IP、子系统和SoC的各种验证方法

处理器/DSP

描述

我们需要越来越复杂的芯片和SoC,用于所有使用人工智能等最新技术的新应用。例如,包含118亿个晶体管的苹果的5nm SoC A14具有6核CPU,4核GPU和16核NPU引擎,每秒能够进行11万亿次操作;而AWS 7nm 64位Graviton2定制处理器包含了更多的300亿个晶体管。设计如此复杂的芯片需要一个标准且经过验证的验证流程,该流程涉及使用各种验证方法和技术在各个级别进行广泛的验证,从IP到子系统再到SoC。

在本文中,让我向您介绍用于验证IP、子系统和SoC的各种验证方法,并解释为什么我们需要像PSS这样的新方法/标准。

对于处理 SoC 验证流程的验证工程师来说,了解如何使用 SoC 构建电子系统至关重要,无论是在 IP 级别进行白盒验证、在子系统级别进行灰盒验证,还是在 SoC 级别进行黑盒验证。

如何使用 SoC 构建电子系统?

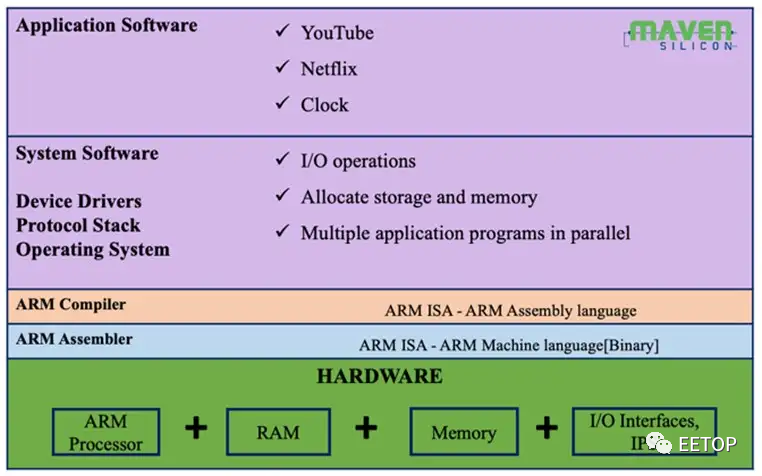

任何芯片、简单的嵌入式微控制器或复杂的片上系统 [SoC] 都将具有一个或多个处理器。图1显示了一个复杂的电子系统,该系统由智能手机等电子设备所需的硬件和软件组成。

图1:电子系统和片上系统

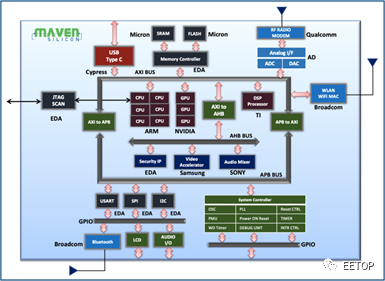

硬件由复杂的SoC组成,该SoC包含设备所需的几乎所有组件。就智能手机而言,我们集成了所有称为IP[知识产权]的硬件组件,如CPU、GPU、DSP、应用处理器、接口IP 如USB,UART,SPI,I2C,GPIO,以及系统控制器、内存与控制器、蓝牙和WiFi等,并由此创建出SoC。

该件由应用软件和系统软件组成。应用软件提供用户界面,系统软件提供接口,使应用软件处理硬件。在智能手机的情况下,应用软件可以是YouTube,Netflix,GoogleMap等移动应用程序,系统软件可以是操作系统[OS],如ios或Android。系统软件提供固件和协议栈等所有内容,以及应用软件与硬件接口所需的操作系统。操作系统并行管理多个应用程序线程、内存分配和 I/O 操作,作为系统软件的核心组件。

接下来解释一下整个系统是如何工作的,就像智能手机一样。例如,当你调用智能手机上的计算器等应用时,操作系统会将可执行二进制文件从存储内存加载到RAM中。然后,它立即将其起始地址加载到其处理器的程序计数器[PC]中。处理器 [ARM/x86/RISC-V] 执行加载到 PC [RAM 地址] 所指向的 RAM/缓存中的二进制文件。这个预编译的二进制文件只不过是处理器的机器语言,因此处理器根据其指令[ADD/SUB/MULT/LOAD]执行应用程序并计算结果。

使用处理器了解SoC设计过程可以帮助验证工程师在系统级处理任何复杂的子系统/芯片验证。作为SoC验证过程的一部分,验证工程师可能需要处理各种事情,例如系统建模的虚拟原型设计,IP,子系统和SoC功能验证,硬件 - 软件协同验证,仿真,ASIC原型设计,硅后验证等。因此,它需要对硬件和软件有凝聚力和完整的了解,才能作为验证专家独立工作,有时还需要与软件团队密切合作,以处理软件,RTOS /固件/堆栈,以进行芯片/系统级验证。

现在让我们探讨各种验证方法。

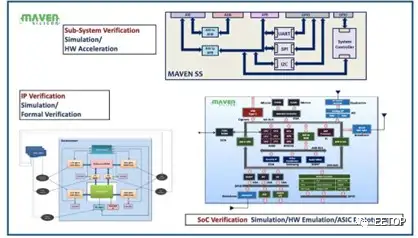

IP验证

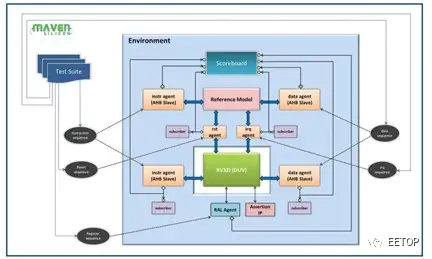

IP 是任何 SoC 的基本构建块。因此,IP验证需要详尽的白盒验证,这需要形式验证和随机模拟等方法,特别是对于处理器IP,因为一切都是由它们作为任何SoC的核心组件启动和驱动的。图 2 显示了我们如何通过基于 SystemVerilog 的 UVM TB 的详尽随机模拟来验证处理器 IP。所有处理器指令都可以使用各种随机值进行模拟,从而生成功能、断言和代码覆盖率。我们使用覆盖范围来衡量验证的进度和质量,然后进行最终的验证签核。IP 级验证要求在 HVL 编程、正式和动态 ABV、仿真调试以及使用 VIP 和 EDA 工具方面具备良好的专业知识。

图2 RISC-V 紫外光验证环境

ABV- 基于断言的验证,VIP – 验证 IP

UVM-通用验证方法 UVC-UVM 验证组件

BFM总线功能模型VIP验证IP RAL寄存器抽象层 子系统验证

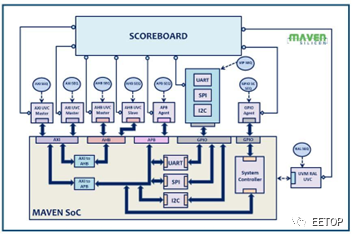

子系统主要由预验证的IP和一些新建的IP组成,例如特定于芯片的网桥和系统控制器。图 3 显示了我们如何从子系统构建 SoC,该子系统使用 AMBA 等片上总线集成了所有必要的接口 IP、网桥和系统控制器。在这种情况下,我们更喜欢基于模拟的灰盒验证,特别是使用验证IP的随机模拟。所有VIP,如AXI,AHB,APB,GPIO,UART,SPI和I2C UVC [UVM验证组件]都将配置并与各自的接口连接。如图 3 所示,我们创建了其他 TB 组件,如参考模型、记分板和 UVM RAL,以使验证环境自检。我们在顶层执行各种VIP UVM序列,验证数据流,并测量总线的性能。

图3 子系统UVM验证环境

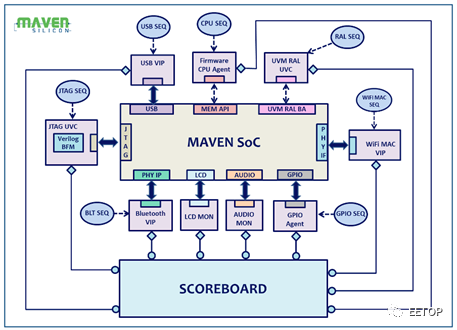

SoC芯片验证

SoC主要由预先验证的第三方IP和一些内部IP组成。通常,我们更喜欢使用硬件仿真或模拟(simulation/emulation)技术进行黑盒验证,以进行SoC级验证。例如,您可能会遇到复杂的 SoC 验证环境,如图 4 所示。SoC测试平台[TB]将具有各种测试平台组件,如标准UVM验证IP[USB /蓝牙/WiFi和标准接口],带有UVM包装器的传统HDL TB组件[JTAG Agent],自定义UVM代理[固件代理],以及一些显示器,以及记分牌和SystemC / C /C++功能模型。在这种情况下,您将不得不在芯片级别处理固件和UVM序列。作为验证工程师,您需要知道如何使用标准 VIP、传统 HDL BVM 和固件代码实现这种混合验证环境,更重要的是,了解如何使用 EDA 工具自动执行simulation/emulation。

图 4:SoC 验证环境

UVM-通用验证方法 UVC-UVM 验证组件

BFM总线功能模型VIP验证IP RAL寄存器抽象层

让我解释一下它是如何工作的。例如,如果SoC使用ARM处理器,通常我们将ARM RTL [加密网表/RTL]替换为其称为DSM [设计仿真模型]的功能模型,该模型可以使用固件[用C编写]作为激励来启动任何操作并驱动所有其他外设[RTL IP]。因此,SoC 验证人员编写 UVM 序列,通过固件测试用例生成各种定向场景,并验证 SoC 功能。在仿真过程中,固件C源代码被编译为目标代码[ARM机器语言二进制文件],该目标代码将加载到片上RAM中。ARM 处理器模型 [DSM] 从内存中读取目标代码,并通过配置和驱动所有 RTL 外设模块 [Verilog/VHDL] 来启动操作。它适用于模拟和仿真(simulation/emulation)。如果 SoC 非常复杂,则首选硬件仿真以加速验证过程并实现更快的验证sign-off。

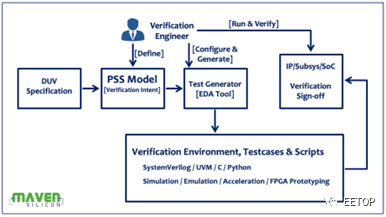

为什么选择 PSS?

图 5:IP、子系统和 SoC 验证方法

PSS 定义:可移植测试和激励标准定义了一个规范,用于创建激励和测试场景的单一表示形式,可供不同配置下不同集成级别的各种用户使用,从而能够生成在各种执行平台上运行的场景的不同实现,包括但不限于, 仿真、仿真、FPGA 原型设计和后硅。使用此标准,用户可以一次指定一组行为,从中可以派生多个实现。

图6:PSS流程

如图6所示,使用PSS,我们可以定义测试场景,并使用任何验证技术在任何级别的IP/子系统/SoC上执行它们。例如,我们可以在 PSS 中定义 IP 的测试场景。在IP级验证中,我们可以使用EDA从其PSS规范中生成断言以进行形式验证,如果需要,我们可以从相同的PSS规范生成UVM测试用例,用于SoC级别的模拟或仿真。我们不需要手动重写 IP/子系统级测试用例,即可在 SoC 级别迁移和重用它们。PSS规范对于各种技术都保持不变。根据我们的选择,如正式/模拟/仿真,EDA工具可以从任何语言或方法(如C / C++ / Verilog / SystemVerilog / UVM)的PSS形态生成测试用例。

形式验证和PSS等方法正在不断发展,同时EDA供应商也在使用ML等技术自动生成测试和验证sign-off。因此,在不久的将来,该行业需要才华横溢且技术娴熟的验证工程师,他们可以与芯片架构师合作,通过“按构造校正”方法推动首次硅成功的验证过程,而不仅仅是处理黑盒验证的传统验证人员,该验证人员主要涉及编写测试用例和管理回归测试。您是否对芯片验证感兴趣,并为这项重要工作做好了准备?

编辑:黄飞

-

硬件验证方法简明介绍2022-11-26 10717

-

适用于NFC和验证的子系统设计2022-09-22 2109

-

仿真和模拟用于IC验证的方法2022-07-05 4142

-

基于VHDL语言的IP核验证2021-09-01 2692

-

探究始于验证体系结构的SoC IP方法2021-04-28 1532

-

【华为海思成都】招聘数字IC设计/验证工程师2020-02-29 2652

-

SoC验证平台的FPGA综合怎么实现?2019-10-11 1674

-

利用FPGA软硬件协同系统验证SoC系统的过程和方法2017-11-17 5372

-

浅谈SOC系统知识2016-08-05 7498

-

SoC多语言协同验证平台技术研究2015-12-31 1035

-

Incisive 12.2版本融入Cadence验证IP,SoC验证效率提高50%2013-01-27 1985

-

基于OVM验证平台的IP芯片验证2012-06-20 3357

-

SoC验证环境搭建方法的研究2009-12-14 588

-

在SoC设计中采用ESL设计和验证方法2009-11-30 769

全部0条评论

快来发表一下你的评论吧 !