基于TL6678F-EasyEVM开发板的高速AD采集处理案例

模拟技术

描述

TI C6678 + Xilinx Kintex-7作为DSP+FPGA架构的经典组合,凭借FPGA的高速采集和DSP的高性能算法处理完美结合的特性,一直被广泛应用于视频追踪、图像处理、软件无线电、雷达探测、光电探测、水下探测以及定位导航等嵌入式应用场景。

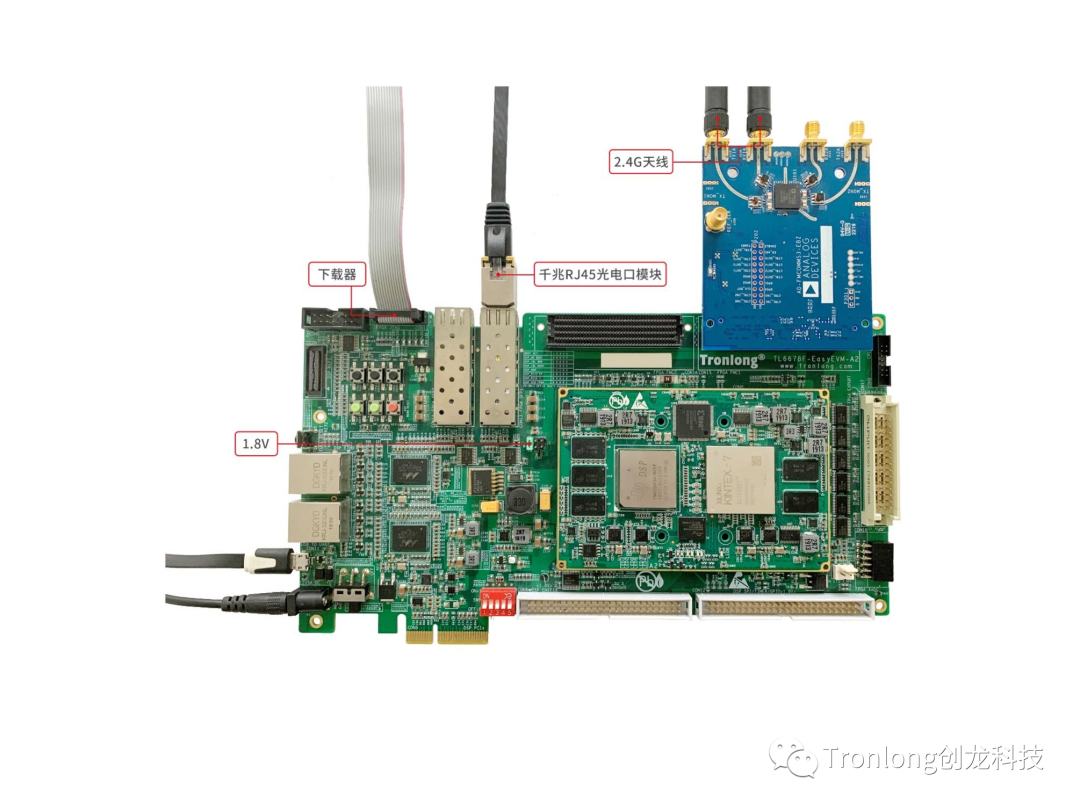

本文基于创龙科技的TI C6678 + Xilinx Kintex-7设计的TL6678F-EasyEVM开发板,给大家介绍高速AD采集处理案例,包含CameraLink/SDI/PAL/HDMI视频采集处理开发案例、AD9361/AD9613高速AD采集处理开发案例。

TL6678F-EasyEVM开发板由核心板与底板组成。核心板内部DSP与FPGA通过SRIO、EMIF16、I2C通信总线连接。

评估板引出双路FMC、双路SFP+光口、双路千兆网口、PCIe等高速通信接口,方便用户快速进行产品方案评估与技术预研。

案例一

AD9361软件无线电案例

1 案例说明

本案例基于ADI AD9361模块AD-FMCOMMS3-EBZ和创龙科技TL6678F-EasyEVM评估板搭建AD9361 RF(Radio Frequency)收发测试平台,实现QPSK(Quadrature Phase Shift Keying)数字调制。AD-FMCOMMS3-EBZ模块开发官方参考链接:

https://wiki.analog.com/resources/eval/user-guides/ad-fmcomms3-ebz

2 案例测试

图 2

图 3 硬件连接

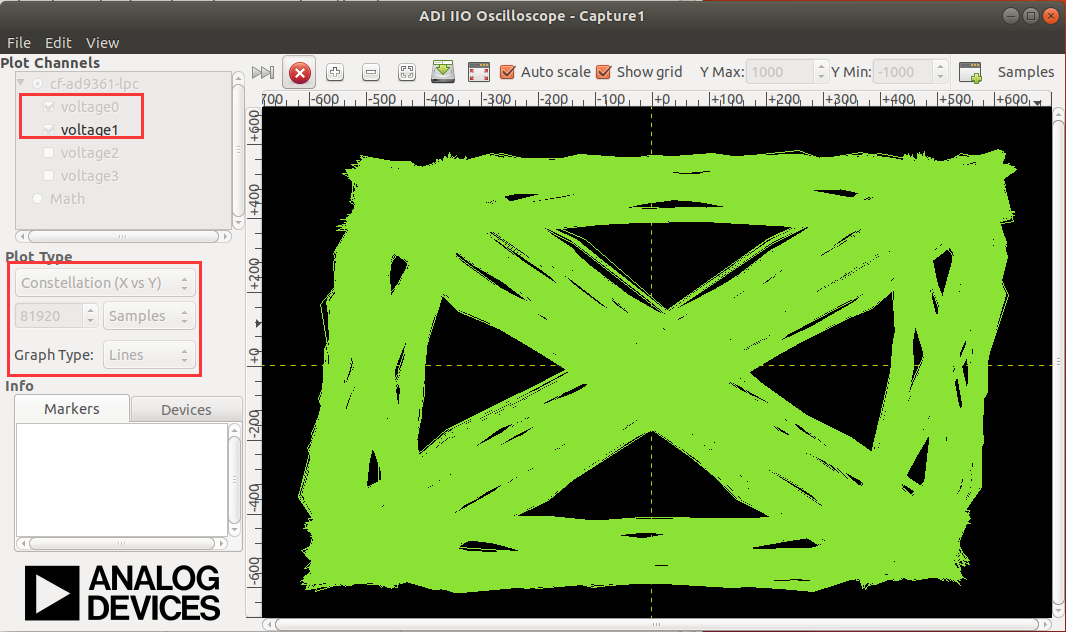

图 4 线状形式星座图

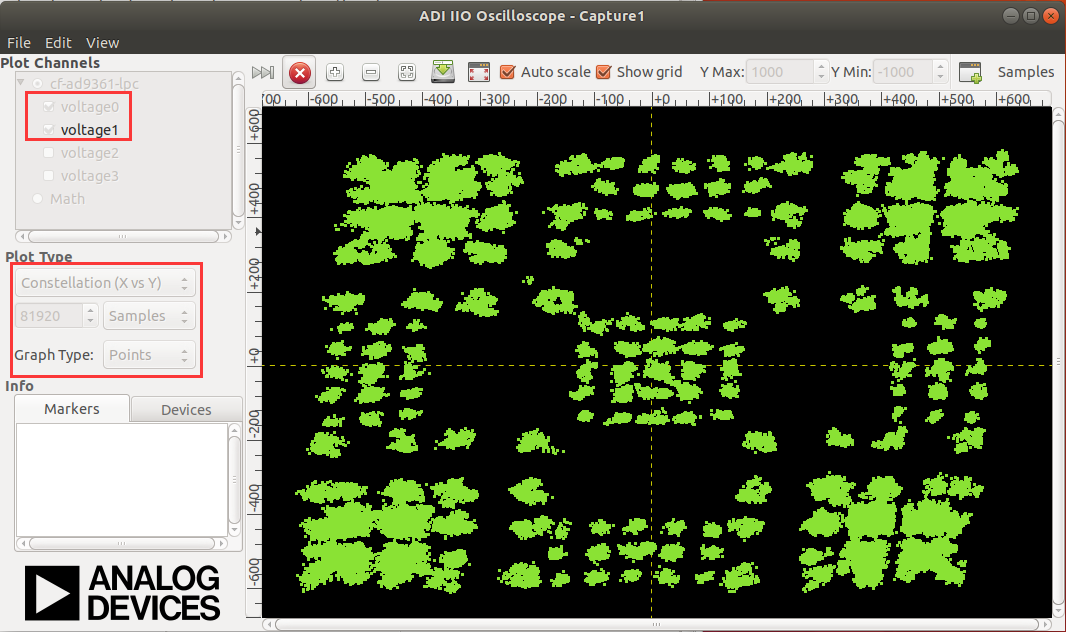

图 5 点状形式星座图

案例二

AD9613高速AD采集处理案例

1 案例说明

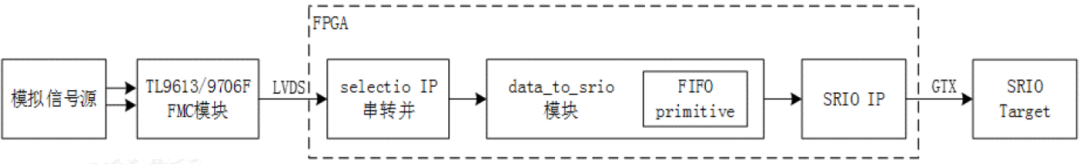

案例功能:FPGA端通过AD9613以250MSPS速率采集AD数据后,将数据通过SRIO总线传输至DSP端进行FFT算法处理。

FPGA端作为SRIO Initiator,DSP端作为SRIO Target。FPGA端通过SRIO SWRITE方式将数据传输至DSP端的0x0C3F0000地址空间,单次传输数据量为16KByte,每传输16KByte数据就发送一个DOORBELL信息。DSP端响应DOORBELL信息后,使用C66xx_0~C66xx_7进行FFT算法处理。

AD9613采样双通道12bit数据,由于传输时将12bit数据按照16bit进行发送,因此实际发送数据量为16bit x 2 x 250MSPS = 8Gbps。

图 6 FPGA端程序功能框图

2 案例测试

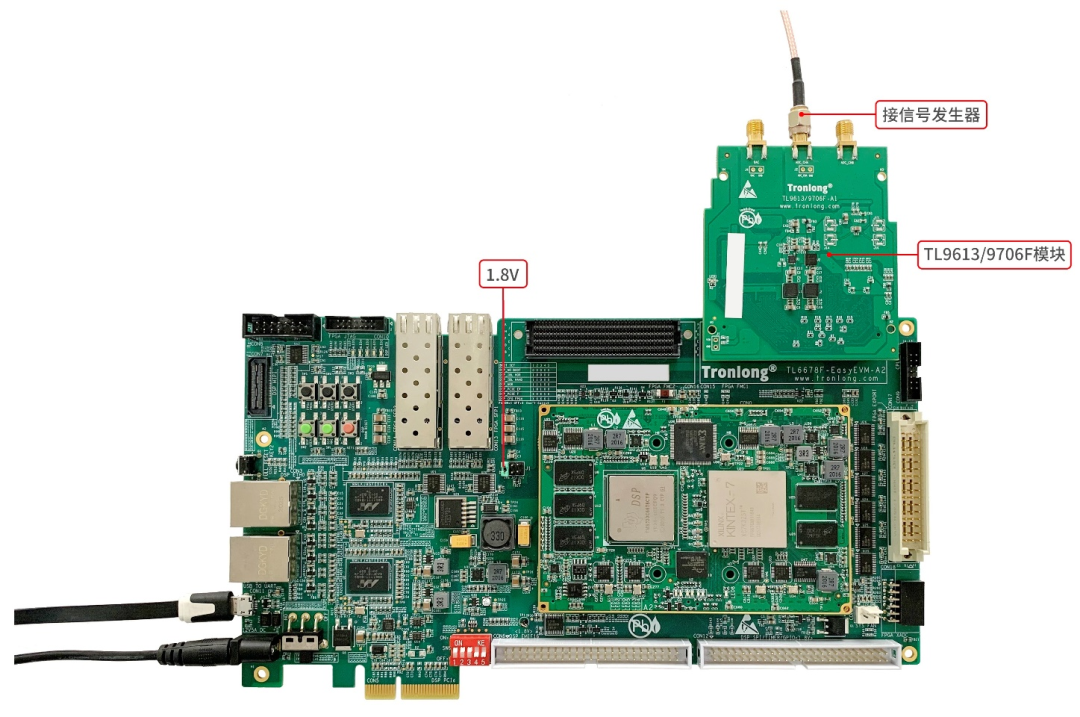

图 7

图 8 硬件连接

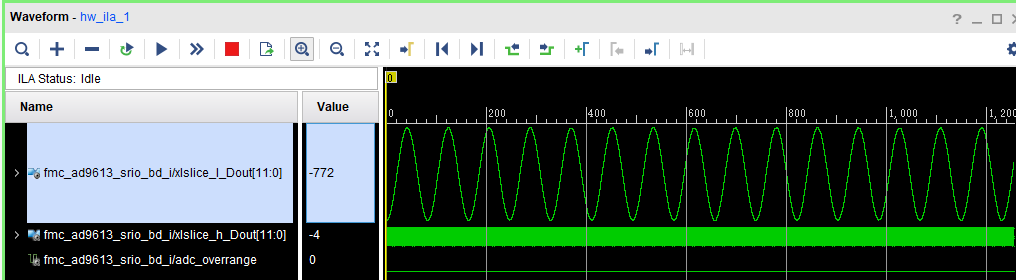

图 9 FPGA端ILA触发抓取的AD数据波形

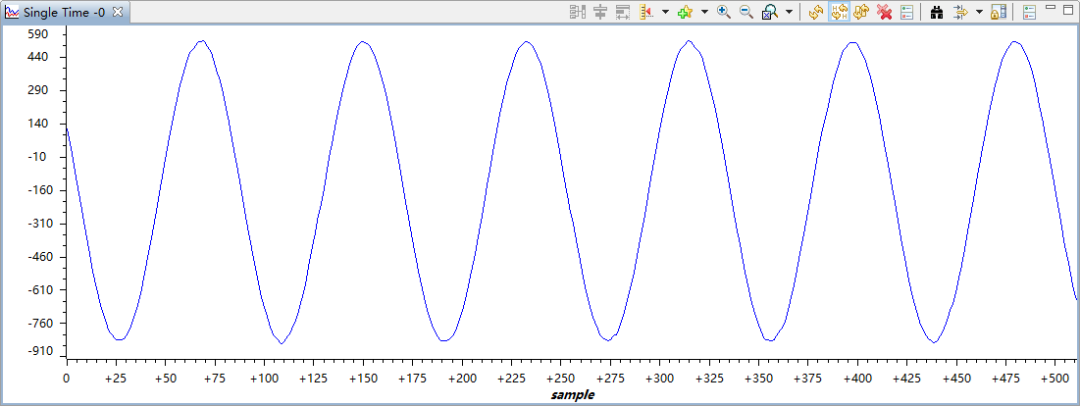

图 10 CCS原始信号时域波形

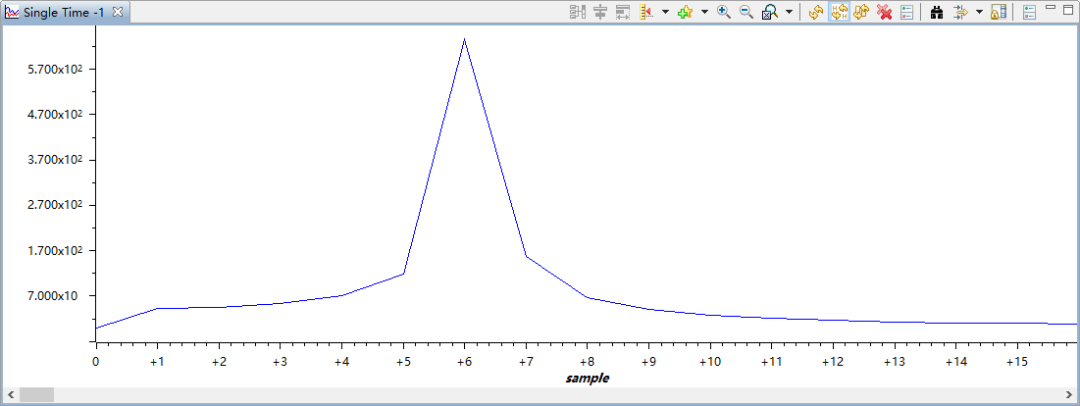

图 11 经FFT处理后的信号频域(振幅)波形

案例三

CameraLink视频采集处理

1 案例说明

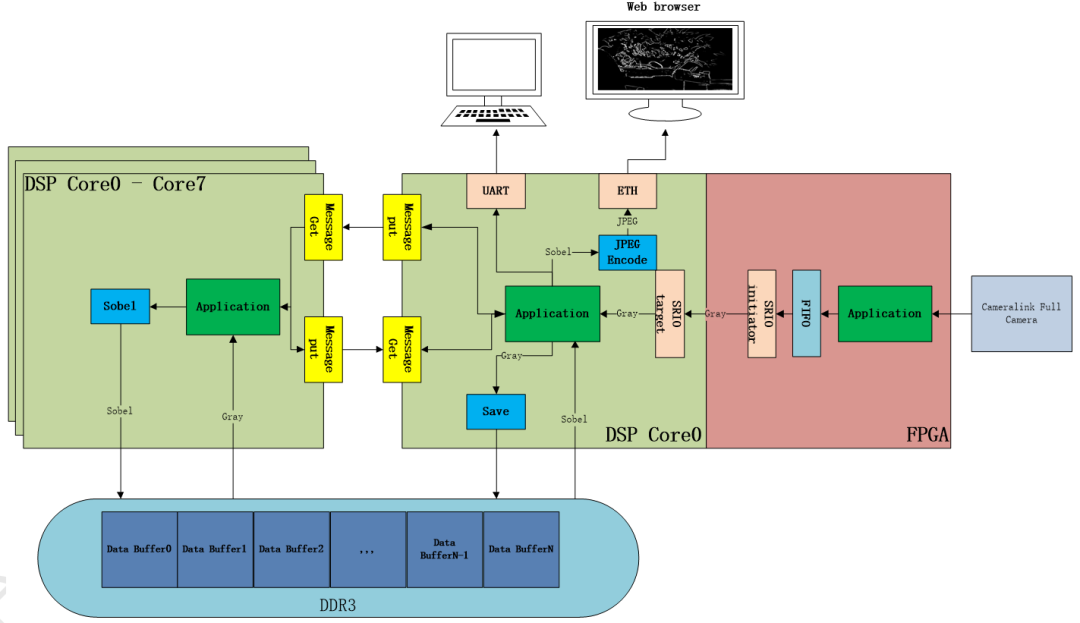

FPGA端通过FMC视频模块TLCameraLinkF的CameraLink接口进行分辨率为2560 x 2048的视频采集,再经过SRIO总线将视频数据传输至DSP端进行Sobel(边缘检测)算法处理,然后将经处理后的图像通过网页进行显示。

FPGA端作为SRIO Initiator,DSP端作为SRIO Target。FPGA端通过SRIO SWRITE和乒乓方式,将数据传输至DSP端的0x90000000和0x90500000的DDR地址空间。

案例使用北京微视的黑白CameraLink相机RS-A5241-CM107-S00,分辨率为2560 x 2048,帧率为107,灰度输出,每个像素8bit,则数据量为2560 x 2048 x 107 x 8 = 4487905280 ≈ 4.5Gbps。案例使用SRIO的两个Lanes,每个Lane传输速率为5Gbps,总数据有效带宽为5Gbps x 2 x 80% = 8Gbps。

图 12 案例功能框图

图 13 FPGA端程序功能框图

2 案例测试

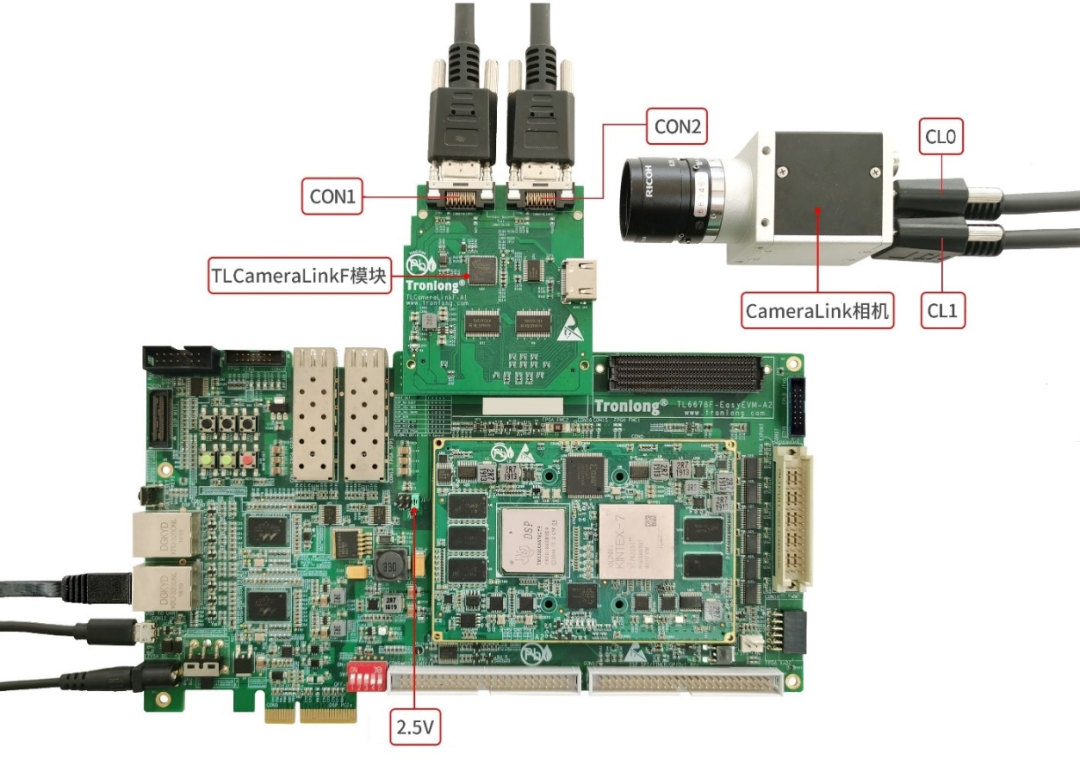

图 14 CameraLink模块

图 15 硬件连接

案例四

SDI视频采集处理

1 案例功能

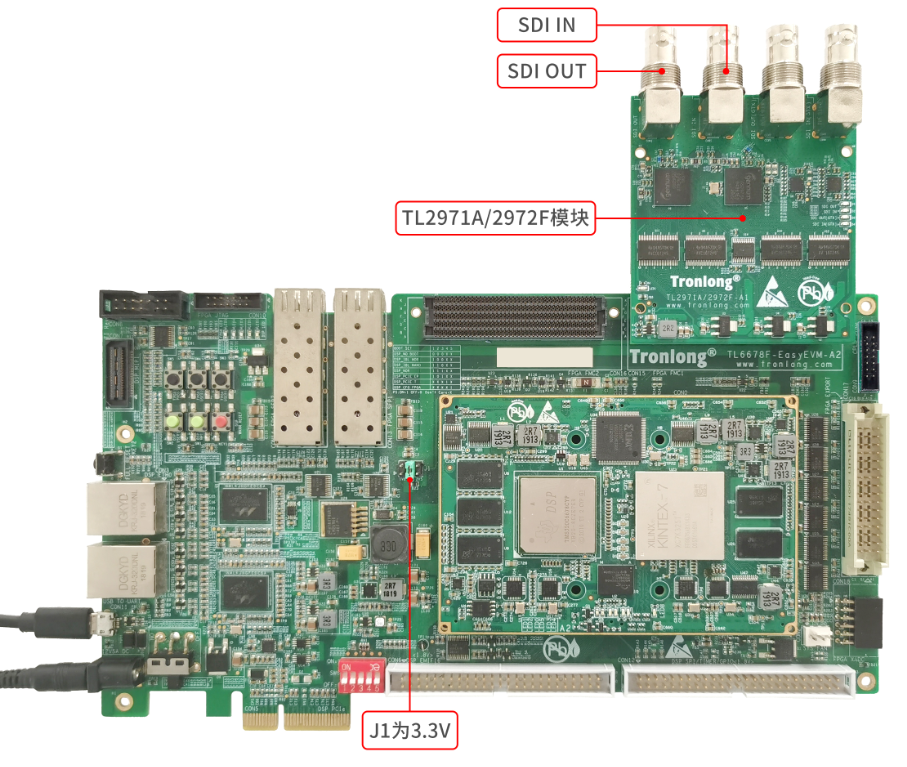

案例功能:评估板通过FMC视频模块TL2971A/2972F的SDI IN接口进行1080P60视频采集,并通过TL2971A/2972F模块的SDI OUT接口将采集到的视频进行输出。

2 操作说明

请将创龙科技的TL2971A/2972F模块连接至评估板FMC1接口,评估板J1跳线帽选择3.3V档位,以配置FMC IO的BANK电压为3.3V。

准备一台拥有HDMI OUT接口的PC机(例如笔记本),通过HDMI数据线将PC机HDMI OUT接口连接至HDMI转SDI模块(厂家:玩视,型号:3G HDMI TO SDI Audio)INPUT接口,PC机HDMI OUT接口用作图像输出。通过SDI数据线将TL2971A/2972F模块的SDI IN接口连接至HDMI转SDI模块的OUTPUT接口。

通过SDI数据线将TL2971A/2972F模块的SDI OUT接口连接至SDI转HDMI模块(厂家:玩视,型号:3G SDI TO HDMI Audio)的INPUT接口,再通过HDMI数据线将一台HDMI显示屏连接至SDI转HDMI模块的OUTPUT接口,HDMI显示屏用作图像显示。

图17

图 18

图 19

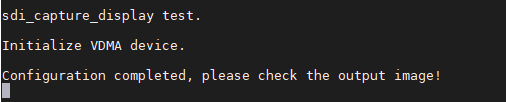

请运行程序,即可看到串口调试终端打印如下信息,然后在PC机的显卡设置(或图形属性)中,按照下图设置HDMI分辨率为1920 x 1080、刷新率为60pHz。

图 20

图 21

此时,HDMI显示屏将显示PC机HDMI OUT接口输出的图像。

图 22

图 23

案例五

HDMI视频采集处理

1 案例功能

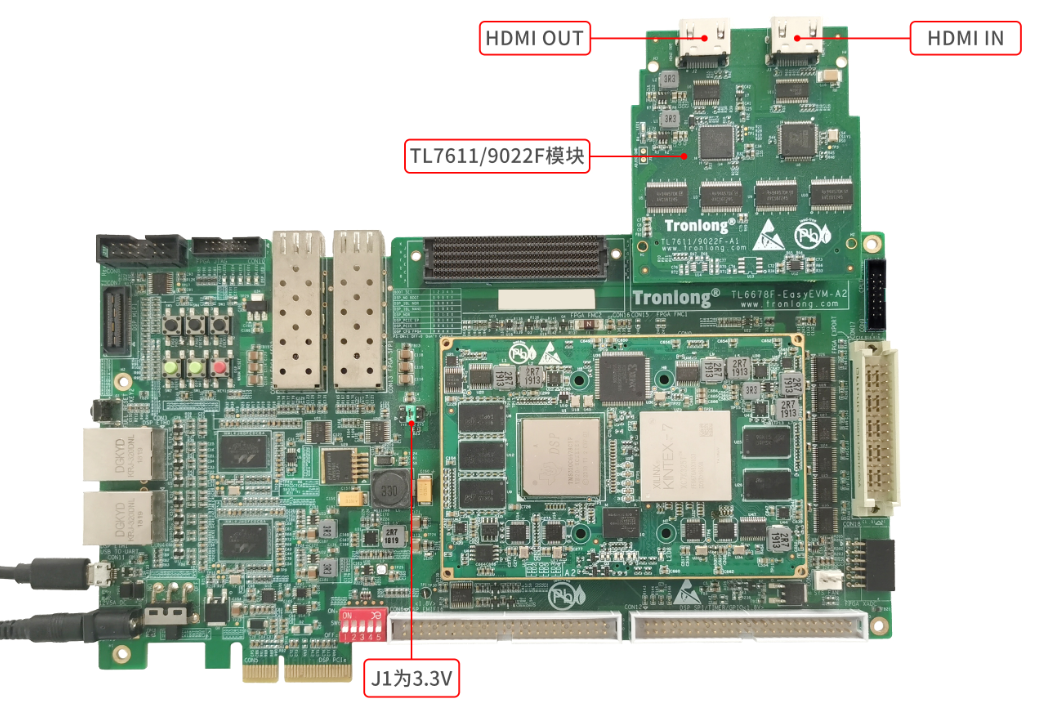

案例功能:评估板通过FMC视频模块TL7611/9022F的HDMI IN接口进行1080P60视频采集,并通过TL7611/9022F模块的HDMI OUT接口将采集到的视频进行输出。

2 操作说明

请将创龙科技的TL7611/9022F模块连接至评估板FMC1接口,评估板J1跳线帽选择3.3V档位,以配置FMC IO的BANK电压为3.3V。

准备一台拥有HDMI OUT接口的PC机(例如笔记本),通过HMDI数据线将PC机HDMI OUT接口连接至TL7611/9022F模块的HDMI IN接口,PC机HDMI OUT接口用作图像输出。通过HMDI数据线将一台HDMI显示屏连接至TL7611/9022F模块的HDMI OUT接口,HDMI显示屏用作图像显示。

图 24

图 25

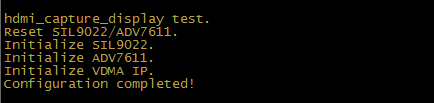

请运行程序,即可看到串口调试终端打印如下信息,然后在PC机的显卡设置(或图形属性)中,按照下图设置HDMI分辨率为1920 x 1080、刷新率为60pHz。

图 26

图 27

此时,HDMI显示屏将显示PC机HDMI OUT接口输出的图像。

图 28

图 29

案例六

PAL视频采集处理

1 案例功能

案例功能:评估板通过FMC视频模块TL2867F的BNC接口进行4路PAL制式D1模拟视频采集,并进行4路视频拼接,再通过TL2867F模块的HDMI接口将拼接视频进行输出。

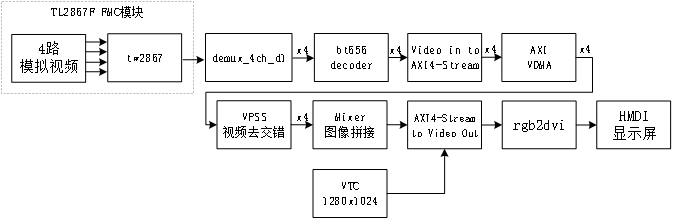

图 30 程序功能框图

2 操作说明

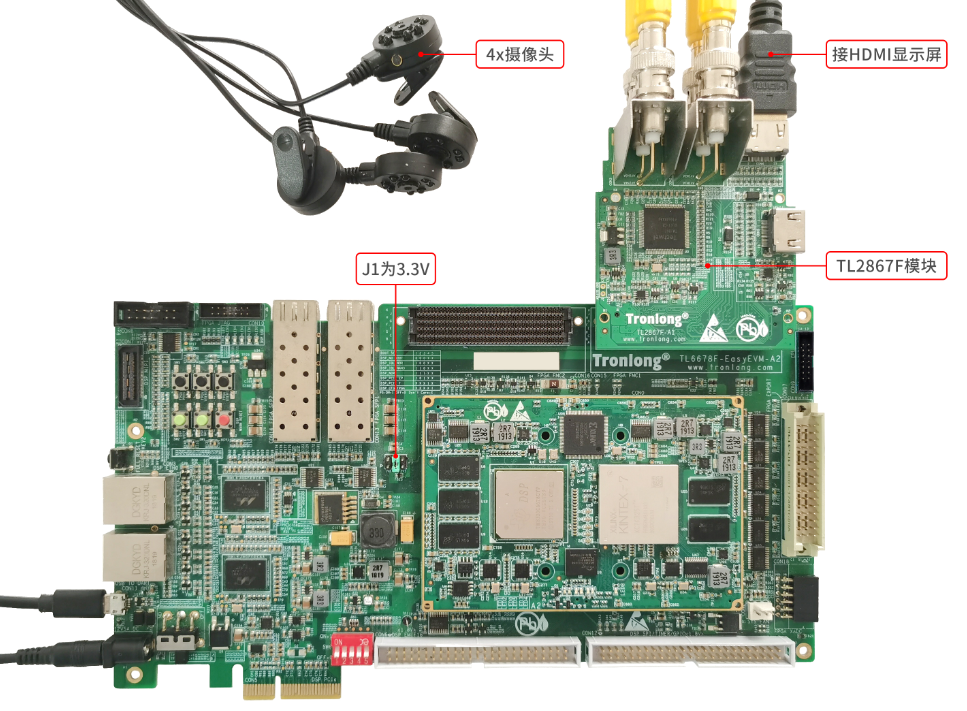

请将创龙科技的TL2867F模块连接至评估板FMC1接口,评估板J1跳线帽选择3.3V档位,以配置FMC IO的BANK电压为3.3V。

请将4个红外夜视摄像头连接至TL2867F模块的BNC接口,并通过HMDI数据线将一台HDMI显示屏连接至TL2867F模块的HDMI1接口,HDMI显示屏用作图像显示。

图31

图 32

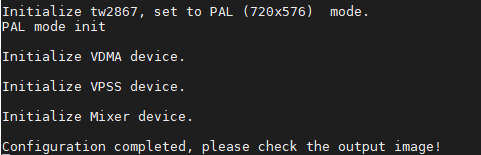

请运行程序,即可看到串口调试终端打印如下信息,HDMI显示屏将显示4路图像。

图 33

编辑:黄飞

-

TL138/1808/6748-EasyEVM 开发板硬件说明书2023-10-09 865

-

创龙 TL6678ZH-EVM开发板案例解析2022-12-06 2403

-

【源码集限时公开】C6678+Kintex-7视频/高速AD开发案例大集合(总计6个)!2022-08-29 2031

-

TL138/1808/6748F-EasyEVM开发板简述2021-12-30 1499

-

TL665xF-EasyEVM开发板介绍2021-12-28 1630

-

源码免费下载!C6678+K7视频采集处理方案,这里全都有2021-11-26 13470

-

你想要的C6678+K7视频采集处理方案,都在这里了!内含案例源码+资料下载!2021-07-09 3865

-

基于DSP+FPGA实现的TL6678F-EasyEVM开发板的介绍2020-02-12 4727

-

免费供应TMS320C6678/TMS320C665x+Kintex-7/Artix-7、TMS320C6748+Spartan-6开发板试用2019-07-16 1618

-

创龙TMS320C6678开发板免费试用2018-10-15 0

-

广州创龙基于TI TMS320C6678芯片,研发的一款DSP+FPGA高速大数据采集开发板2018-03-06 6974

-

转手一块创龙TL6678-EasyEVM 八核DSP2017-03-06 3231

-

创龙TI KeyStone C66x八核 TMS320C6678 DSP开发板2016-08-14 3876

-

TL437x-EasyEVM开发板硬件说明书2015-12-24 832

全部0条评论

快来发表一下你的评论吧 !