QuarusⅡ工具时序分析结果

电子说

描述

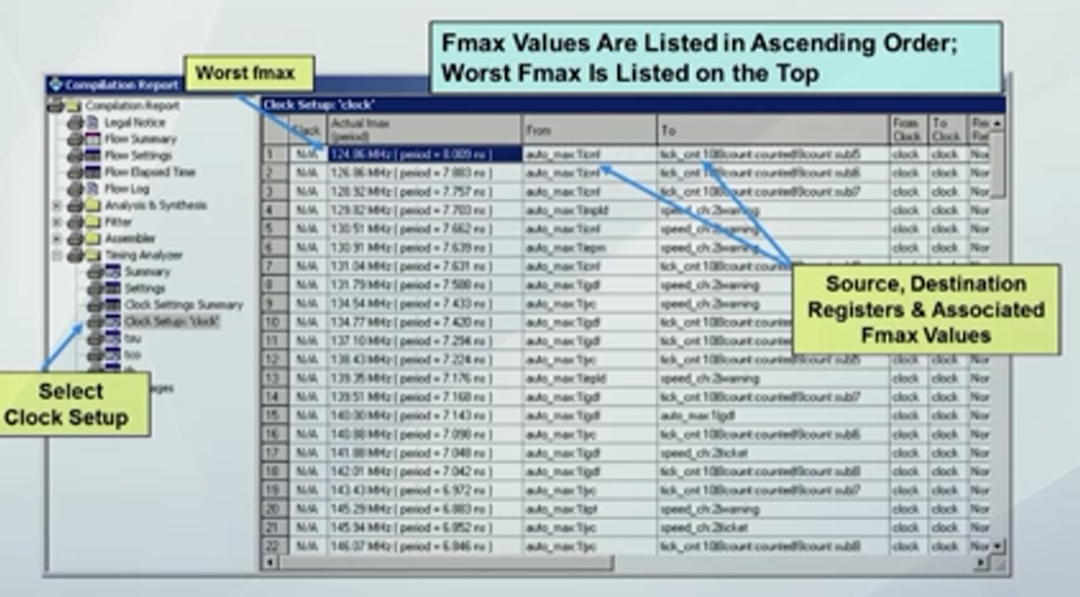

图一是Quartus Ⅱ工具关于时序分析建立时间分析报告结果(个人理解:该报告可以作为时钟周期报告)。Quartus Ⅱ工具可以详细给出每一条路径的分析结果,路径信息按照延时由大到小的顺序排列,因为延时最长的情况通常被认定为最坏情况,所以需要关注延时长的情况。

图一的第一列展示的是延时的时间长度,最长的关键路径延时为8ns(1ns=10-9s),对该时间取倒数,可以得出芯片的工作频率在125MHz左右。

除此之外,图一还展示了延时路径的一些信息,包括源节点(可以理解为数据发送端)信息、目标节点(可以理解为数据接收端)信息等。目标节点从顶层到底层(含个人理解:门级信息,具体到某个节点的某个引脚)的信息均列出,设计人员可以通过以上信息分析出该路径在设计中的实际位置,方便对电路设计进行优化。

图一,图片来源:学堂在线《IC设计与方法》

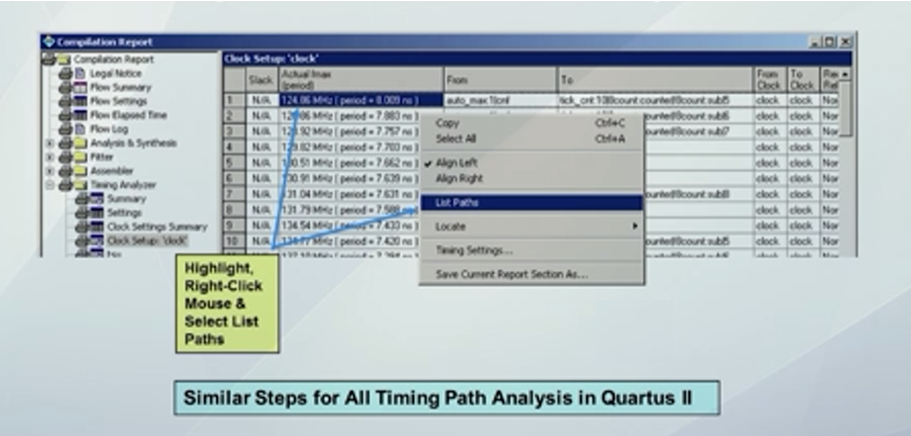

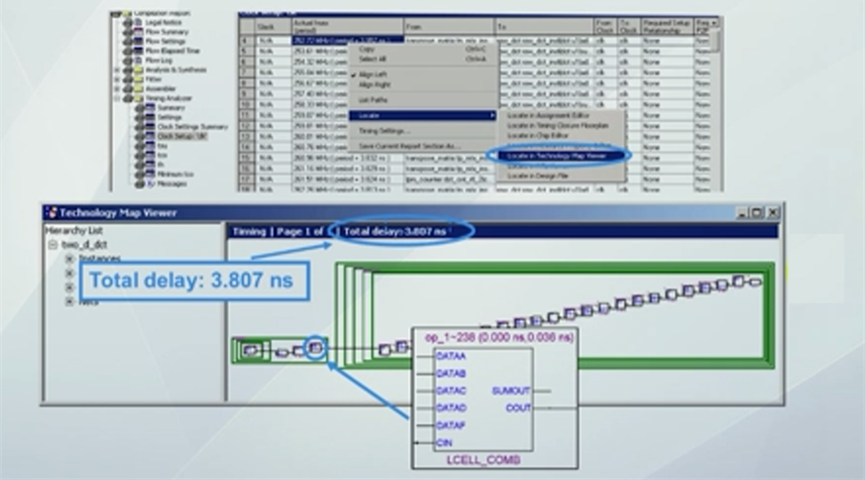

设计人员可以通过图二的操作列出某一路径的详细信息,图二的操作可以展示延时最长路径的详细信息。

图二,图片来源:学堂在线《IC设计与方法》

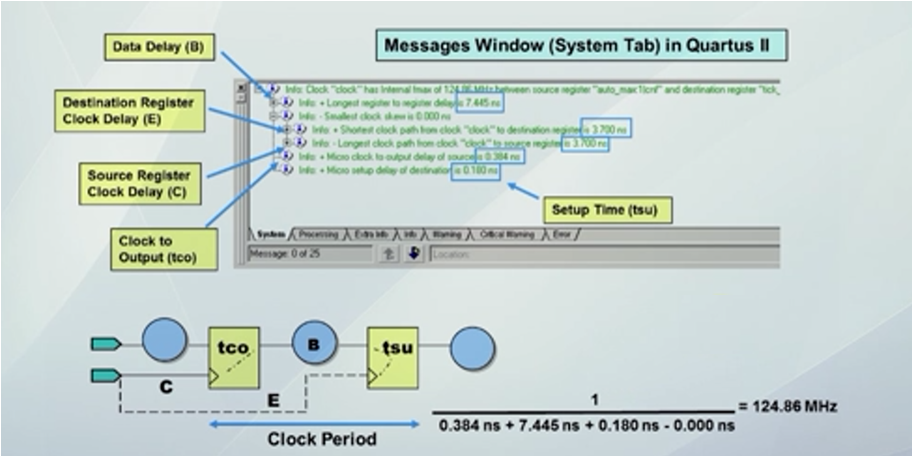

经过图二的操作,Quartus Ⅱ工具会显示出图三界面,图三列出了延时最长路径的详细信息。

图三左下角是时序分析的模型图,设计人员可以对照模型图在图三界面中找到C(时钟信号传递到源触发器的延时)、E(时钟信号传递到目标触发器的延时)、B(从源触发器到目标触发器所经过的组合逻辑电路的延时)、tco(源触发器延时)、tsu的信息(目标触发器延时)。

图三界面中,一共有七行信息。第二行列出了最长的B的延时为7.445ns。第四行列出了最短的E的延时为3.7ns,第五行列出了最长的C的延时为3.7ns,可以发现C=E,这是因为该芯片面积较小,所以C和E相等。第六行列出了tco为0.384ns,第七行列出tsu为0.18ns。

根据时钟周期的公式:

time period=tco+B+tsu-(E-C)

可以计算得出time period(时钟周期)等于8.009ns。工作频率为time period的倒数,其值约为124.86MHz。

图三,图片来源:学堂在线《IC设计与方法》

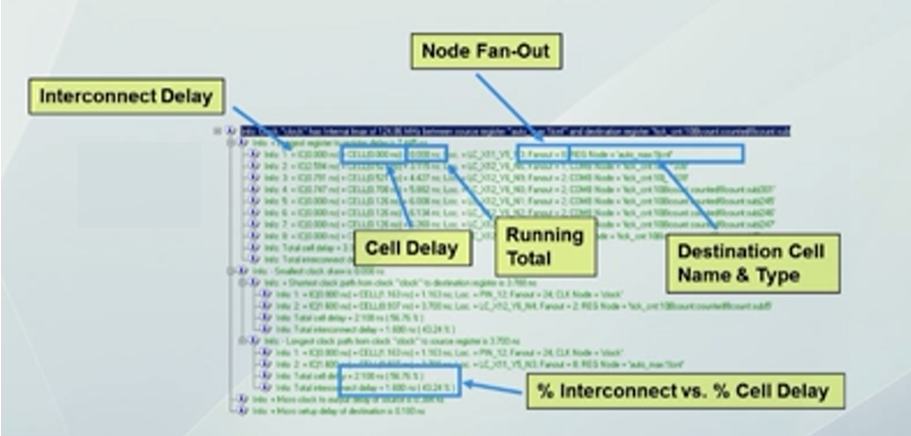

Quartus Ⅱ工具可以将图三中更详细的信息展示,如图四上侧,列出B路径的详细信息。图四上侧展示了互连线延时和单元(个人理解:一个门器件)的延时、元器件的扇出系数(扇出系数越大,延时越大)、节点相关信息。

图四下侧展示了总结性的报告,包括总互连线延时、总的单元延时、以及两种延时所占的比例。设计人员可以通过两种延时的比例判断延时过长的原因是因为互连线过长,还是因为逻辑过复杂。

图四,图片来源:学堂在线《IC设计与方法》

图五下侧的窗口展示了使用Technology Viewer(Quartus Ⅱ工具中一种运用图形展示分析结果的方式)展示最长延时路径。如图五所示,输入D触发器经过十几个单元达到输出D触发器,说明最长延时路径延时过长的原因是电路逻辑过复杂。

设计人员也可以通过Technology Viewer观测某个元器件所使用的信号、元器件的类型、元器件的延时。

图五,图片来源:学堂在线《IC设计与方法》

审核编辑:刘清

-

[求助]静态时序分析与时序仿真?2010-03-03 5021

-

基于Astro工具的ASIC时序分析2012-11-09 3008

-

时序计算和Cadence仿真结果的运用2009-12-21 914

-

时序约束与时序分析 ppt教程2010-05-17 955

-

静态时序分析与逻辑(华为内部培训资料)2010-07-09 1073

-

SOC时序分析中的跳变点2010-09-15 2223

-

融合时序分析和SI的工具2011-07-02 2917

-

调用timequest工具对工程时序进行分析2019-11-28 2835

-

静态时序分析:如何编写有效地时序约束(一)2019-11-22 4319

-

一种可延长静态时序分析仪精度的时序签核工具2019-08-13 4233

-

正点原子FPGA静态时序分析与时序约束教程2020-11-11 2918

-

芯片设计之Quarus 工具部分功能简介2022-08-17 1529

-

怎样分析PLD(可编程器件)逻辑综合结果是否正确呢2022-08-25 2487

-

时序分析工具对比报告2022-09-27 740

全部0条评论

快来发表一下你的评论吧 !