Rambus推出DDR5串行检测集线器和温度传感器

电子说

描述

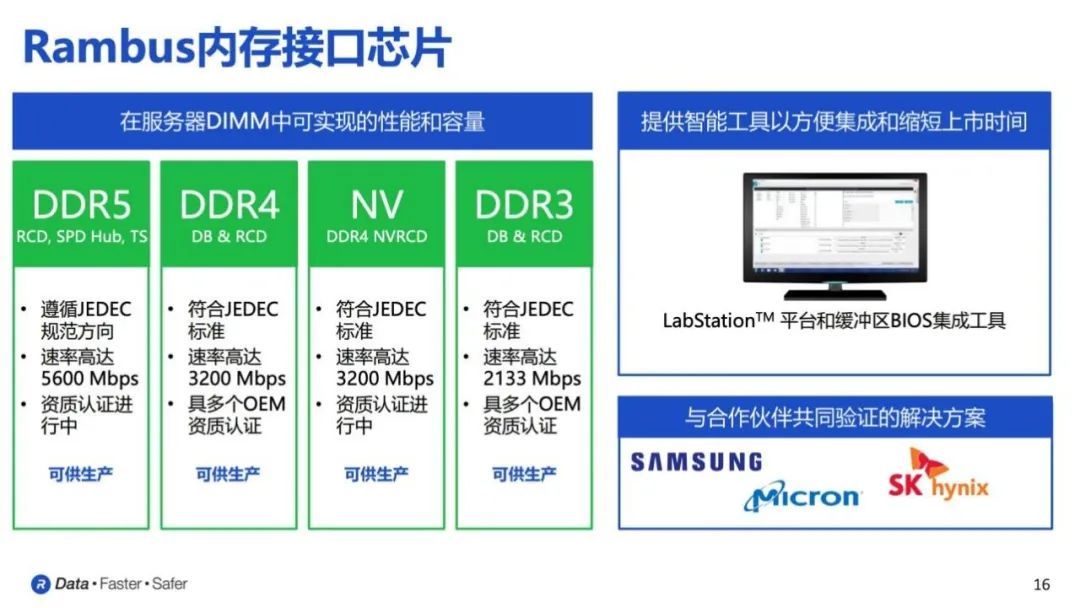

在DDR4出现十年之后,DDR5翩翩来迟。作为十年之久的换代,DDR5的设计上实现了诸多突破:新的通道设计、片内ECC、片上PMIC、更多温度传感器乃至插槽缺口的位移等。新的设计规范和标准,让内存容量、带宽和传输速率得以大幅提升,但同时新的标准使得内存条的设计复杂度增加。

相比DDR4,DDR5的DIMM上所需的和数据传输相关的关键芯片更多,其中包括寄存时钟驱动器(RCD)、数据缓冲器(DB)外,串行检测集线器(SPD Hub);服务器级的内存模组还需要在两端添加温度传感器(TS)。

IDC预计到2023年底, DDR5的出货量将会超过DDR4。面对旺盛的市场需求和DDR5更为复杂的设计要求,在DDR5 RCD和DB芯片发布一年之后,Rambus于近日发布了其DDR5 SPD Hub(SPD5118)和TS产品(TS5110),完善了其DDR5 DIMM芯片组合。这些芯片对于增强系统管理和热控制至关重要,可以帮助实现高带宽和高容量,同时优化总体拥有成本。

/01/

DDR5:诸多关键变化带来更高性能

据Rambus内存互连芯片业务部门产品营销副总裁John Eble介绍,虽然RDIMM和LRDIMM相对于DDR4的设计并没有太多的变化,但是在DDR5模块本身的配置却有着重大的改变。诸多的关键变化帮助DDR5满足了最新的技术要求。

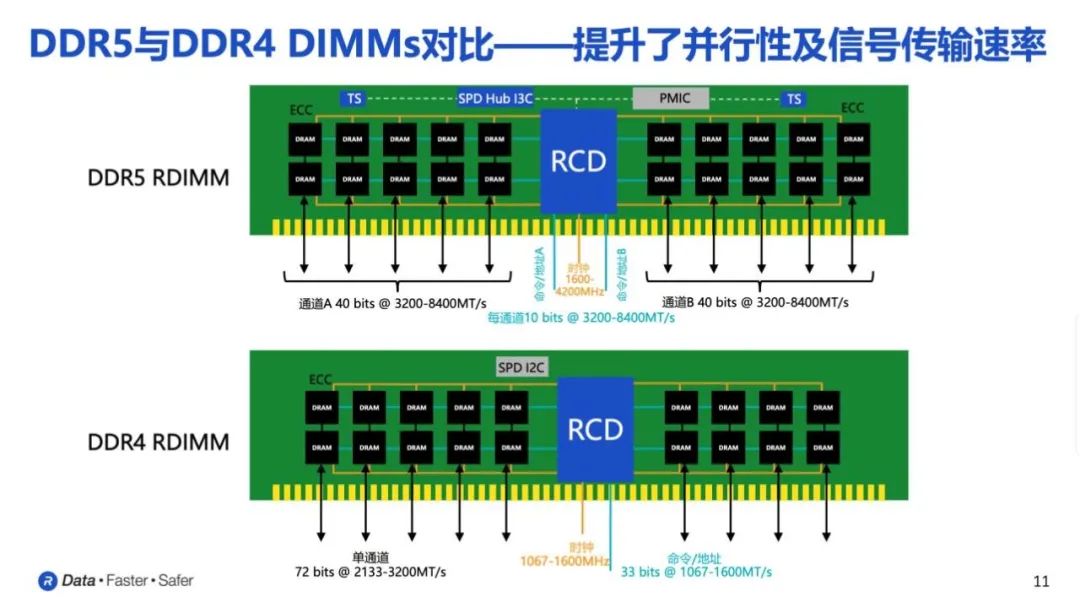

首先是在通道架构方面,DDR4模块采用单一的内存接口数据通道,具备72位总线,其中包含64个数据位和8个ECC位。而DDR5具有两个40位宽的数据通道,每个通道包括32 个数据位和 8 个 ECC 位,以保持相同的ECC保护,并允许存储元数据。每个模块的额外通道不仅满足了访问粒度的要求,而且还增加了内存效率和数据的并发性。

在数据通道的原始速度上,DDR4的最高数据传输速率为每秒3200MT/s,而DDR5的起始速率将达到4800MT/s,其设计的最高数据传输速率将达8400MT/s。

在突发长度方面,DDR4的突发斩波长度为四,突发长度为八。DDR5 的突发斩波和突发长度将扩展到八和十六,以增加突发有效负载。在突发长度为十六 (BL16) 的情况下,允许单个突发访问 64 字节的数据(典型的 CPU 缓存行大小)。

在命令/地址总线和时钟方面,DDR4具有33个特定功能的引脚,运行单一数据速率的时钟。为了在与DDR4相同的模块引脚数下容纳两个独立的命令/地址总线,DDR5的接口必须变得更加高效,因而DDR5为其两个数据通道使用了单个时钟。DDR5为每个命令/地址总线分配了10个引脚,每个总线运行双倍数据速率,以进一步提高效率。

通过上述一系列的优化,DDR5相比DDR DIMM在性能、容量和功耗方面实现了全面超越。除了上述提到的带宽等优势外,DDR5 DIMM还具备更高的相关容量,每颗芯片的最大密度从DDR4的16Gb到DDR5的64Gb。因此对于使用单芯片封装的DIMM来说,每个模块的最大容量将从64GB增加到256GB,更高容量的DIMM还可以通过3D堆叠技术实现。

/02/

DDR5服务器性能优化离不开SPD Hub和TS

服务器市场相比消费市场,对于性能的迫切性更高。可以预期几乎所有的服务器都会逐渐采用DDR5,在接下来的三个月到半年时间,预计也将看到更多支持DDR5的服务器处理器陆续上市。

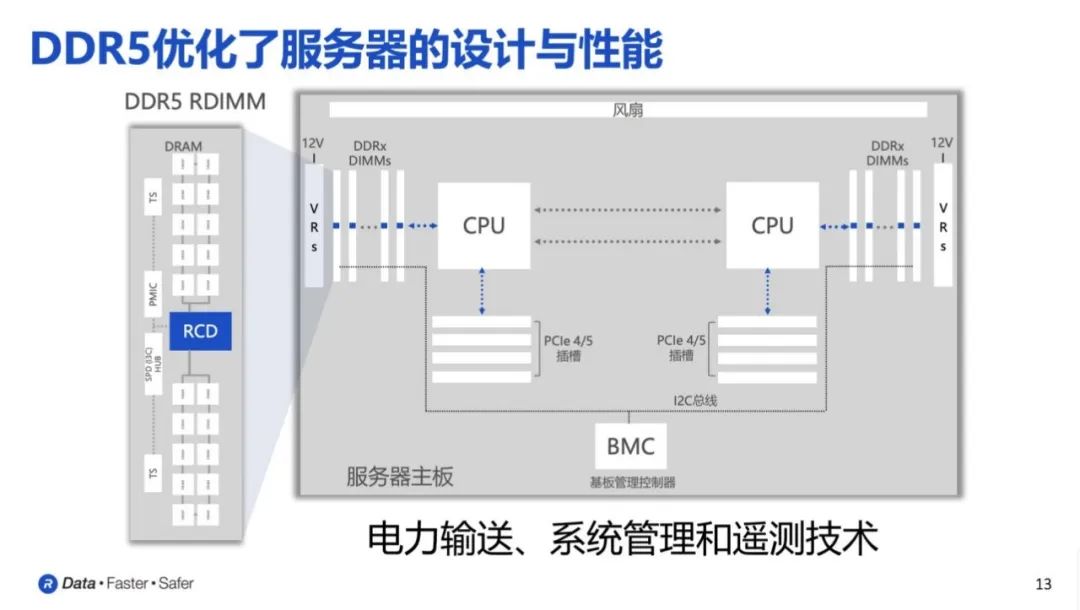

而对于DDR5 RDIMM而言,除了RCD和DB之外,SPD Hub和温度传感器这两颗芯片对于整个模组的性能提升至关重要。这两颗芯片是服务器级DDR5模组实现电力输送、系统管理和遥测技术的关键,进而也将影响到服务器的整体设计和性能改善。

下图是一个非常典型的双插槽服务器设计,每个插口都有一组DIMMs和PCIe插槽,可以填充SSD、网卡、加速器等。另外有一个底板管理控制器,可以通过各种接口与主板的所有组件进行通信。此外还有一系列的风扇来管理散热和温度。

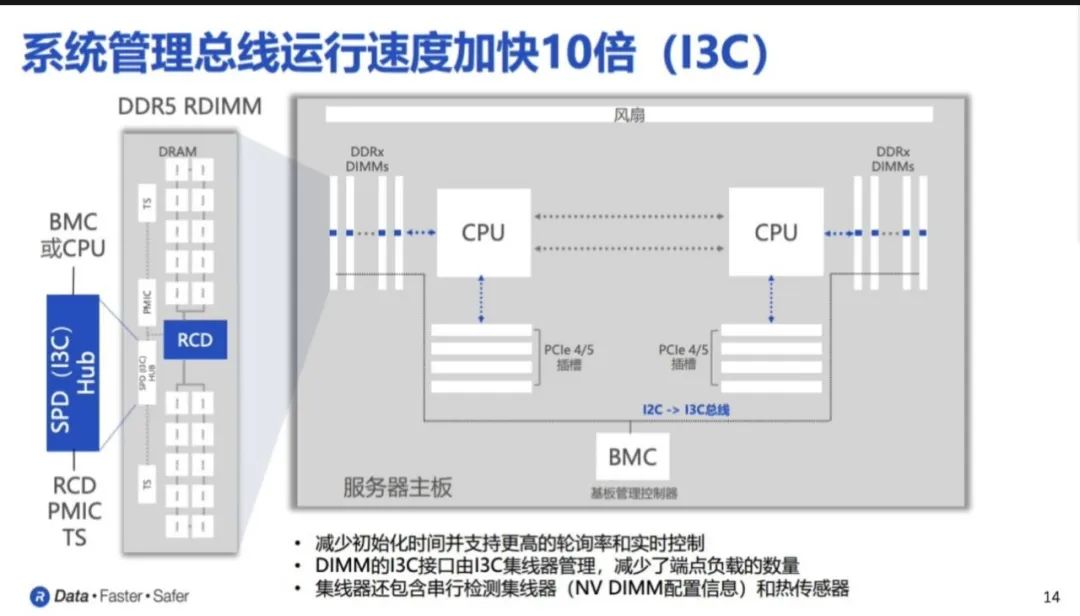

系统总线在服务器初始化时被大量使用,以发现接入的DIMMs,并执行早期的内存通道校准。DDR5将系统总线从DDR4的I2C升级到了I3C,从而实现了运行频率从1MHz到10MHz的十倍提升。为了支持这种更高的速率,就需要支持I3C接口的SPD Hub进行通信。

SPD Hub将总线隔离到控制器一侧的单个DIMM,与主机进行通信。在目标端点,SPD Hub可以与模块上其他具有I3C接口的芯片(RCD、PMIC和独立的热传感器等)进行通信。除了减少初始化时间,总线速度的提高也将支持更高的轮询率和实时控制。该SPD Hub还包括串行存在检测集线器,存储了DIMM的非易失性配置信息,并具备热传感器。

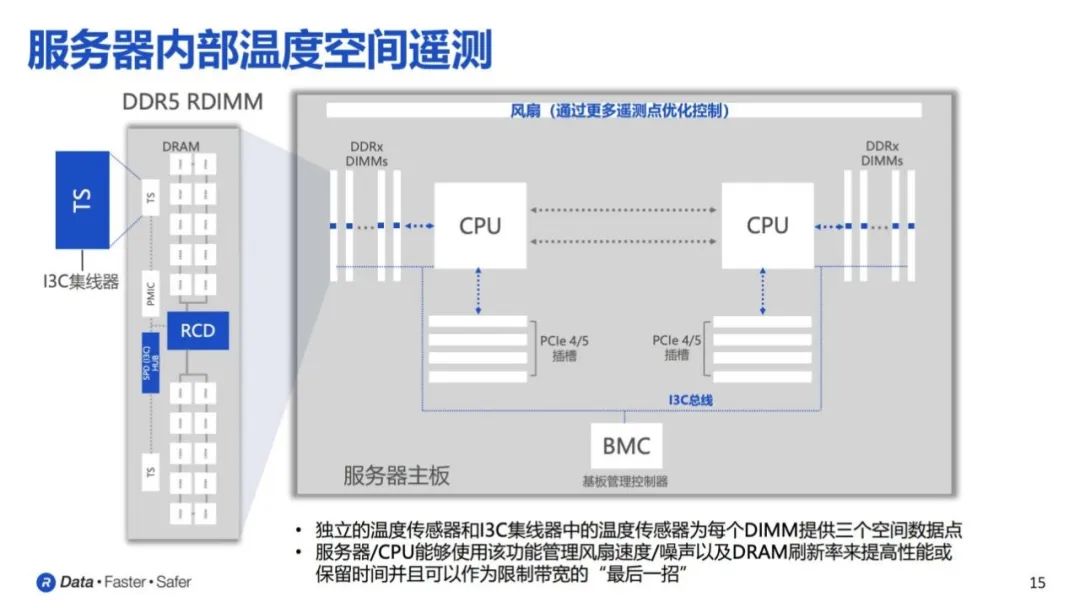

相比消费级的DDR5内存条,服务器级的DDR5模组对于温度控制的要求更高,因此TS必不可少。每个RDIMM的两端各布置了一个TS,通过I3C与SPD Hub进行通信。两端的TS与SPD Hub中的内置温度传感器一起,实现了RDIMM上三个空间点的温度监测数据,多个DIMMS一起就提供了服务器中大量的温度情况信息。服务器/CPU能够使用该功能管理风扇速度/噪声以及DRAM刷新率来提高性能或保留时间,并且可以作为限制带宽的“最后一招”,可以选择节流带宽,以减少热量。

/03/

DDR5 DIMM芯片组:加速内存产品上市

由于DDR5设计规范上的巨大变化,设计DIMM内存的难度比DDR4要更高一些。John Eble表示,由于高的数据传输效率所带来的复杂性的进一步提高,所以对于整体的热管理,还有包括信号完整性的管理提出了新的要求。

因此在DDR5时代,提供包含RCD、DB、SPD Hub和TS在内的更完整的DIMM芯片组,就变得非常必要。这种芯片组可以降低客户的设计、开发和验证门槛,帮助加速实现产品上市。

Rambus在信号完整性、接口IP方面,有着非常深厚的技术积累,这是其技术护城河之一。在其DDR5 的成功的RCD和DB产品之后,新加入的SPD Hub和温度传感器作为内存模块上非常关键的两个部件,能够帮助实现服务器或PC当中具体的系统配置的感知,反馈之后从而实现更好的整体系统优化。

据John Eble介绍,新的更为完整的DDR5 DIMM芯片组,可以提供两大优势。第一是能够实现更好的、更有效率的内部验证的过程。不论是芯片送去生产之前,以及在拿回生产芯片之后,DIMM芯片组的芯片都可以整合在一起,能够实现更好的质量的校验,确保整个芯片达到之前所设计的质量标准或速率的标准。

第二个主要优势是提供了更好的客户体验和一站式的质量追溯。新SPD Hub和温度传感器发布,让Rambus成为一个对客户来说更重要和更有意义的供应商。客户拿到DDR5的相关芯片之后,可以自己进行模组的整合。如果使用中间或后期有一些相关问题,只需找到Rambus一家,即可帮助他们解决所有出现的问题,这带来了更好的用户体验,客户的产品后期出现问题也可以实现一站式追溯。

John Eble表示,内存接口芯片本身是为了解决主机内存控制器和DIMMs之间的信号完整性问题。Rambus在整个数据信号完整性、电源完整性和功率完整性方面,有超过30多年丰富的经验,可以给到客户非常多的价值。为降低客户的设计复杂度,提升可靠性和成功率,Rambus的在模组设计和系统设计方面已经实现了早期的系统验证,以确保这些设计留出余量。

此外,Rambus还和CPU厂商保持着非常密切的合作,完成了大量的早期工作。例如在CPU厂商的参考平台上进行模拟和验证工作,通过CPU厂商与生态系统分享DDR5 DIMM的设计。

/04/

总结

DDR5正处于爬升阶段,面临着巨大的市场机遇,生态内更需要一个可靠、高性能的DDR5 DIMM芯片组,来帮助内存厂商加速DDR5 DIMM产品上市。

和先进DRAM产品在市场的渗透步伐一致,Rambus的发展策略也是先关注数据中心的各项应用,开发出一系列领先的解决方案,然后逐步向更广泛的市场去推广。

Rambus大中华区总经理苏雷表示,作为行业领先的DDR5 RCD接口芯片的补充,新推出SPD Hub和温度传感器两款芯片产品使得Rambus不但在服务器内存模块市场拓展了产品组合,也为Rambus在消费级内存模块市场开辟了一个新的机遇。

审核编辑 :李倩

-

Rambus推出6400MT/s DDR5寄存时钟驱动器,进一步提升服务器内存性能2023-02-22 0

-

Rambus扩大面向数据中心和PC设备的DDR5内存接口芯片组合2022-08-18 594

-

RMBS扩大面向数据中心和PC设备的DDR5内存接口芯片组合2022-08-18 573

-

DDR5爆发前夜,Rambus再次扩充产品阵营2022-08-31 1889

-

有关DDR5设计的更多技术细节2022-09-23 2531

-

服务器对DDR5内存标准的要求2022-09-30 2002

-

Rambus推出DDR5系列产品:串行检测集线器和温度传感器2022-11-02 1464

-

DDR5游戏DIMM解决方案2022-12-09 305

-

ChatGPT带旺服务器需求,Rambus发布第三代DDR5 RCD芯片,提前卡位DDR5市场爆发2023-03-02 4760

-

浅谈Rambus对DDR5市场趋势的前瞻见解2023-05-06 516

-

Rambus通过全新PMIC系列支持多代基于 DDR5 的高性能服务器2024-06-20 866

-

Rambus 通过 DDR5 服务器 PMIC 扩展适用于高级数据中心内存模块的芯片组2024-06-21 269

-

昂科烧录器支持Montage澜起科技的串行检测集线器 (SPD Hub) 芯片M88SPD5118A52024-08-28 282

-

Rambus推出DDR5客户端时钟驱动器,将业界领先的内存接口芯片产品扩展到高性能 PC领域2024-08-29 824

-

Rambus推出DDR5客户端时钟驱动器2024-09-03 519

全部0条评论

快来发表一下你的评论吧 !