可编程逻辑电路设计—可制造性设计DFM

可编程逻辑

描述

在一般工业中,可制造性设计(Design for Manufacturability,DFM)是指一套应用于产品设计阶段的方法,其在设计的早期阶段,就考虑产品制造过程中的困难、要求和约束等,使得最终产品具有良好的可制造性和成品率,能以最低成本、最短时间、最高质量被制造出来。

在集成电路中,DFM主要是针对集成电路制造工艺面临的严峻困难,通过前段和后段的设计手段来部分解决或缓解工艺制造的困难,提高电路制造后的功能成品率(Functional Yield)和参数成品率(Parametric Yield)。

随着集成电路工艺进入纳米尺度,集成电路制造面临日益严重的挑战。例如,采用193nm波长光源的亚波长光刻导致硅片图形严重畸变,化学机械抛光工艺导致互连线在高度方向发生严重偏差,工艺扰动的影响日益严重等。

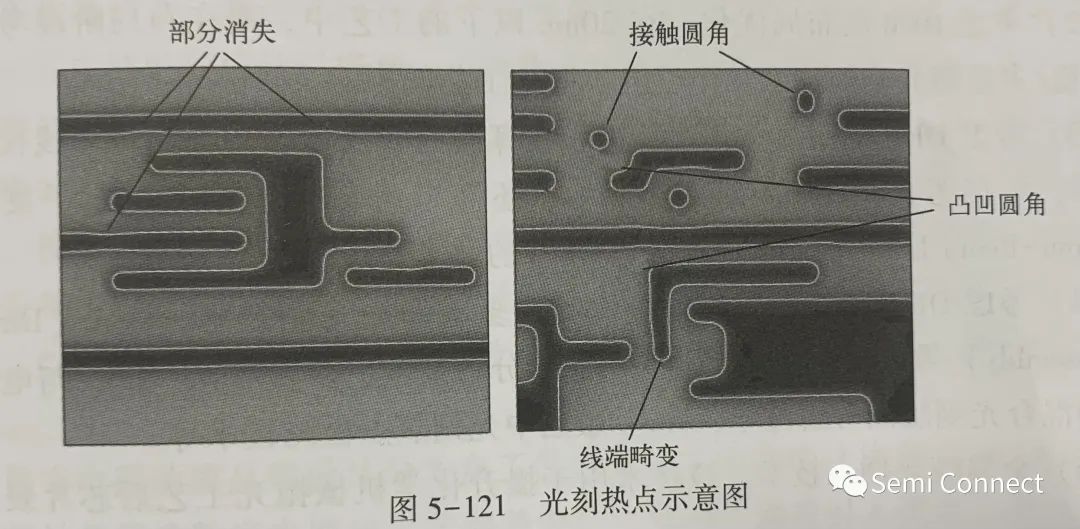

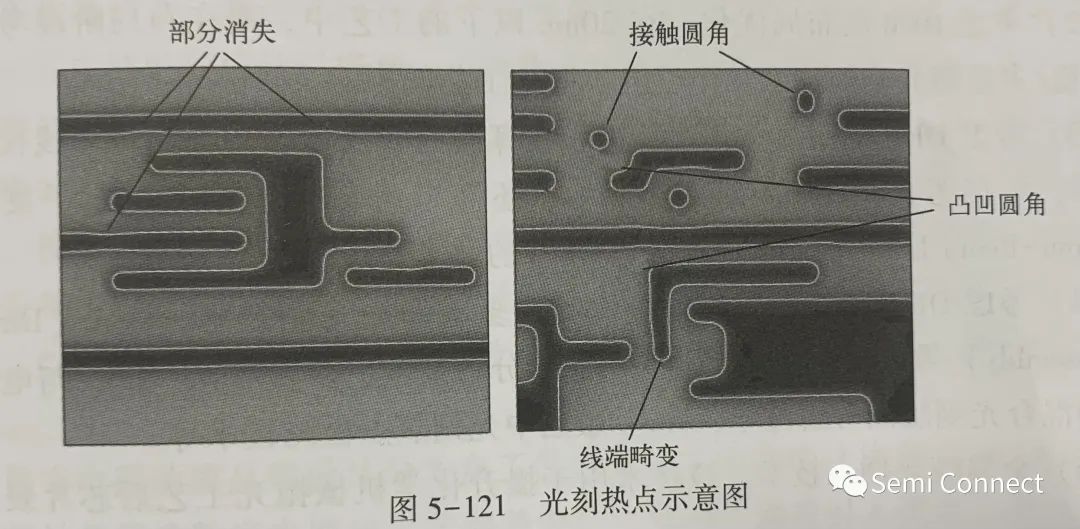

在亚波长光刻工艺中,即使采用分辨率增强技术(Resolution Enhancement Technology,REF)后,光刻中依然容易在互连线顶端和拐角处出现“圆角”形变(Round-off),在线段中出现部分消失(Partial Disappearance)等畸变现象,如图5-121所示。这些可能产生畸变图形的设计版图(Pattern)称为光刻热点,在设计时应尽量避免此类图形,而在流片前要用光刻热点检查工具进行彻底排查。

金属哑元插入(Dummy Filling)对化学机械抛光(Chemical Mechanical Polishing,CMP)工艺后芯片表面形貌影响如图5-122所示。插入金属哑元后,芯片表面平整性明显优于插入哑元前。但引入金属哑元会增加寄生电容,降低电路性能。因此,在芯片哪些位置插入哑元、插入多少哑元、确定哑元形状等是哑元填充工具需要解决的关键问题。上述光刻热点检查和金属哑元插入技术均属于常见的DFM技术。

总体而言,DFM技术是针对传统设计流程的扩充和优化,其通常包括如下技术。

(1)考虑DFM的标准单元设计技术。该技术不仅需考虑标准单元本身的可制造性,而且应考虑相邻单元边界附近光刻的相互影响。在考虑DFM的标准单元综合技术中,除需满足传统设计规则外,还需兼容大量新增的DFM设计规则;甚至为提高成品率,标准单元行间隙(Line-Gap)也需进行优化。为了兼容多重曝光和自对准双重曝光等新的光刻工艺,满足日益紧张的布线通道约束,输入/输出的位置(Pin Access )也需进行仔细优化。

(2)考虑DFM的布局优化。在20nm以下的工艺中,需在布局阶段考虑双重/三重/多重曝光光刻技术和化学机械抛光工艺的影响。

(3)考虑DFM的布线优化。传统布线算法一般仅考虑布通率、总线长等优化目标,而在考虑DFM的布线优化中,还需考虑与多重曝光、电子束光刻(Electron-Bean Lithography)等新光刻技术的兼容性。

(4)考虑DFM的掩模版优化。例如,多重曝光光刻技术、DSA(Directed Self-assembly)等新光刻工艺中的版图图形分解技术、多重曝光、DSA与电子束光刻的混合光刻版图分解技术、Mask版图中光刻热点检测技术等。

(5)金属哑元插入技术。该技术用于提升化学机械抛光工艺后芯片表面的平整性。

(6)冗余通孔技术(Redundant Via)。该技术用于提升通孔的可靠性。

当集成电路进入纳米尺度后,部分DFM技术已进入芯片代工厂(Foundry)的参考设计流程(Reference Flows)中,是设计者必须考虑的设计环节之一。在可见的未来,DFM技术会随着新的制造工艺和设计技术的出现而不断扩充和发展。集成电路设计者需在具有DFM功能的电子设计自动化(Electronic Design Automation,EDA)工具的协助下,在设计阶段充分考虑工艺制造中的困难,这样才能有效提升流片后芯片的成品率。

审核编辑 :李倩

-

什么是现场可编程逻辑阵列?它有哪些特点和应用?2024-05-23 2663

-

标准高速可编程阵列逻辑电路数据表2024-05-13 365

-

高性能冲击可编程阵列逻辑电路数据表2024-05-11 380

-

高性能Impact X可编程阵列逻辑电路TIBPAL16C数据表2024-05-07 390

-

什么叫可编程逻辑器件 可编程逻辑器件有哪些特征和优势?2023-09-14 4577

-

可创建小型组合与时序逻辑电路的PLU可编程逻辑单元2022-12-01 2688

-

实现可编程逻辑电路的三种主要技术2022-09-08 3218

-

可测性设计工具在可编程逻辑电路中的应用2022-08-26 1689

-

可编程逻辑电路设计2022-08-22 1874

-

可规划逻辑电路设计与实习报告2021-12-23 1290

-

现代数字逻辑电路实践教学探索与改革2010-05-24 593

-

基于可编程逻辑器件的数字电路设计2009-11-16 1940

-

什么是可编程逻辑2009-05-29 3801

全部0条评论

快来发表一下你的评论吧 !