详细介绍RH850U2A芯片相关的功能

电子说

描述

前言

RH850U2A芯片是瑞萨公司针对电控类域控制器而发布的一块最新MCU芯片,功能及其强大。本系列文章讲详细介绍RH850U2A相关的功能,本文为RH850U2A-MPU功能详解。

正文

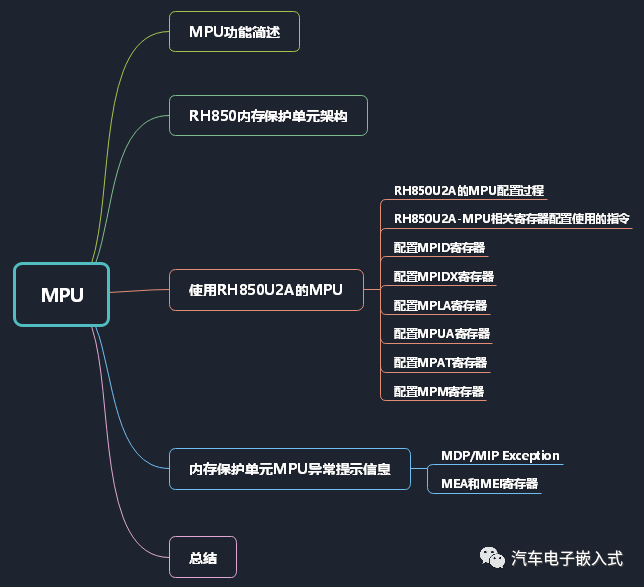

1.MPU功能简述

MPU保护与当前执行的代码“不相关“的所有数据。“不相关”是相关内存地址的权限受限制,或者是程序访问内存地址的范围于其无关,阻止关键数据被破坏,使嵌入式系统更加健壮与安全。

MPU作用主要有两个方面:为两个保护,一个检测。

1)MPU的保护作用

指访问区域的保护和读写区域的保护。

① 访问区域的保护。

可以将内存区域划为特权区域和普通区域,特权区域只有特权用户才能访问,普通用户被禁止访问,以此来保护特定的数据。

常见的应用场景:

1> 对带系统的来说,可以设置数据,以防止用户应用程序破坏操作系统使用过程中的数据。

2> 隔离任务,以防止一个任务访问其他任务的数据。

3> 将SRAM或者RAM空间定义为不可执行,防止代码注入。

② 读写区域的保护。

设置指定的区域为只读,可以有效的防止比较关键的数据被错误修改。

2)MPU的检测功能

指可以检测堆和栈的溢出情况及数组有没有越界。

功能安全中对内存分区MPU的相关描述:汽车ECU软件是高度模块化的嵌入式软件,其功能实现是可以为非功能安全,和功能安全的SWC组合,它们分别拥有不同的ASIL安全等级。

根据ISO26262,如果嵌入式软件包含不同ASIL等级的SWC,要么整个软件工程都需要基于最高安全等级的要求进行开发,需要保证拥有更高安全等级的SWC的操作不会受到其他SWC的干扰,也即需要做到FFI(Freedom from interference)的设计。

基于更低安全等级要求开发的SWC,可能会出现错误地访问到更高安全等级SWC的内存区域,产生干扰。

为此,SWC需要运行在不同的内存区域,或者不同的内存分区,来防止类似的内存访问违例。

ISO26262中,以下内存相关的故障影响被视为SWC之间产生干扰的原因:

-内容损坏

-读写区域属于另一个SWC

-数据不一致

-栈溢出或栈下溢

要满足上述定义,是MPU内存保护的目标, 也可以通过限制对于内存以及内存对应的硬件的访问。

这里的内存分区意味着:

各OS Application运行在相互保护(不干涉)的内存区域 ,在某一个分区上运行的代码,无法修改另一个分区的内存。

内存分区也可以保护只读内存段(例如代码执行)以及内存对应的硬件。

内存分区和用户/特权模式可以保证SWC之前互不干扰——即使某一个SWC出现了内存相关的故障,也不会对其他软件模块有影响。

如果一个SWC运行在用户模式,那么它对CPU资源/指令的访问也是受限制的。

MPU的微控制器有专用的硬件:即内存保护单元(MPU),来支持内存分区。

2.RH850内存保护单元架构

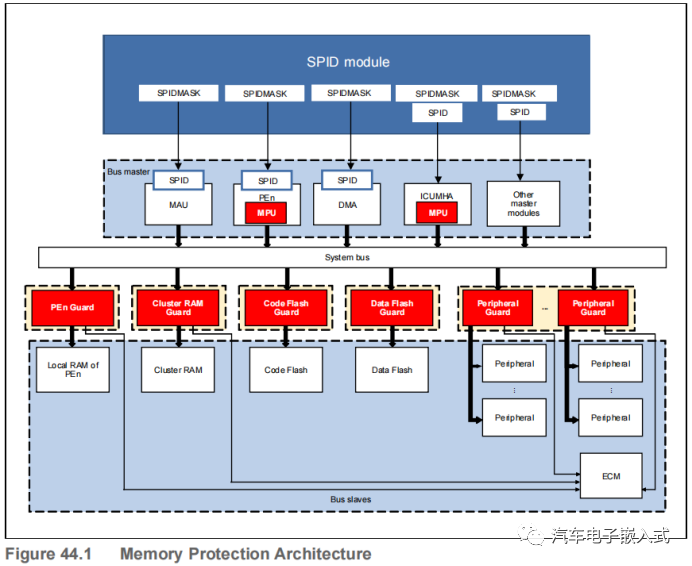

RH850U2A芯片具有内存保护/保护功能,防止对内存数据的错误访问,并控制外围模块的寄存器。下图1显示了内存保护的整体架构。每个可编程核心(总线主机)都有一个内存保护单元(MPU),它定义了软件访问保护。此外,每个资源(总线从设备)都有一个守卫来控制任何总线主设备的访问,包括那些没有MPU的,比如DMA。

3.使用RH850U2A的MPU

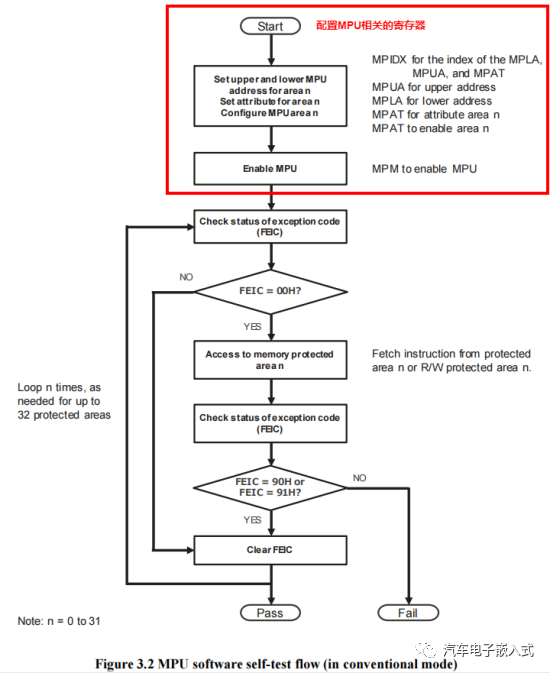

3.1 RH850U2A的MPU配置过程

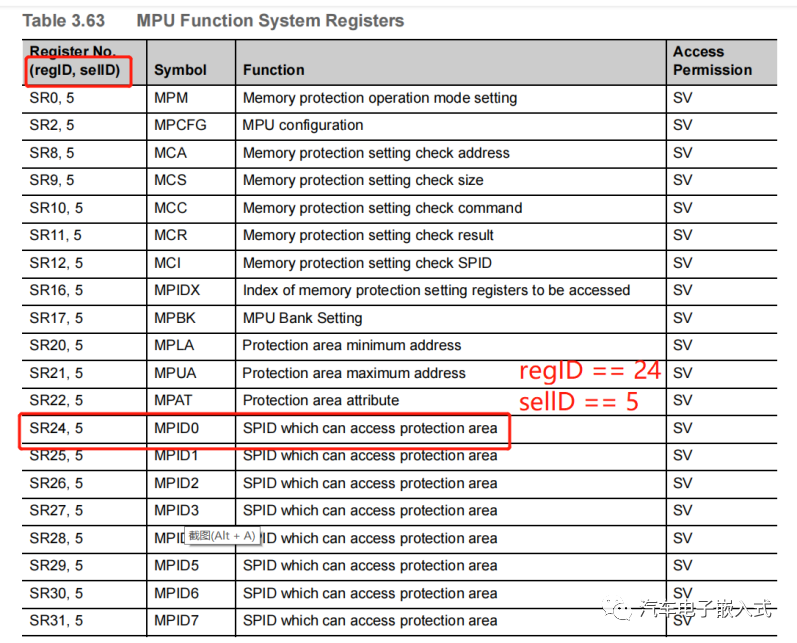

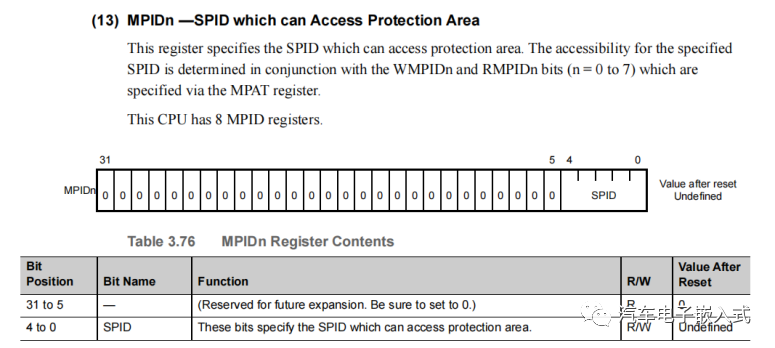

1)第一步,配置MPIDn寄存器。在使能了MPU功能后,哪些硬件模块还可以访问所有的内存保护区域。

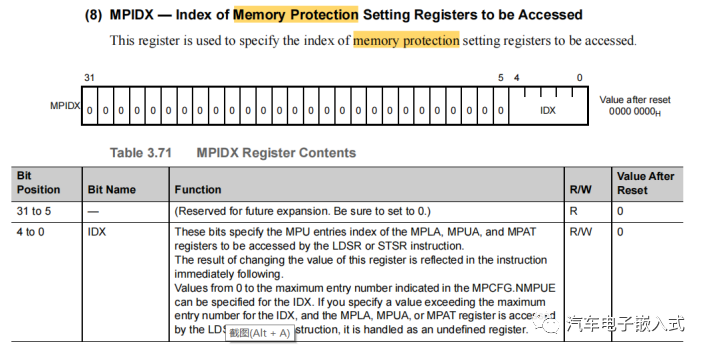

2)第二步,配置MPIDX寄存器。配置每一个内存保护块的时候,需要先配置MPIDX寄存器直没entry ID。

3)第三步,配置MPLA寄存器。配置每一个内存保护块的Minimum地址。

4)第四步,配置MPUA寄存器。配置每一个内存保护块的Maximum地址。

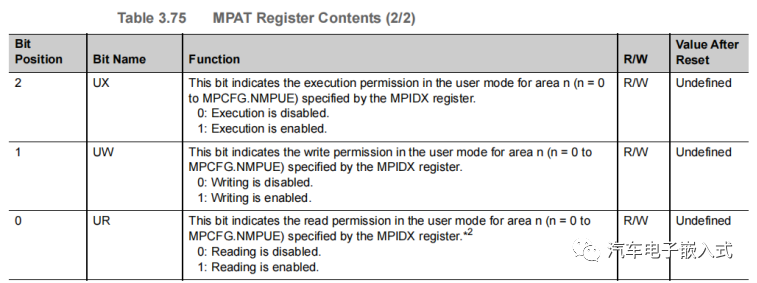

5)第五步,配置MPAT寄存器。配置每一个内存保护块的USER/SVP模式下的可读、可写、可执行的属性。

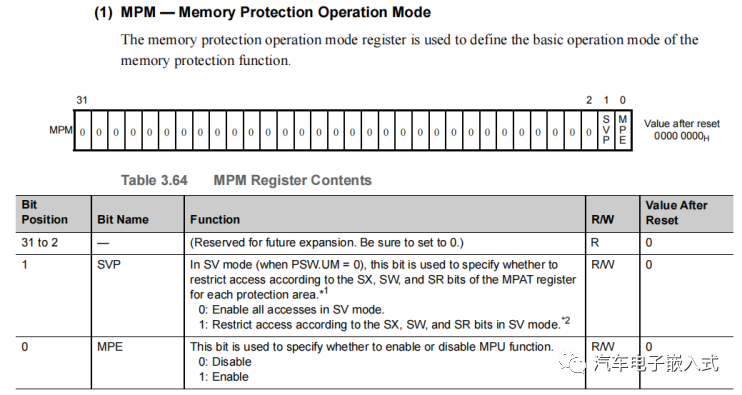

6)第6步,配置MPM寄存器。使能MPU功能。

3.2 RH850U2A-MPU相关寄存器配置使用的指令

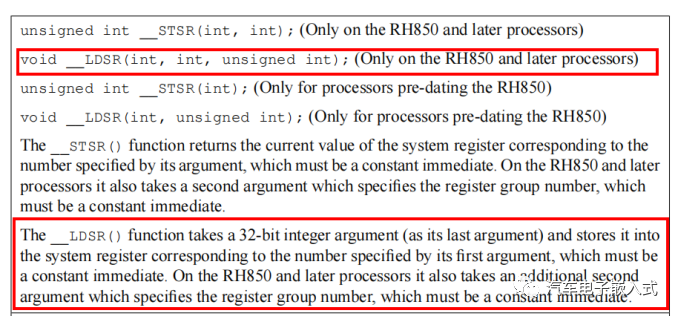

使用 void __LDSR(int regID, int selID, unsigned int val);

Note: 什么是寄存器的regID和sellD? -- __LDSR()函数接受一个32位整数参数(作为它的最后一个参数),并将其存储到系统寄存器中,与它的第一个参数指定的数字相对应,该参数必须立即是一个常量。在RH850和以后的处理器上,它还需要另一个参数,该参数指定寄存器组号,它必须立即是一个常量。简单来讲regID就是寄存器ID,sellD就是寄存器所在的组ID。

3.3 配置MPID寄存器

MPID寄存器配置哪一些模块可以直接访问内存保护区域。

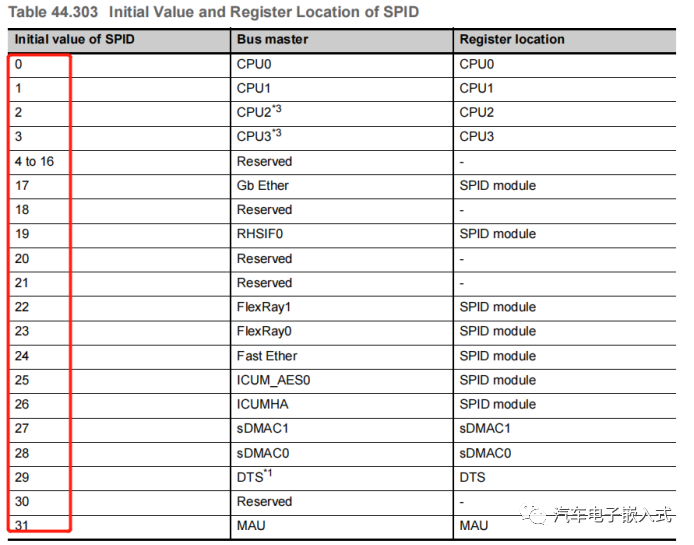

下表记录了有哪些SPID可以配置为直接访问内存保护区域。

示例:__LDRS(24, 5, 0)//CPU0可以访问保护区域

3.4配置MPIDX寄存器

每一个内存保护块都有一个IDX(最多32个,0-31),在配置每一个内存保护块的访问属性的时候,首先要配置MPIDX寄存器。

示例:__LDRS(16,5,0);//通过MPIDX寄存器配置第一个entry的IDX。

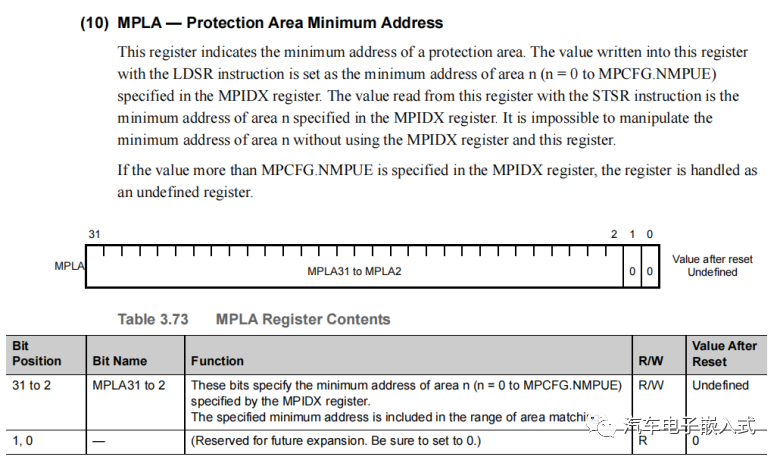

3.5配置MPLA寄存器

MPLA配置当前内存保护块(MPIDX == 0-31)的起始地址(Minimum Address)。

示例:__LDRX(20,5, 0x00007F00);

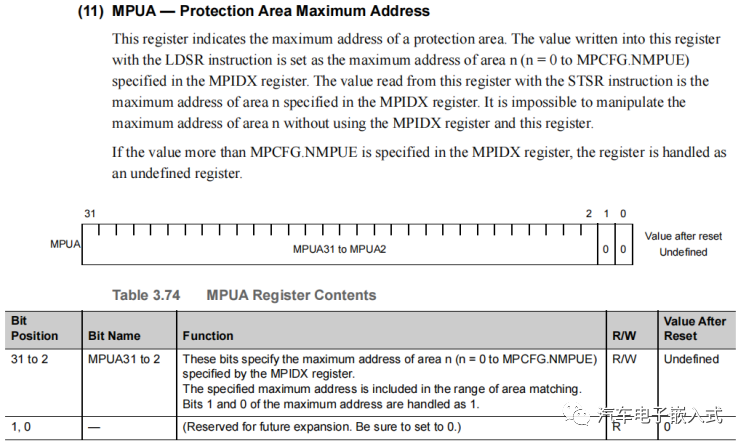

3.6配置MPUA寄存器

MPLA配置当前内存保护块(MPIDX == 0-31)结束地址(Maximum Address)。

示例:__LDRS(20,5,0x00017FFC);

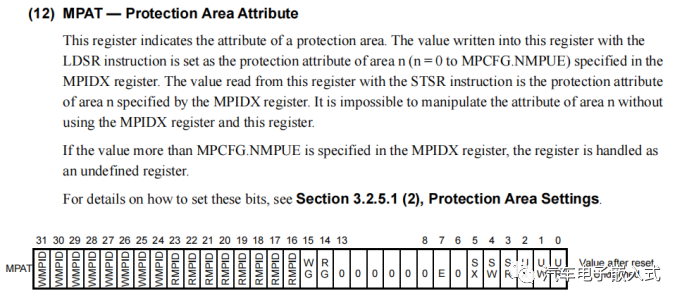

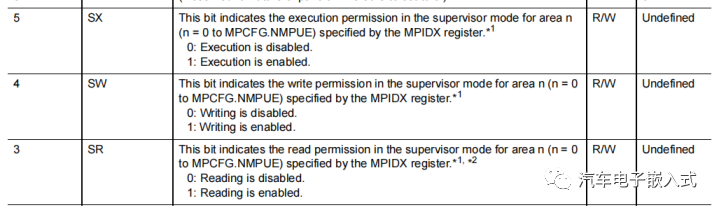

3.7 配置MPAT寄存器

MPAT寄存器配置每一个内存保护块的访问属性(user模式下的可读UR、可写UW、可执行UX; supervisor模式下的可读SR、可写SW、可执行SX)。

3.8 配置MPM寄存器

使能(Enable)MPU功能。

4.内存保护单元MPU异常提示信息

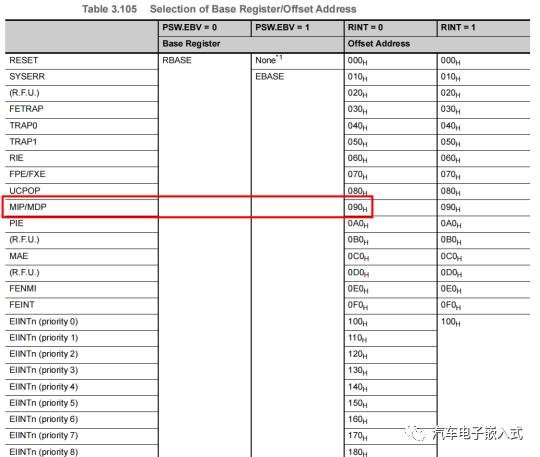

4.1 MDP/MIP Exception

产生内存保护后会产生MIP/MDP Exception(异常中断地址偏移,0x90,如果我们设置EBASE为0x00080000,那么异常中断的绝对地址就是0x00080090)。

在MIP/MDP Exception的异常中断处理函数汇总一般会条用_Os_Abort触发OS调用ShutdownHook函数,在这个函数里面我们可以做一些故障信息保存动作。

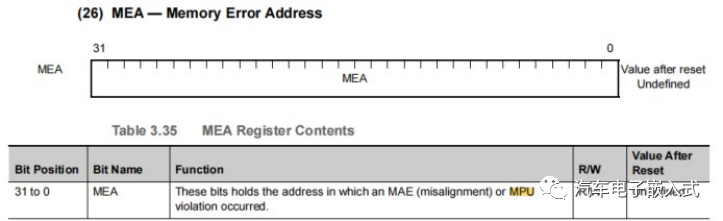

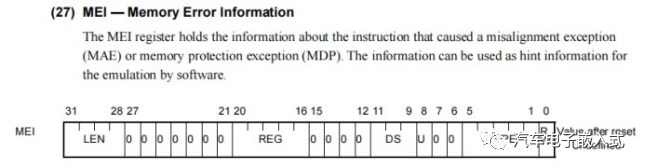

4.2 MEA和MEI寄存器

产生了MIP/MDP异常之后,MEA寄存器会存储异常地址,MEI寄存器会存储异常指令。

5.总结

本文介绍了MPU的基本原理,以及结合RH850U2A芯片详细介绍了MPU的配置使用过程,同时介绍了MPU保护功能产生后如何去识别异常信息。MPU在实际项目功能中非常的有用,如果使能了MPU,同时能通过有效的方法记录MPU异常中断时的MEI/MEA寄存器的信息,那么在发生了异常复位后就能通过历史信息来定位复位的SWC(实际项目中不可能一直都有仿真的机会,所以这个功能非常的重要)。

Note: MPU的配置及使能一般都是在EcuM_Init之前完成。

审核编辑:刘清

-

TC3xx芯片的MPU功能详解2023-09-19 5594

-

RH850/U2A 516pin 用户手册: PiggyBack Board(Y-RH850-U2A-516PIN-PB-T1-V1)2023-07-04 563

-

RH850/U2A 176pin 用户手册:Piggyback Board(Y-RH850-U2A-176PIN-PB-T1-V1)2023-06-30 480

-

RH850/U2A 516pin 用户手册: PiggyBack Board (Y-RH850-U2A-516PIN-PB-T1-V1)2023-02-02 565

-

RH850/U2A 176pin 用户手册:Piggyback Board (Y-RH850-U2A-176PIN-PB-T1-V1)2023-01-10 678

-

RH850/U2A 156pin 用户手册:搭载板(Y-RH850-U2A-156PIN-PB-T1-V1)2023-01-09 518

全部0条评论

快来发表一下你的评论吧 !