SRAM的基本结构、应用及挑战

存储技术

描述

存算一体化是指将传统以计算为中心的架构转变为以数据为中心的架构,它可以突破冯·诺伊曼架构下存算分离的瓶颈,直接利用存储器进行数据处理,从而把数据存储与计算融合在同一芯片中,极大提高计算并行度与能效比,特别适用于深度学习神经网络领域,如可穿戴设备、移动设备、智能家居等场景。

在上期的文章里,我们介绍了新型非易失性存储介质ReRAM用于存算一体大算力AI芯片的优势,今天我们来介绍另一种常见的存储介质——SRAM。

SRAM的全称是静态随机存取存储器(Static Random-Access Memory, SRAM) 是随机存取存储器的一种。

所谓“静态”,是指只要保持通电,写入的信息就不会丢失,读出时也不破坏存储的信息。这种“静态”是相对于动态随机存取存储器(Dynamic Random-Access Memory,DRAM) 而言的。后者由于存储位元是基于电容器的电荷量进行存储,电荷量会随着时间和温度的变化而减少,因此需要定期刷新来保持原有的记忆信息。但无论是SRAM还是DRAM,都属于易失性存储器,在断电后就会丢失数据。

SRAM 的基本结构

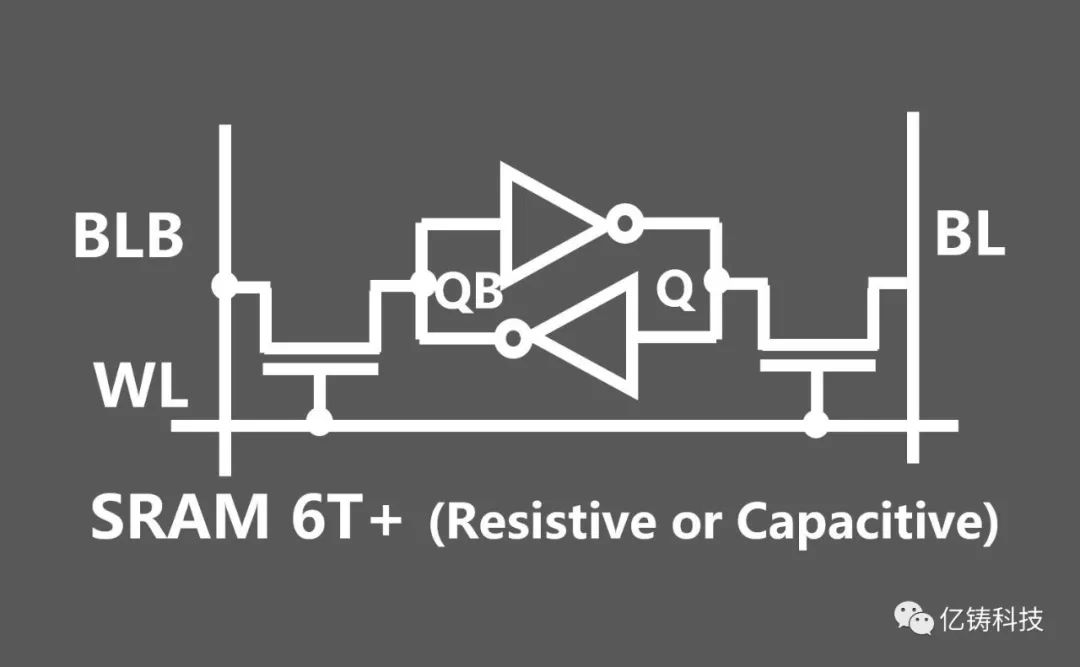

一个经典的6-T SRAM cell结构如下:1个bit (基本存储单元) 由6个晶体管构成,主要包括2个CMOS反相器,以及2个控制管。具体而言,每个反相器包括1个PMOS和1个NMOS,分别将信号反转后输入到另一反相器中,组成交叉连接的锁存结构,其输入输出由2个NMOS控制,存储和读取需要的信息。

SRAM在存算一体中的应用

在学术领域,SRAM凭借其高成熟度和高存取速度成为了存算一体领域里的热门研究对象;在市场应用方面,SRAM作为传统存储介质适合IP化,SRAM存算一体在中小算力、端侧、对待机功耗无要求的场景,例如:可穿戴设备、边缘计算、无人车等市场具有一定的应用价值。但也因其单元面积大、静态功耗高、易失性、对PVT变化敏感、存储密度低、密度提升潜能较低、成本高等特点,在应用于一些大算力、大容量、高密度集成的大型神经网络计算场景时会受到较多限制。

SRAM应用于大型神经网络计算的两大挑战

#1漏电流

当SRAM应用于存算一体架构,由于SRAM即使待机也会产生静态漏电功耗,因此,大量的SRAM封装在一起,实现巨量的并行计算(读取操作)要解决巨大的电流电压波动问题和功耗问题。所以对企业来说,实现SRAM大容量和高并行度读取(高算力)的设计和工程落地有着较高的工艺和设计门槛,会导致设计和工程成本极高,成为了基于SRAM的存算一体技术商用路上较难跨越的阻碍。

在未来的车载和数据中心的应用场景中,SRAM的高功耗,和器件特性对温度比较敏感等特性,还可能导致用电量高和运行不稳定。

#2密度

SRAM基本单元是由6个Transistor组成的锁存结构,密度相对来说较低。存储单元在做存算的时候,需要更多Transistor进行控制,比如使用8T、10T或更多Transistor的架构,导致了面积大、单位密度受限。

同时,SRAM算力的提升主要靠工艺制程的升级,器件本身在密度上难以实现大规模突破。

上期提到,ReRAM的微缩性有着天然的优势,不主要靠CMOS制造工艺的升级就可以实现每代密度翻倍。

在未来,大型神经网络参数动辄几个GB,SRAM难以容纳如此大的参数,很难跟上AI模型规模的发展节奏。相比之下,基于ReRAM的存算一体芯片可以轻易做到高密度,而亿铸科技的方案还能够实现多芯片互联,从芯片系统角度进一步提升密度和算力。

亿铸科技选择基于ReRAM的全数字化存算一体技术,无需ADC/DAC模数和数模信号转换器,不会受到信噪比的影响,精度可以达到32bit甚至更高,既不会产生精度损失,也不会面临模拟计算带来的诸如IR-DROP等问题,非常适合实现大算力、高精度、高能效比的存算一体AI芯片。

审核编辑:汤梓红

-

设计SRAM电路时,使用双联锁结构2019-10-11 1426

-

单端口SRAM与双端口SRAM电路结构2020-07-09 6827

-

SRAM的性能和结构2020-12-29 2777

-

静态随机存储器SRAM面临的问题挑战2021-02-25 2690

-

如何设计具有相似功能且基于SRAM编程技术的电路结构?2021-04-14 1526

-

基于SRAM和DRAM结构的大容量FIFO的设计与实现2010-02-06 958

-

SRAM的结构框图2009-12-04 3322

-

基于DBL结构的嵌入式64kb SRAM的低功耗设计2010-01-12 1264

-

SRAM模块,SRAM模块结构原理是什么?2010-03-24 4729

-

SRAM 72-Mbit QDR® II SRAM 2 字突发结构2017-10-10 866

-

SRAM随机存储器的特点及结构2020-04-30 4072

-

对于静态随机存储器SRAM,它将面临的两大问题挑战2020-07-30 1434

-

两种SRAM的电路结构2020-09-19 9504

-

读取优先和SRAM-MRAM混合结构,几个混合结构的管理策略2020-11-17 888

-

介绍关于SRAM两大问题挑战2022-11-24 1677

全部0条评论

快来发表一下你的评论吧 !