射频功率放大器的阻抗匹配设计

RF/无线

描述

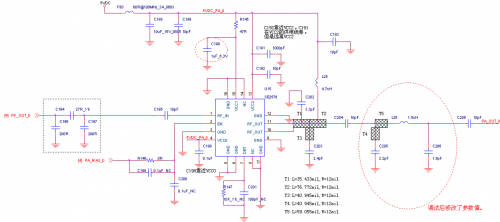

本文主要对射频功率放大器电路设计进行介绍,主要介绍了射频功率放大器电路设计思路部分,以及部分设计线路图。

一、阻抗匹配设计

大多数PA都内部集成了到50欧姆的阻抗匹配设计网络,不过也有一些高功率PA将输出端匹配放在集成芯片外部,以减小芯片面积。

常用的匹配设计有微带线匹配设计、分立器件匹配设计网络等,在典型设计中有可能会将两者共同使用,以改善因为分立器件数值不连续带来的匹配设计不佳的问题。

PA阻抗匹配设计原理和射频中的阻抗匹配相同,都是共轭匹配设计,主要实现功率的最大传输。常用工具可以使用Smith圆图来观察阻抗匹配设计变化,同时用ADS软件来完成仿真。

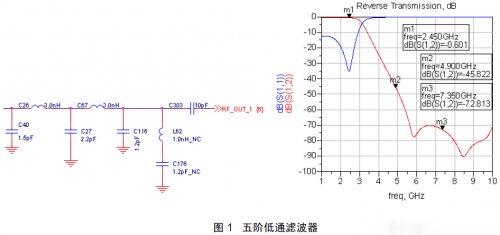

二、谐波抑制

由本人微博《射频功率放大器 PA 的基本原理和信号分析》得知,谐波一般是由器件的非线性产生的倍频分量。谐波抑制对于CE、FCC认证显得尤为重要。由于谐波的频率较分散,所以一般采用无源滤波器来衰减谐波分量,达到抑制谐波的效果。

不仅PA,其它器件包括调制信号输出端都有可能产生谐波,为了避免PA对谐波进行放大,有必要在PA输入端即添加抑制电路。

上图所示无源滤波器常用于2.4G频段的芯片输出端位置,该滤波器为五阶低通滤波器,截止频率约为3GHz,对2倍频和3倍频的抑制分别达到45.8dB和72.8dB。

使用无源滤波器实现谐波抑制有以下优点:

l 简单直接,成本有优势

l 良好的性能并且易于仿真

l 可以同时实现阻抗匹配设计

三、系统设计优化

系统设计优化主要从电源设计,匹配网络设计出发,实现PA性能的稳定改善。

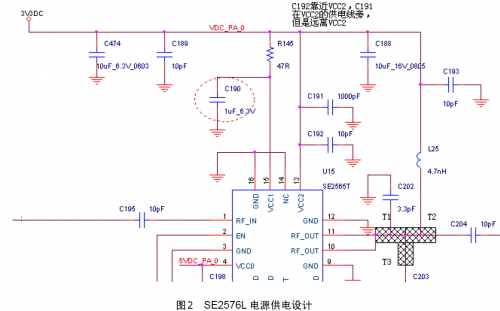

3.1 电源设计

功率放大器是功耗较大的器件,在快速开关的时候瞬间电流非常大,所以需要在主电源供电路径上加至少10uF的陶瓷电容,同时走线尽量宽,让电容放置走线上,充分利用电容储能效果。PA供电电源一般有开关噪声和来自其它模块的耦合噪声,可以在PA靠近供电管脚处放置一些高频陶瓷电容。有必要也可以加扼流电感或磁珠来抑制电源噪声。

从SE2576L的结构框图可以看出,该PA一共由三级放大组成,每一级都单独供电,前面两级作为小信号电压增大以及开关偏置电路,其工作电流较小,最后一级功率放大,其电流很大。参考DEMO设计,VCC1串联47R电阻,并联一个1uF电容用于滤波;VCC2则添加1000pF和10pF两个高频电容,充分滤除100MHz到6GHz左右频段的干扰信号。功率输出端同时也提供直流供电路径,所以流过L25的电流最大,C188用于在PA打开瞬间提供电流;添加L25、C193作用是防止射频信号泄露,并对电源产生干扰,耦合到放大器的前端,造成自激或振荡。同时在主供电电路上使用一个10uF陶瓷电容和10pF电容组合,减小PA供电网络与其它模块电源之间相互干扰。

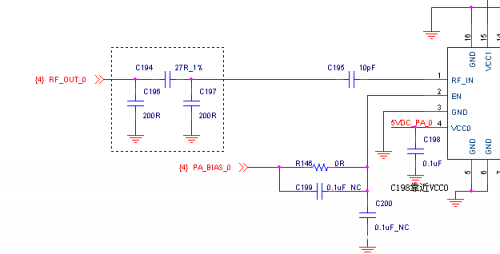

3.2 输入输出端传输线

输入输出端传输线首先需要设计阻抗匹配,微带线也用50欧姆特性阻抗线走线。连接分立元件的微带线尽量短,并且分支器件放置在射频信号传输主微带线上,避免由天线效应产生的信号泄露和辐射。

如果有必要,可以在输入端预留谐波抑制低通滤波器和π型衰减网络。

在PA输入端预留π型衰减网络,可以调节PA输入信号的动态线性范围,获得最佳的性能。如SE2576L增益为33dB,而11g线性输出最大为26dBm,则此时的输入信号强度最大为-7dBm。若产品设计输出功率为20-25dBm范围,那么输入信号范围则需要控制在− 13 到 − 8 d B m -13到-8dBm−13到−8dBm以内,而从芯片端输出的信号较大,如QCA9**1芯片输出信号大概为− 9 到 3 d B m -9到3dBm−9到3dBm具有最好的信号质量,加上4 到 8 d B 4到8dB4到8dB的衰减量可以优化线性范围。

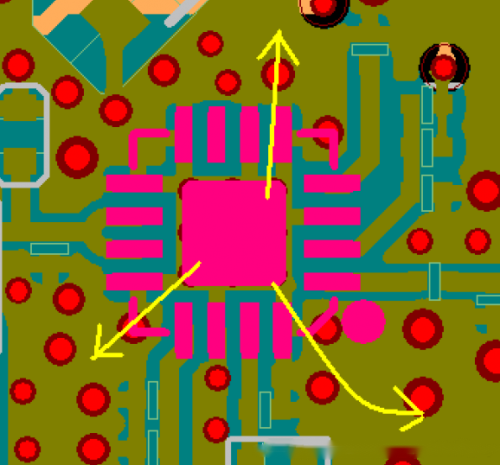

3.3 接地处理

良好的接地不仅可以获得较优的性能,同时还可以改善温度。一般PA芯片的中间是一个大的接地焊盘,这个焊盘是主要的散热途径。至少放置3*3的接地孔,可以有效地将热量传递到其它层铜箔,扩大散热能力。为了减小地过孔的等效电感值,可以增大接地孔的尺寸。

芯片一些接地和NC的引脚可以连接到地,此时可以通过这些引脚将中间的地和顶层周围地连接,进一步减小过孔引入的感性,同时增大散热面积。

芯片有效地接地,同时将顶层地区域设计的更大,减少控制线和电源线的切割,可以让热量通过最快捷的顶层铜箔散开。

3.4 电源布局

在完成器件的摆放后,再着重优化电源部分走线和布局。请参考以下原则:

l PA电源布局一般不使用电源岛,而是通过分支走线的方式来减小噪声和干扰;

l 共用大电容放置在分支点处,并添加一个高频陶瓷电容滤除射频信号噪声;

l 不同供电级数,电流不同,根据电流大小调整走线宽度;

l 高频电容靠近芯片关键放置;

l 若空间足够,可以将电源线走线长度控制在1/4波长,利用其高阻态,抑制噪声;或走一段线,也可以利用走线的等效电感,减小信号泄露。

3.5 输入输出端走线

l 使用50欧姆特性阻抗微带线;

l 隔直电容和衰减匹配网络靠近PA放置;

l 器件摆放紧凑,分支连接器件放置在射频微带线上;

l 使用微带线作匹配设计的网络,要严格按照要求计算两点线长;

l 若走线有弯折,可以串接一个器件跨接,或使用弧形线连接,避免直接走90°角;

l T型和π型网络要保持电路网络应有的结构,能够很直观看出其形态和功能,实现设计的统一,也是性能的保证。

以上内容就是射频功率放大器电路设计的大体思路以及设计过程,大体分为阻抗匹配设计、谐波抑制、系统设计优化。

审核编辑:汤梓红

-

Aigtek:功率放大器如何进行阻抗匹配2025-03-05 1280

-

高频谐振功率放大器原理2023-11-06 3039

-

功率放大器的输入、输出阻抗匹配的实现步骤2023-06-30 13998

-

射频功率放大器——如何选择合适的射频功率放大器2023-06-27 3215

-

寡头垄断的射频电源2023-05-17 8158

-

功率放大器在电动汽车动态无线电能传输阻抗匹配研究中的应用2023-04-17 1559

-

Aigtek功率放大器在使用过程中应该如何进行阻抗匹配2023-02-17 645

-

功率放大器如何进行阻抗匹配测试工作原理2022-11-26 2637

-

射频功率放大器电路该怎样去设计呢2021-11-11 995

-

射频功率放大器的全面介绍2019-06-28 4339

-

微波低噪声放大器和功率放大器2019-06-19 3123

-

射频功率放大器推动电路设计2017-03-10 5074

-

射频功率放大器简介2011-11-18 6576

-

功率放大器的阻抗匹配及防护措施2010-03-31 5976

全部0条评论

快来发表一下你的评论吧 !