自动化创建特定应用处理器

处理器/DSP

描述

如果说半导体的扩展速度仅仅是放缓而不是失效的话,那么SoC设计者面临的挑战是找到满足更大计算性能需求的方法。在2018年著名的图灵演讲中,Hennessey和Patterson就指出,需要新的方法来解决扩展失败的问题,并预测了 "计算机架构的黄金时代"。众所周知应对这一挑战的一个关键方法是在架构上进行创新,并创造更多的专用处理单元--如领域专用处理器和加速器。

如果您对半导体定律逐渐失效这个话题感兴趣,可通过此链接下载Codasip半导体扩展定律失效白皮书:https://codasip.com/2022/04/08/semiconductor-scaling-is-failing/

自动化创建特定应用处理器!

根据定义,专用的处理器核将根据其工作负荷而有很大的不同。有些可能很容易通过定制现有的RISC-V处理器核来开发。然而,这种方法并不是在每一种情况下都有效,有时可能需要开发一个新的架构。在这种情况下,有必要进行指令集架构(ISA)和微架构空间探索,以找到一个好的设计方案。

传统上,定制内核的开发是通过手动创建指令集模拟器(ISS)、软件工具链和RTL。这个过程可能很耗时而且容易出错。另一种方法是用高级语言描述处理器核,并使用处理器设计自动化来生成ISS、软件工具链、RTL和验证环境。

而第二种方法正是Codasip所能提供的核心技术之一。Codasip Studio作为一个独特的高级处理器设计自动化工具集,它已被应用于RISC、DSP和VLIW设计中。在Codasip,我们利用Codasip Studio 来开发所有的RISC-V处理器核。处理器使用CodAL架构语言进行描述,其中包括指令精确(IA)和周期精确(CA)的描述。

利用Codasip Studio探索指令集

开发一个为特定应用而优化的内核的第一步是定义指令集。如果RISC-V的标准字长如32位或64位是可以接受的,那么相应的基本整数指令集可以是一个很好的起点,用以节省时间。然而,如果选择不同的字长,如8位或16位,那么就不能直接使用RISC-V。相反,应该开发基于较小字长的指令,这一点上,谷歌在开发8位张量处理单元(TPU)时的方法值得借鉴。

Codasip CodAL

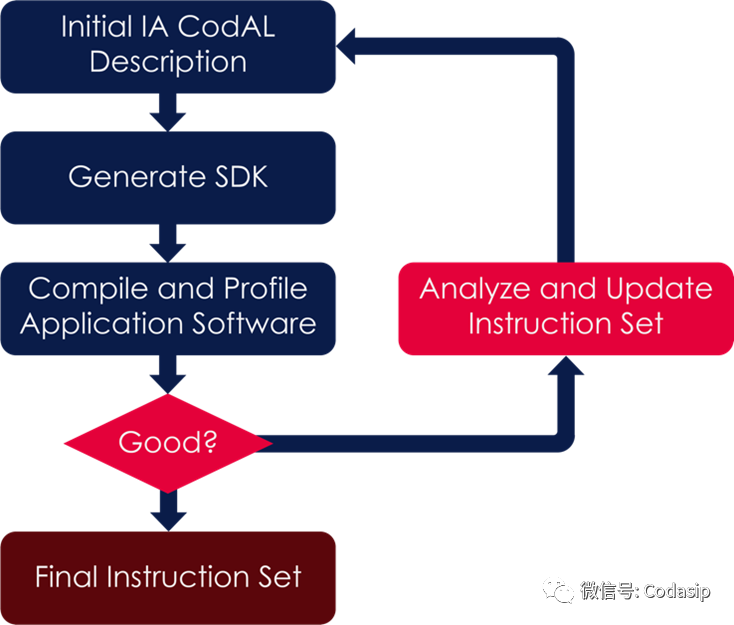

一旦定义了初始指令集,就可以在SDK in the loop中进行迭代探索。我们建议使用Codasip的CodAL处理器描述语言来描述指令集、资源和语义,而不是使用一个开源的工具链或指令集模拟器,如GCC、LLVM或Spike。一旦指令集被建模,软件工具链(或SDK)就可以使用Codasip Studio工具集自动生成。该SDK可以用来描述真实的应用软件,并且可以识别软件中的任何热点。

SDK in the loop

一旦热点被确认,就可以调整指令集以更好地满足计算负载。CodAL中更新的描述可以用来生成一个SDK,以便进一步分析。这可以通过进一步的迭代重复进行,直到ISA被最终确定。

利用Codasip Studio定义微体系架构

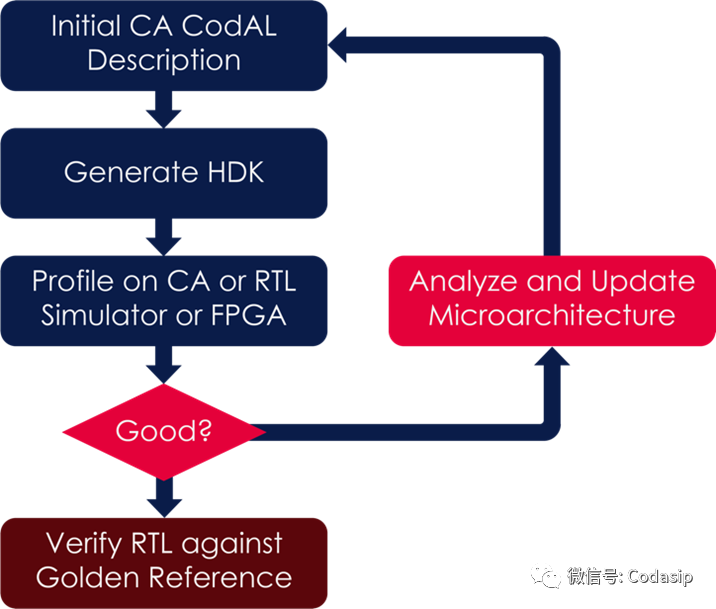

有了一个稳定的指令集,第二步就需要用CodAL来开发微架构。需要决定并行的形式(如多发射问题)或流水线深度或特权模式,这些决定将导致一个新的迭代阶段( HDK in the loop )。

HDK in the loop

CodAL被用来定义一个使用现有指令集和资源的内核的循环精确描述。反过来又可以用来生成CA模拟器、RTL和测试平台。设计的性能可以用CA仿真器、RTL仿真或FPGA原型来评估。RTL可以进行硅面积和时序分析。如果微架构没有达到其目标,可以对其进行修改并重新生成HDK。

最后一步同时也是最重要的便是根据IA黄金参考来验证最终的RTL。Codasip Studio可以为此生成UVM验证环境。此外,Codasip Studio具有帮助功能覆盖和生成随机汇编程序的工具。当然用户还应该使用自己的定向测试并应用多种验证策略。

审核编辑:汤梓红

-

恩智浦i.MX 94应用处理器如何变革工业和汽车连接2025-01-17 2333

-

自动化创建UI并解析数据2024-11-29 9611

-

什么是专用处理器?专用处理器的设计方法和工具介绍2023-07-17 2366

-

应用处理器芯片行业科普2022-01-25 879

-

410e/APQ8016E应用处理器是什么2021-12-23 1295

-

DSP处理器与通用处理器的比较2021-09-03 2071

-

FPGA设计之自动化2014-12-16 3411

-

瞄准工业自动化,嵌入式处理器厂商群集SoC设计“战场”2014-08-13 1008

-

加速工业自动化进展,TI处理器整合PRU2014-07-14 1664

-

流水线操作,应用处理器,应用处理器的结构和原理是什么?2010-03-26 1420

-

利用LabVIEW优化多核处理器环境中的自动化测试应用2010-03-23 2339

-

什么是通用处理器2010-01-12 5213

-

多媒体应用处理器的原理和应用2009-12-01 665

-

罗克韦尔自动化与Intel合作开发工业处理器技术2009-06-12 753

全部0条评论

快来发表一下你的评论吧 !