分享一篇汽车电子产品的EMC整改实例

EMC/EMI设计

描述

EMC是对一个电子工程师能力的一个全面考量,整改过程可能会涉及到结构,软件,硬件,从芯片级,板级到系统级的各个层级,EMC问题中最为常见的就是RE辐射类问题。RE实验的目的是测量产品通过空间传播的辐射骚扰场强,RE实验的依据的标准包括以下:CISPR25,GB18655(国标),ECE-R10.05,欧盟汽车EMC指令2004-104-EC等标准,当然对于各大厂家来说,会根据对产品的要求,在标准的基础上超出标准上限的限值。

解决RE的问题书本上和网上的教程案例很多,但其实对待EMC问题,永远都是多多实践,多多总结,再反过来看书本上,网上教程才能理解的更为深刻。

本文以一篇汽车电子产品的EMC整改实例,归纳总结了一些小技巧供大家参考,希望对大家解决RE或者EMC问题能够提供些许帮助,谢谢。

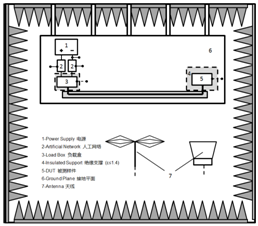

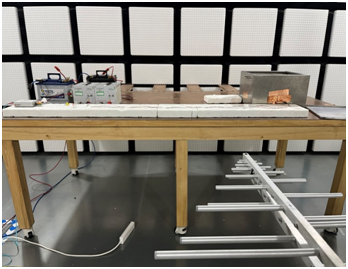

实验布置图:

测试布置图

实验标准:

按照对应主机厂的RE ALSE法标准。

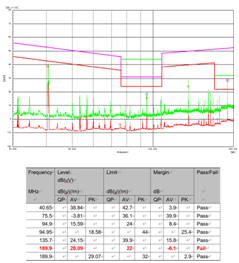

实验现象

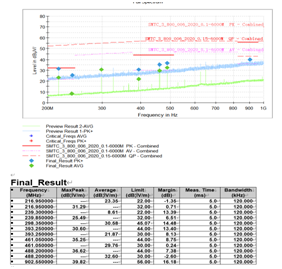

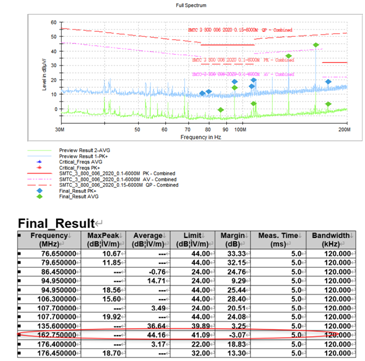

产品在189.8MHz,501.8MHz,244.1MHz,217MHz,176.3MHz,162.7MHz超标最为严重。

超标频点测试数据

结合板子上的主要干扰源,发现以上频点均为13.56MHz的倍频点。

13.56MHz是板子上的天线频率,第一干扰源很容易确认,但是如何解决其引起的倍频,才是难以解决的问题。结合以前经验,按照以下方法逐一排查分析:

1.)通过给产品接口端套入磁环,进而判断该辐射主要是来源于产品本身,还是干扰源通过测试1.7m线束形成的传导耦合;

2.)该产品利用的是13.56MHz的磁场耦合,通过跟供应商沟通,可以将天线接地处理,降低其一部分能量的辐射;

3.)天线部分都有其匹配电路,可以通过LC滤波,滤除其高次谐波,但是电感电容又不能取值太大,太大的电容,电感配对值会影响天线部分的阻抗匹配,影响天线功能;

4.)可以找出天线耦合到PCB上的二次干扰源在哪儿,找到这个干扰源,并进行合理抑制,或许能够解决这个问题;

针对以上分析,我们一一进行验证

首先验证分析1

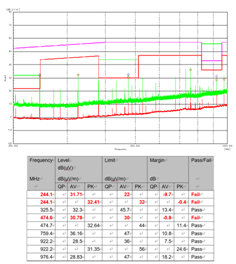

①对产品进行整体屏蔽处理,屏蔽箱用编织带接入大地,测试辐射效果,数据显示(因为时间有限,先仅对30MHz-200MHz验证,因为都是13.56MHz倍频,确认有效果后,接着测试其他频段)可以提升4db左右(观测216MHz频点,因为产品本身读卡存在周期性,测试扫描频点也存在时间性,扫描到对应频点时,产品可能没有在读卡,所以额外出现488MHz频点,对于该频点先不做考量)。

产品屏蔽,线束不做处理

②将测试1米7线束布置很短,产品不做屏蔽处理,这样可以减小线束耦合的环路面积,使得RE能量减小,测试数据发现仍然存在超标点,但是203MHz这个频点之前并未发现,不好判断是效果如何。

产品不做屏蔽,测试线束变短数据

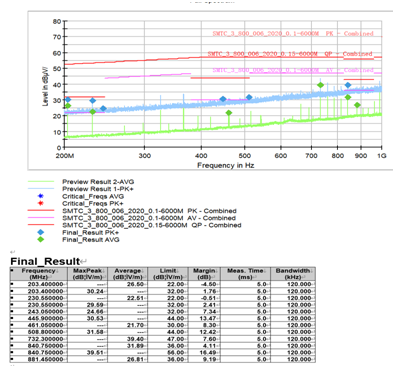

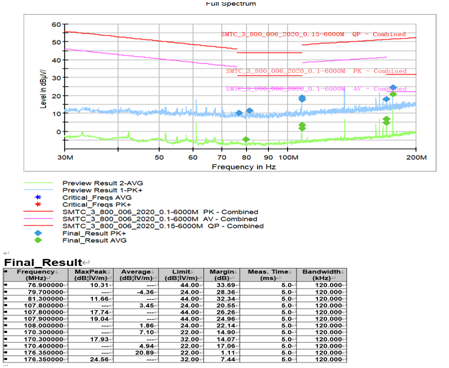

③同时进行产品屏蔽处理和测试线束变短,为防止测试过程中存在的偶然性,经过多次测量,均未发现超标点,截取其中一次测试数据如下:

产品屏蔽,测试线束变短数据

通过对分析1的验证,得出的结论是当给产品进行整体屏蔽同时减小线束耦合面积时,可以通过该频段的实验,但是这又带来问题,减小线束端的耦合,我们可以对产品的电源输入端增加共模电感或者差模磁珠进行验证,但是产品本身的辐射很难快速判断,辐射源可能是天线本身,也可能是天线相关的其他电路。我们先验证分析2。

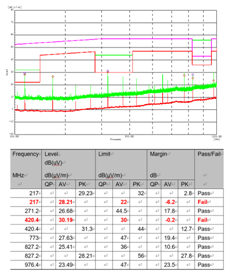

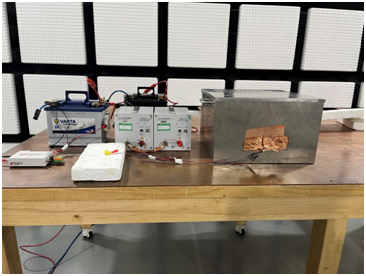

验证分析2

将天线的几何中心接地处理,测试数据如下,发现162.7MHz频点可以下降3db左右,对于辐射还是有改善的,但是还是无法通过测试。其实实验验证到此处,我们下一步需要做的可以是将天线接地和输入端加共模电感/磁珠,结合起来进行验证,但是我们也可以先用频谱分析仪扫描PCB板,看看板子上哪一部分的能量最强,对该区域进行处理,或许也能解决辐射问题,总之,条条大路通罗马,就看怎么选择。

天线的几何中心接地

天线的几何中心接地测试数据

对于分析3,经过验证,增加到一定电容后(300pf)左右,LC截止频率仍然很高,对于1GHz以下频点超标影响很小,我们接着验证分析4.

分析4验证

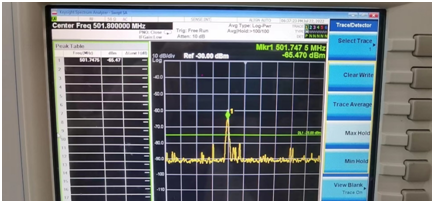

用频谱分析仪扫描PCB板子上超标明显的频点,扫描发现天线匹配电路,电感输入前端各个频点的能量很高,而板子其他部位,包括天线本身辐射能量都要低于匹配电路前端的电感。选取部分超标频点图示:

天线匹配电路输入电感辐射图

PCB板其他区域辐射图

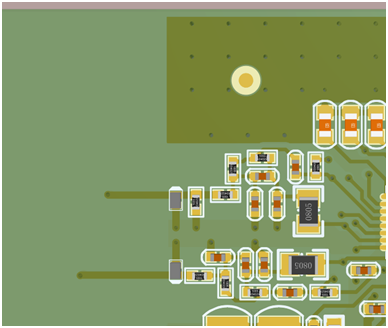

对于该部分电路,我们目前的设计是地挖空处理,这是为了防止天线的能量被地吸收,从而影响天线的性能,但是这样也导致了辐射超标的问题,为了验证是不是这部分引起的RE问题,我们对该区域进行屏蔽罩处理,重新测试数据,发现测试通过。

天线匹配电路屏蔽处理

纵观这次debug整个过程,分析4仅需要重新洗板即可通过实验,整改的成本是最低的,按照正常的整改过程,我们也应该需要进一步结合验证给线束增加共模/差模滤波,同时将天线接地处理这两个措施的效果如何,由于整改时间关系,未对此做进一步验证。

总结

解决EMC的问题也可以归纳为由大到小,由面到点,即先判断RE超标主要因素是来源于线束的耦合传导,还是产品本身,因为如果可以判断出来源于线束的耦合传导,那么我们很快可以通过给接口电路增加共模电感/差模电感,或者电容等方式处理RE问题,简单高效;涉及到产品本身,除了一些明显的干扰源外,我们往往需要借助其他设备,例如频谱分析仪进行定位,定位到干扰源后,还需要再确认是传导耦合,还是辐射耦合,可能需要多花费一些时间。

同时在debug过程中,当发现一到两个措施有效时,我们可以选择将这两个措施结合起来,观察测试效果如何,亦或跟着既定的方法继续验证排查,总之,EMC debug要多尝试,努力寻找一个经济成本最优的方案出来。

审核编辑:刘清

-

电子产品EMC整改:从源头到终端的系统化技术路径2025-12-30 390

-

2026年度一场《汽车电子产品EMC设计与整改案例分析》公开课来袭!2025-12-27 46

-

EMC电池测试整改:确保电子产品电磁兼容性的方案2025-03-25 965

-

EMC与EMI测试整改:打造电磁兼容性的电子产品之路2024-05-23 1136

-

深圳比创达电子|EMC测试整改:打造电磁兼容强劲产品的必经之路.2024-04-26 3121

-

制约我国汽车电子产品发展的因素是什么?2021-05-19 2179

-

电子产品EMC:汽车电源7637-2设计与测试2020-05-30 3868

-

【活动】如何做电子产品EMC设计评估?参与免费送课!2020-05-12 4847

-

汽车电子产品环境可靠性测试2016-12-26 3725

-

电子产品认证检测中的EMC问题及其分析(77页PPT)2015-08-24 38294

-

《汽车电子产品整改与设计》高级研讨会2013-09-23 3587

-

对汽车电子产品的测试和测量2012-09-28 8086

-

浅谈汽车电子产品的七大特点2012-08-31 6211

-

汽车电子产品抗干扰整改案例2008-06-26 17730

全部0条评论

快来发表一下你的评论吧 !