浅谈台积电3D Fabric 技术三大步

描述

3D Fabric将释放下一代创新力量。

作者:半导体产业纵横编辑部

全文引自2022世界半导体大会台积电专场论坛

在世界半导体大会上,台积电资深技术经理郑茂朋分享了台积电目前的先进封装前沿技术。

台积电 3D Fabric 技术

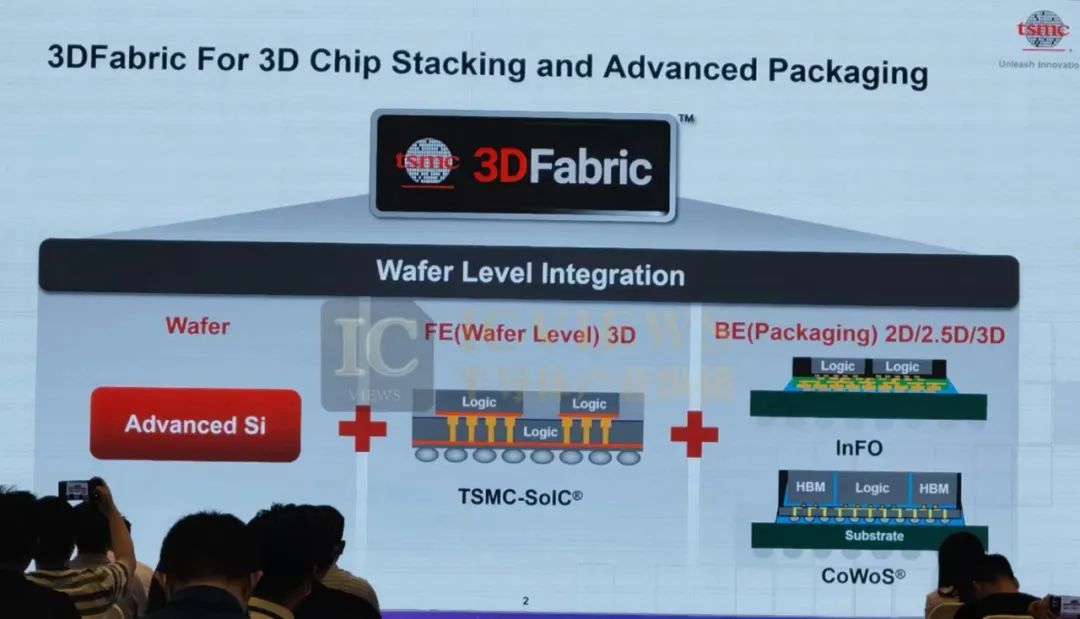

3D Fabric是台积电Chiplet的方案,其分为三大步。

第一步是用先进制造,其中重要的是如何去切割,形成标准的集成电路。 第二步是使用wafer level 3D封装将其变成标准的集成电路。wafer level 3D封装并非在基板上实现,而是通过制造手段实现。这其实是Chiplet的典型方案,当芯片过于大时,需要将其切割成小芯片。台积电的SoIC是由三颗chiplet的小方案组成的。

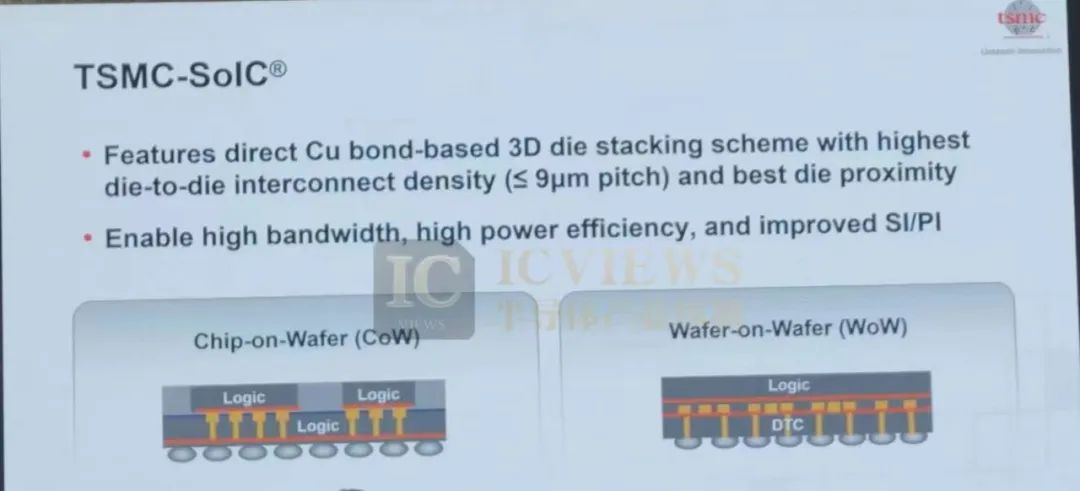

第三步是BE(封装)2D/2.5D/3D,封装就是通过基板的连线结合起来。 3D Fabric 在HPC中的应用 HPC的高性能运算主要指网络产品、网络通讯产品、CPU、GPU以及使用AI的产品,都属于HPC的范畴。这其中会用到一些比较大的芯片。正常芯片最大尺寸是800平方毫米,但GPU和AI芯片需要无线增大时,就需要切割。 在HPC中,台积电会用到3D Chip Stacking。这其中包括两种方式,一种方式是 Chip on wafer,就是将切割后的Chip直接放在晶圆上;另一种方式是wafer on wafer,就是直接将晶圆和晶圆对接。完成这一阶段后,台积电将进行3D封装。 台积电的3D封装有很多种类。第一种,如果是高密度的互连。芯片需要和基板相连则会使用silicon imterposer,直接使用晶圆作为中介层,进行高密度的连接。第二种,如果两个Die之间并非高密度互连,可能使用CoWoS-R或者InFo-2D的RDL。第三种,CoWoS-L处于以上两种情况中间,在Die和Die之间高密度互联区域中存在一个Local silicon。 台积电的SoIC封装方式,主要提供高密度互连。一种方式是chipon wafer,也就是logic与logic之间通过一个bonding直接连接,这其中尺寸可以达到9微米。另外一种wafer on wafer,也是提供了最小9个micron。目前,甚至在一些摄像头上,台积电已经提供了小于1个micron的bonding尺寸。这种连接方式可以实现高带宽、节省能耗、提高SI/PI性能。

从SoIC目前的技术指标看,在逻辑制程上,台积电2022年已经达到3nm节点。 SoIC-CoW可以做到Top Die和Bondom Die达到7nm,bondingpitch达到9个micron,未来的技术指标将做到5nm和5nm的堆叠,6 micron的尺寸。 SoIC-WoW,达到7nm、0.13DTC。AMD发布的EPYC Processor中,将最占面积的缓存进行了3层的堆叠。 其他的封装方案还有,CoWoS和InFo。 CoWoS方案上,台积电推出了三种方式,CoWoS-S、CoWoS-R、CoWoS-L。CoWoS-S是CoWoS中台积电能够提供的最成熟技术,已经有11年的研究经验。另外,一些低成本的方案可以使用CoWoS-R,也即不使用晶圆的制造,而是通过有机物的RDL制造。

InFo方案上,台积电推出了两种方式,InFO-oS、InFO-M。InFo方案与大多数封装厂的Fan-Out类似,主要区别在于去掉了silicon imterposer,使用一些RDL层进行串连。

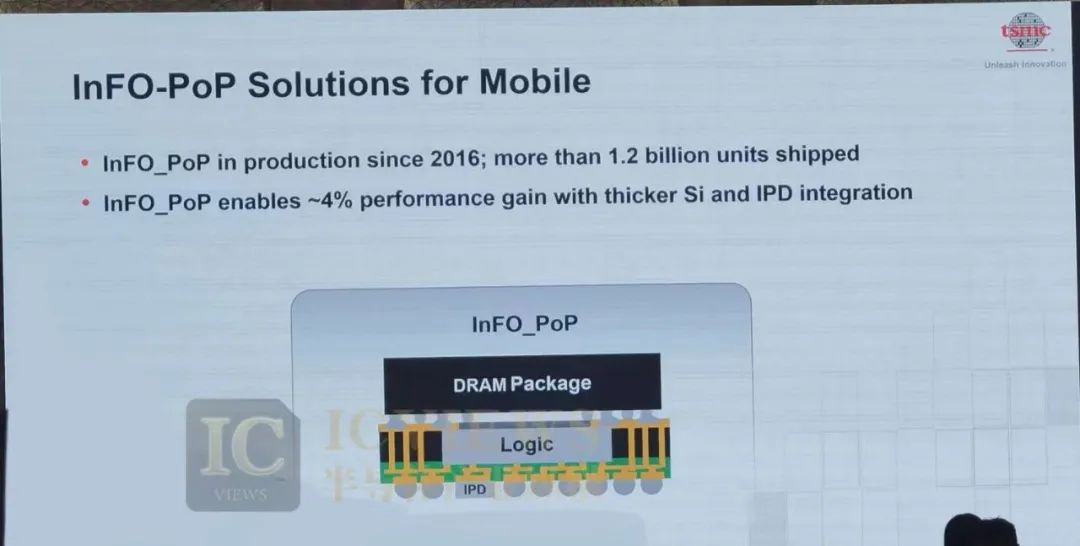

3D Fabric在手机应用

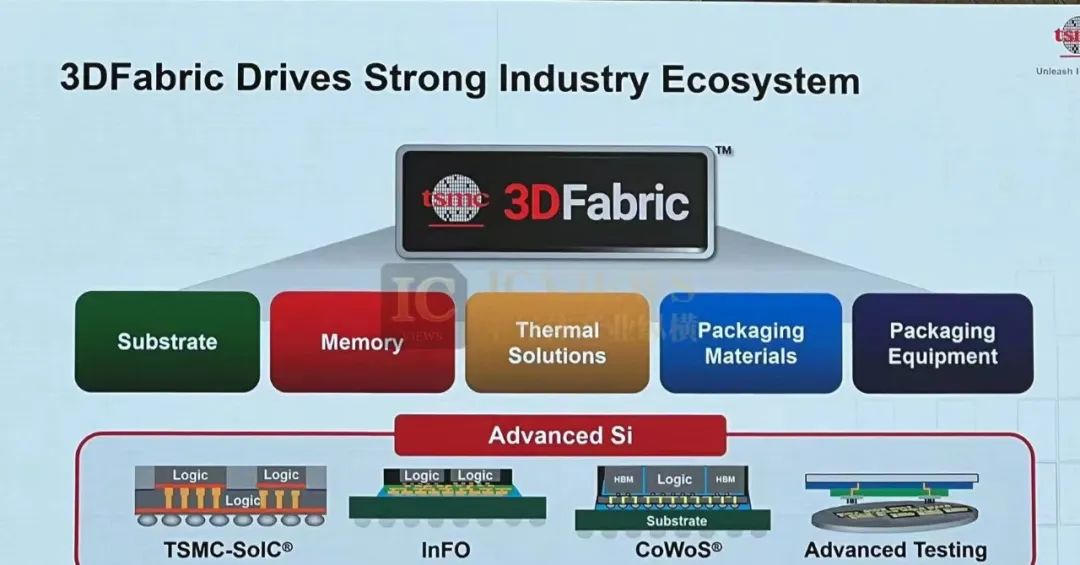

InFO-POP在2016年应用于手机产品,出货量达到1.2亿。现在,InFO-POP达到了4%的提升,并且其中的silicon较薄,更适用于手机。 苹果A系列的chip大概在100平方毫米,安卓也基本在120平方毫米,如果芯片需要的功能越来越多,相应芯片会越来越大。台积电对此的应对方式是使用InFO-3D,将一颗芯片拆分为SoC 1和SoC 2,通过封装的形式堆叠,做成相同性能的一颗芯片,使得芯片尺寸明显变小。 3D Fabric的制造及生态链 目前,台积电已经建成了全球第一个全自动化3D Fabric工厂,可以提供:SoIC、CoWoS、InFO、先进测试的服务。

3D Fabric仍然面临着很大挑战,对此台积电也在努力推动工业的生态链建设,包括基板、存储、散热、封装材料、设备的合作协同。

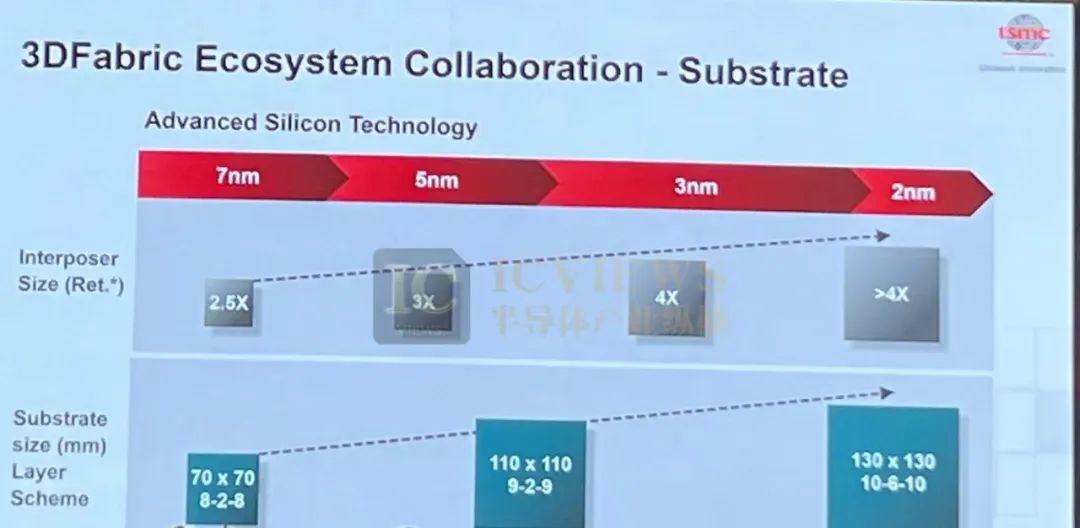

基板的尺寸大多停留在70*70mm的尺寸,但随着芯片的逐渐增大,需要的基板尺寸也更大。如何驱动基板厂商与台积电一起进一步改进,是其中一个问题。 在HPC方面,台积电将与HBM供应商密切合作,定义和调整HBM3规范,以实现与CoWoS技术的强大工艺集成。 在手机方面,将InFo-POP兼容性从定制扩展到主流LPDDR,实现InFO-B工艺与LPDDR组件的集成。 3D Fabric将释放下一代创新力量。

编辑:黄飞

-

台积电成立3D Fabric联盟 ARM、美光、新思等19个合作伙伴加入2022-10-27 2309

-

5G手机全球出货量首次超过4G手机 台积电3D Fabric技术如何助力手机和HPC芯片2022-09-20 3150

-

台积电开发SoIC新3D封装技术,中芯国际考虑跟随2020-12-30 3448

-

台积电在台湾进行3D硅片制造技术研发2020-11-27 2000

-

谷歌和AMD帮助台积电测试和验证3D堆栈封装技术,有望成为首批客户2020-11-23 2431

-

台积电3D封装芯片计划2020年量产2020-11-20 3091

-

继Intel、台积电推出3D芯片封装后,三星宣布新一代3D芯片技术2020-10-10 2142

-

台积电将增加到6座芯片封测工厂 新投产两座3D Fabric 封装技术工厂2020-09-25 882

-

三星加速部署3D晶圆封装技术,有望明年与台积电竞争2020-08-25 3385

-

台积电揭露3D IC封装技术成功,揭开半导体制程的新世代2019-05-27 3597

-

台积电完成全球首颗3D IC封装技术2019-05-04 3098

-

台积电完成全球首颗3D IC封装技术,有望持续独揽苹果大单2019-04-23 3526

-

台积电尝试发展3D晶片堆叠技术2011-12-16 1047

全部0条评论

快来发表一下你的评论吧 !