一文详解CameraLink标准

电子说

描述

CameraLink标准解读

1. LVDS信号:Low Voltage Differential Signal低压差分信号。低功耗、低误码率、低串扰和低辐射等特点,可以在PCB上传输,也可以用平衡电缆传输。差分终端电阻是100欧姆,差模电压(摆幅)在247mV到454mV之间,共模电压在1.125V到1.375V之间;

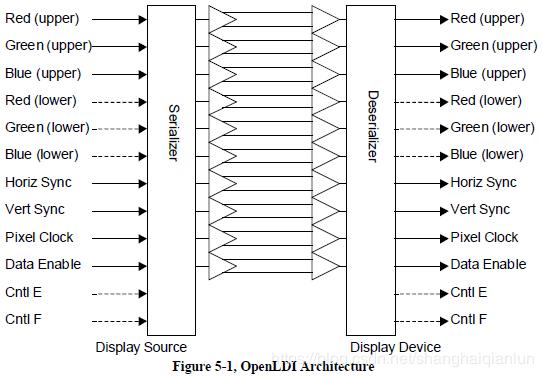

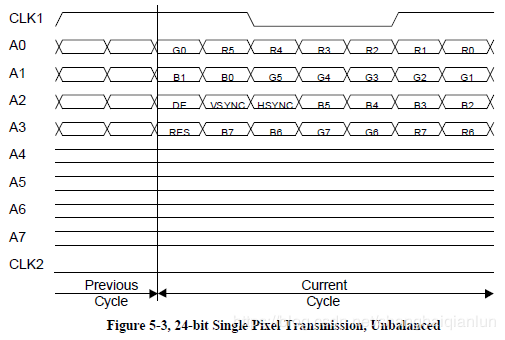

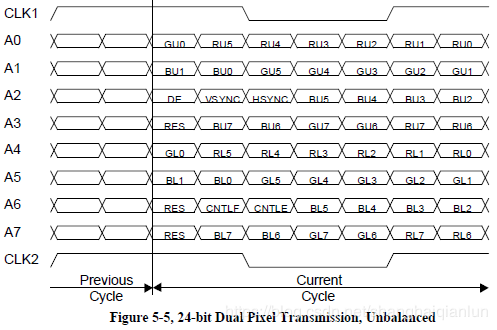

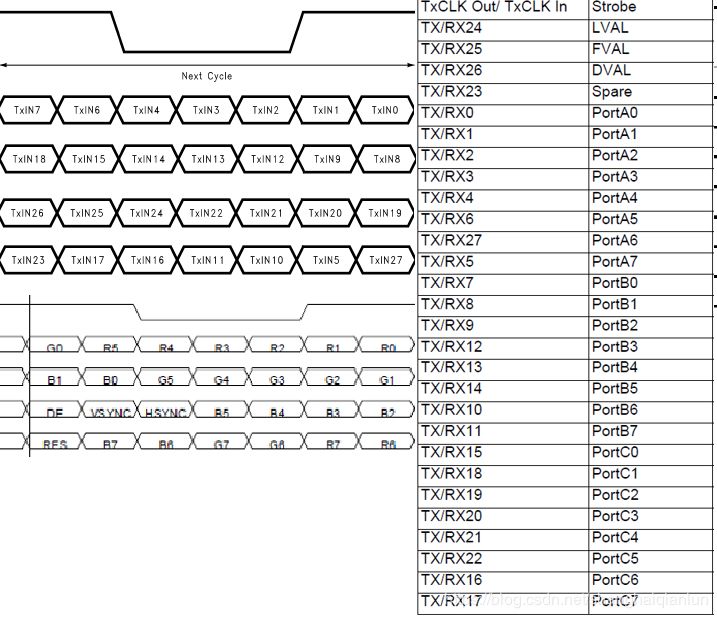

2. CemraLink是如何传输数字视频数据:以24bit单双像素非平衡传输方式为例:

图1 一个时钟周期传输的位的定义。

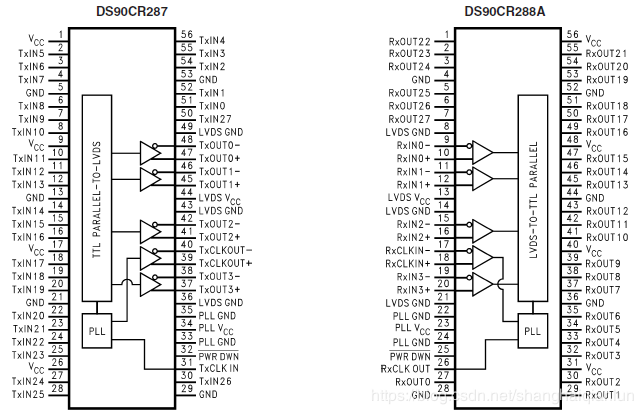

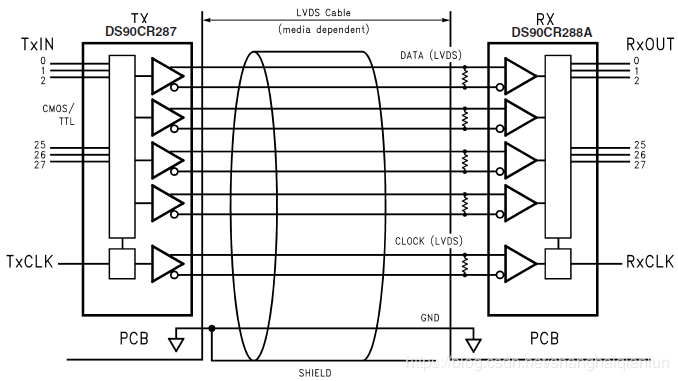

硬件支持,以288和287为例:

配置(Configuration):最新的CameraLink规定了5种配置:

Lite:支持10bit,1个电缆连接器

Base:支持24bit,1个电缆连接器

Medium:支持48bit,2个电缆连接器

Full:支持64bit,2个电缆连接器

80 Bit。支持80bit,2个电缆连接器

1. 端口(Port):8bit宽。是从信号连接的角度来说的,1个端口可传输8bit的数,但是并没有规定具体是什么数:如是Red、Green、Blue、Luma等。 (5) Tap:直到CameraLink 2.0才引入了Tap的概念,但是并没有给出定义,而仅仅是直接就用起了TAP,通过仔细看标准,我认为:Tap表示一个类型的数据,如:Red数据、或Green数据、或Blue数据、或是偶像素数据、或是奇像素数据。比如:

1. 用一个Base配置来传输24bit的RGB,RGB的每个数据是8bit,那么我们就说是3个TAP,每个TAP是8bit。

2. 如果我们用一个Medium配置来传输双像素RGB,RGB数据是8bit,那么我们就说是6个TAP,每个TAP是8bit。

3. 如果我们用Lite配置来传输黑白图像,亮度用10bit数来表示,那么,我们说1个TAP,每个TAP是10bit。

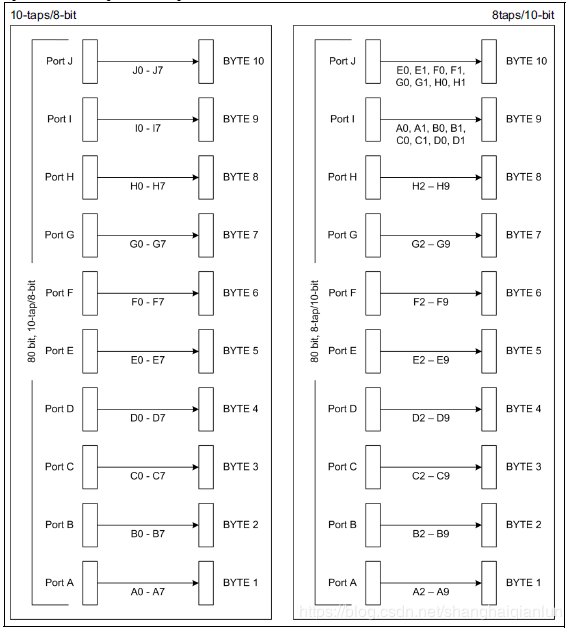

4. 再比如80bit模式的10tap8bit,和8tap10bit,如下图

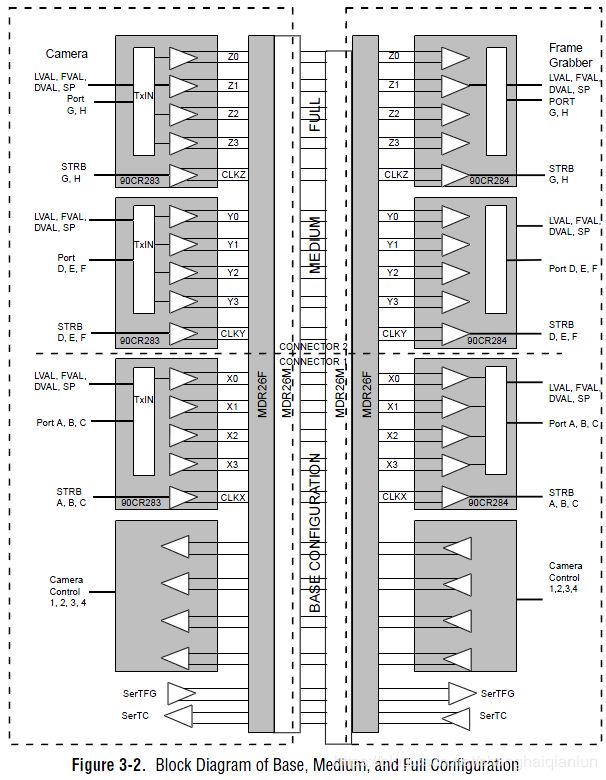

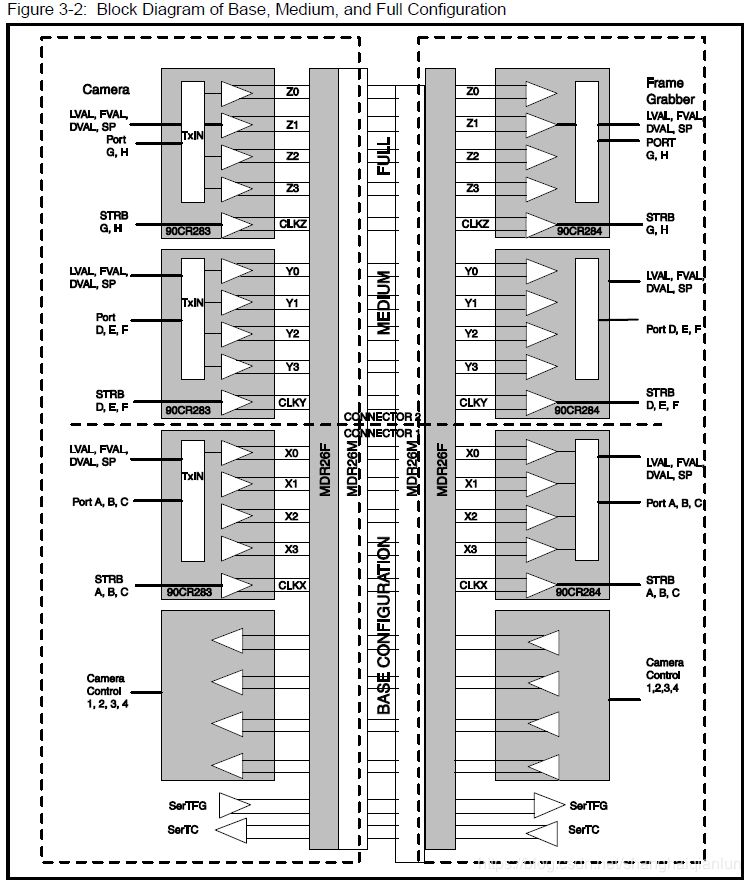

2000年版的Camera Link标准:

Camera Link有3个配置,这主要是因为单通道链路芯片限制了28bit,而某些相机可能要传输更大的图像。

1. Base(基本):单通道连接芯片,1个电缆

2. Medium(中等):2通道连接芯片,2个电缆连接器

3. Full(完全):3个通道连接芯片,2个电缆连接器。

2012年发布的Camera Link V2.0对原先版本做了扩展:

3个配置:

1. Lite/Base:1个通道连接芯片,1个电缆连接器

2. Medium:2个通道连接芯片,2个电缆连接器

3. Full/80bit:3个通道连接芯片,2个电缆连接器

CameraLink标准应该对如下一些内容作出明确定义:

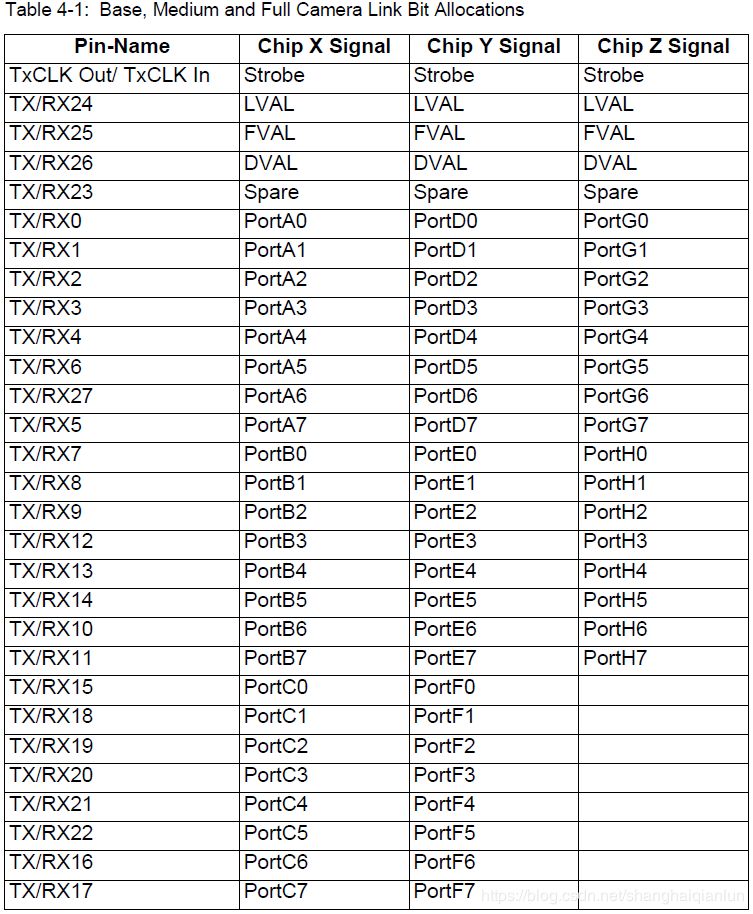

我们知道要传输的图像数据是由一个或多个Tap组成的,先要定义这些Tap的每一位是如何分配在Port上的,这就是第2.2.2.1节定义的位的分配(Bit Assignment)。

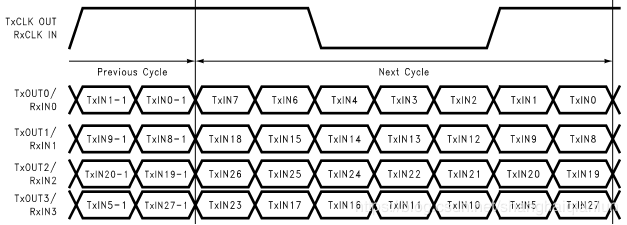

然后要定义Port的每一位及LVAL、FVAL、FVAL、SPARE处于LVDS时钟周期的哪个相位,也就是是Port每一位与收发器的RX/Tx脚位之间的关系。这个问题在2.2.2.2节位的位置(Bit Allocation)中定义。

标准还要定义每个Port位于哪个通道连接,或者说哪个芯片上,或者说是在X连接通道上,还是Y、Z连接通道上?这一点由第2.2.2.3节的配置的框图来定义。

1. Bit Assignment

其它Bit assigment可查标准。

2. Bit Allocation

3. Configure

-

采用LVDS电平标准的Cameralink传输2019-05-30 3401

-

基于ZYNQ的CameraLink图像采集与边缘检测开发详解2020-09-17 1566

-

一文详解蓝牙模块原理与结构2020-11-26 5378

-

一文详解精密封装技术2022-12-30 2603

-

一文详解分立元件门电路2023-03-27 4954

-

一文详解pcb和smt的区别2023-10-08 5864

-

一文详解pcb涨缩标准是多少2023-10-12 6685

-

一文详解pcb地孔的作用2023-10-30 3112

-

一文详解pcb不良分析2023-11-29 2281

-

一文详解PCB半成品类型2023-12-11 3467

-

一文详解pcb的msl等级2023-12-13 16751

-

一文详解pcb微带线设计2023-12-14 6691

-

一文详解pcb线路板的ipc标准2023-12-15 12996

-

一文详解pcb的组成和作用2023-12-18 3753

-

一文详解pcb回流焊温度选择与调整2023-12-29 3430

全部0条评论

快来发表一下你的评论吧 !