【Makefile】C文件包含的头文件修改,但不重新编译?

【Makefile】C文件包含的头文件修改,但不重新编译?

描述

在上一篇 《【Linux + Makefile】十分钟教你学会Makefile的FORCE 》文章的最后,笔者就FORCE的用法在一个示例工程中使用,提出了一个问题:为何build_info.h每次都是新生成的(有修改过),而main.c又是有include “build-info.h”,但main.c却不是每次都重新编译呢?这个到底是不是违反了Makefile的基本规则呢?本文将给你答案,通过阅读本文,你将了解到以下内容:

- 如何保证在C文件中包含的头文件修改了的时候,C文件每次都会被重新编译?

为了更好地展示上诉描述的问题,我们将之前的示例工程稍微复杂化一点点:

整个工程有3个.c文件,a.c/b.c/main.c,其中main.c会调用a.c/b.c中的两个接口,同时main.c会include头文件build_info.h;这个build_info.h每次编译都会重新生成,按照我们之前的写法,我们Makefile可能就是这样:

SHELL = /bin/bash #指定shell使用/bin/bash,否则echo -e可能会出问题

ECHO = echo

BIN = test

BUILG_INFO_H = build_info.h

SRC-C-y += a.c

SRC-C-y += b.c

SRC-C-y += main.c

SRC-O = $(patsubst %.c, $(O)%.o, $(SRC-C-y))

all: gen_build_info $(BIN)

clean:

rm -rf $(SRC-O) $(BIN) $(BUILG_INFO_H)

$(BIN) : $(SRC-O)

gcc -o $(O)"$@" $(SRC-O)

%.o : %.c

gcc -c "$<" -o "$@"

gen_build_info: $(BUILG_INFO_H)

$(BUILG_INFO_H): FORCE #强制生成build_info.h

@$(RM) $@

@$(ECHO) ' GEN $@'

@$(ECHO) -e " #ifndef __BUILD_INFO_H__\n"\

"#define __BUILD_INFO_H__\n"\

"#define APP_TIME \"`date "+%Y-%m-%d %H:%M:%S"`\"\n"\

"#endif" > $@

FORCE:

.PHONY: FORCE

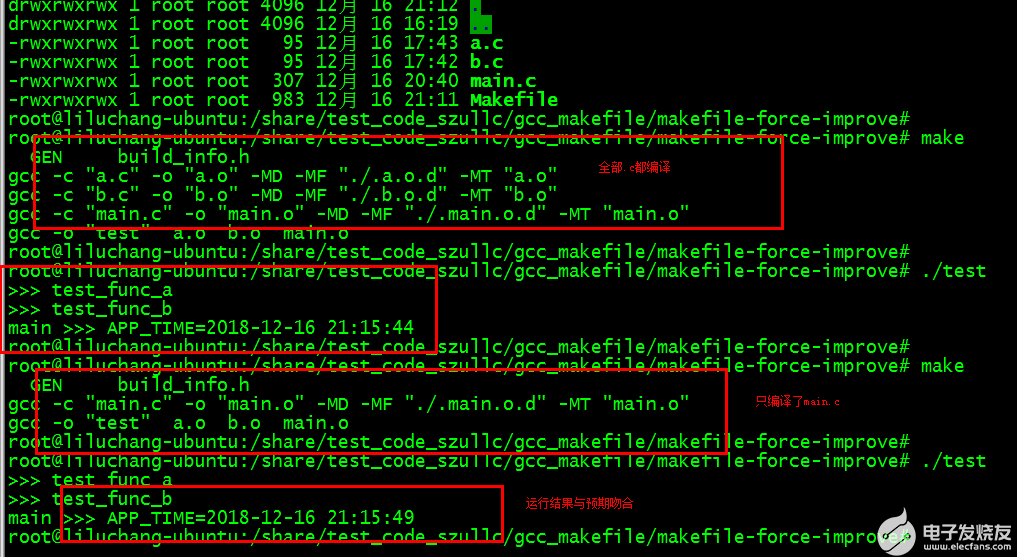

执行make,我们会发现,跟我们的预期不一样:它虽然会每次都生成build_info.h,但是main.c包含了build_info.h却不会每次都重新编译。这个问题发生的原因,我们来分析下:

在我们的Makefile规则中,main.o只依赖于main.c (Makefile 第18-19行),而在第二次执行make的时候,main.c显然并没有被修改,所以main.o不会重新生成,自然可执行文件就不会重新生成。这里的问题根源在于,main.c它是依赖于build_info.h的,而这个依赖关系并没有体现在Makefile中,所以整个编译流程达不到我们的预期想法。我们尝试下,将main.c的依赖头文件也写入到Makefile中,怎么实现呢?

恰好,GCC给了我们强大的支持,它有个非常有用的选项 -MD -MF,它可以在生成一个.o的同时也生成它的依赖文件列表,修改后的Makefile如下所示:

SHELL = /bin/bash #指定shell使用/bin/bash,否则echo -e可能会出问题

ECHO = echo

BIN = test

BUILG_INFO_H = build_info.h

SRC-C-y += a.c

SRC-C-y += b.c

SRC-C-y += main.c

SRC-O = $(patsubst %.c, $(O)%.o, $(SRC-C-y))

SRC-C-DEPS = $(patsubst %.c, $(O).%.o.d, $(SRC-C-y)) ## 由 a.c ==> .a.o.d

all: gen_build_info $(BIN)

clean:

rm -rf $(SRC-O) $(BIN) $(BUILG_INFO_H) $(SRC-C-DEPS)

$(BIN) : $(SRC-O)

gcc -o $(O)"$@" $(SRC-O)

%.o : %.c

# 生成xxx.o的时候,同时生成它的依赖列表,放在文件.xxx.o.d中

gcc -c "$<" -o "$@" -MD -MF "$(dir $@).$(notdir $@).d" -MT "$@"

gen_build_info: $(BUILG_INFO_H)

$(BUILG_INFO_H): FORCE #强制生成build_info.h

@$(RM) $@

@$(ECHO) ' GEN $@'

@$(ECHO) -e " #ifndef __BUILD_INFO_H__\n"\

"#define __BUILD_INFO_H__\n"\

"#define APP_TIME \"`date "+%Y-%m-%d %H:%M:%S"`\"\n"\

"#endif" > $@

FORCE:

.PHONY: FORCE

# 在Makefile末尾强制包含这些依赖文件

-include $(SRC-C-DEPS)

测试结果如下所示:

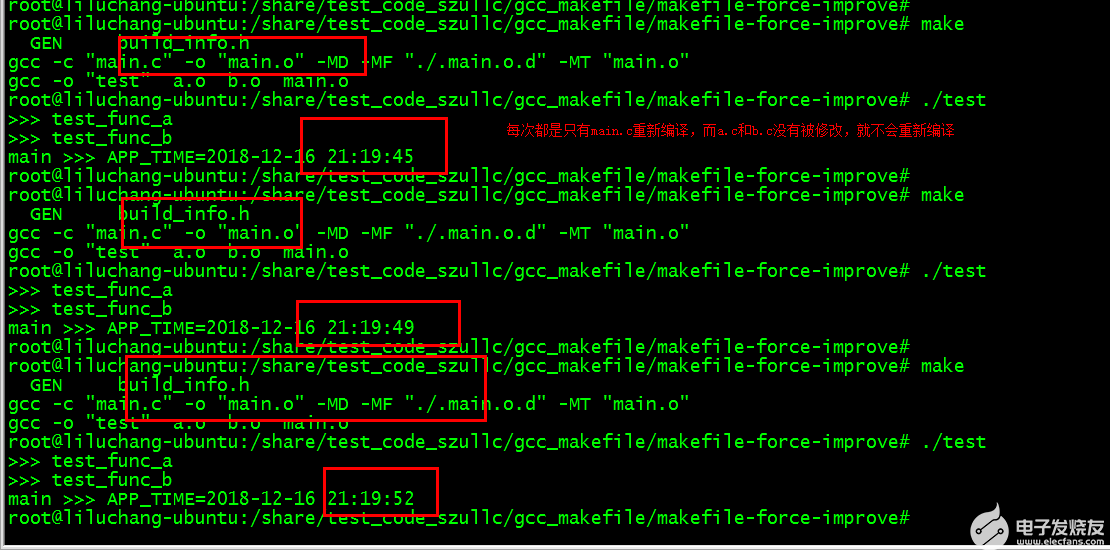

再次执行make,多试几次,一样的结果。

由上可知,经过改造后的Makefile是实现了我们的需求,每次build_info.h重新生成,导致main.c包含了build_info.h也会重新编译,而a.c和b.c没有被修改,所以在未执行make clean的情况下,a.c和b.c是不会被重新编译的,每次都是仅仅main.c被再次编译,从而重新生成新的test可执行文件。这样就是已经达到了【当C文件包含的头文件修改了的时候,C文件必须重新编译】的目的。

以上就是关于Makefile的高阶用法,基本满足了我们日常工程实践的需求。如果你对该Makefile有疑问,欢迎在评论席提出你的疑问,博主很乐意为你解答。

延伸阅读:

【Linux + Makefile】十分钟教你学会Makefile的FORCE

审核编辑:汤梓红

-

C语言中的头文件能不能重复包含2024-11-26 1273

-

Makefile可以做什么?Makefile的基本格式2024-01-25 1539

-

C语言必备知识头文件包含2023-12-01 3399

-

Makefile是如何编译代码文件的?2023-05-18 5943

-

keil添加了头文件仍然报找不到头文件的原因2021-11-21 8423

-

芯片设计中的Makefile简单教程2020-12-24 1659

-

C语言的头文件组织与包含原则2020-11-14 4400

-

Linux内核的Makefile、Kconfig和.config文件2020-11-12 3952

-

无法重新编译和重新构建Video Demo的任何文件2019-09-12 1587

-

如何实现Makefile每次都重新编译指定文件2019-08-20 5908

-

关于编译后头文件的包含问题2018-04-06 3190

-

如何写Makefile编译汇编和C文件2017-11-24 16341

-

如何在C++代码中使用C头文件2017-10-19 2953

-

F28035实现双电机控制的程序,包含C文件、关键头文件和CMD2015-11-02 1867

全部0条评论

快来发表一下你的评论吧 !