线性稳压器和开关稳压器比较 FPGA电源隔离指南

电源/新能源

描述

引言:面向收发器 (SERDES) FPGA 的PDN设计对电源有严格的要求,需要干净的电压源。虽然低功耗应用中通常采用低泄漏 (LDO) 线性稳压器,但这一方法必须仔细的隔离电压源。电路板设计人员在这些应用中必须全面考虑电压源隔离和电压源共享问题。隔离度较高时,会增加稳压器的数量,而太多的共享则会影响性能。如果 PDN 稳压不够,那么,收发器的性能会受到很大影响。因此,正确的选择稳压器和电源配置对于实现最佳收发器性能非常重要。

在很多 PDN 设计中,创新的开关稳压器相对于线性稳压器有很大的优势。而且,FPGA收发器技术不断发展,在 FPGA 中实现稳压器,从而不再需要使用外部稳压器。本文档在以下方面为稳压器选择和实现提供指南:

线性稳压器和开关稳压器比较

FPGA 电源隔离指南

推荐的单片封装解决方案

PDN 性能实例

1.线性稳压器和开关稳压器比较

传统上,电路板设计人员在低电流、低噪声和电路板空间有限的情况下使用线性稳压器,而使用开关稳压器来提高功率,增强效率。这种指导原则在很多情况下是适用的,但是,随着开关稳压器设计的进步,现在它在很多应用中可以替换线性稳压器。这一部分阐述线性稳压器和开关稳压器之间的不同,提供每一类稳压器的实例,介绍开关稳压器技术的进步。 线性稳压器具有较低的输出噪声,比较容易实现,需要较少的支持元件,能够很快的响应负载变化,而且成本低于开关稳压器。但是,随着功率需求的增大,线性稳压器无法有效的输出大电流。典型的开关稳压器能够有效的输出大电流,但通常需要多个支持元件,会带来噪声代价。开关稳压器设计不断发展,现在能够支持开关稳压器来替代线性稳压器。下面会详细介绍这一新技术的各方面。

1.1 开关稳压器设计的发展

在过去十年中,开关稳压器经历了很多关键变革。这包括最开始的 DC/DC 变压器 IC、外部电源 FET,以及电感等很多外部支持元件。后来是微型开关电路,这些电路在微型电路板上实现,采用了 PCB 标准接口。然后发展到 DC/DC 变压器和 MOSFETS 集成到一个封装 ( 单片转换开关 ) 中,只有电感还保留在封装之外。最近的发展则是单封装解决方案。下面详细介绍这些发展过程。

微型 PCB 上的微型电路解决方案

微型 PCB 上的微型电路有两个与 DC/DC 变压器模块相关的标准;负载点联盟 (POLA) 和分布式电源开放标准联盟 (DOSA)。每一标准都定义了引脚输出接口、标准封装大小,以及标准电接口规范和控制。这些技术的例子有 Artesyn TM Technologies PTH12060DC/DC 变压器 (POLA 标准)、Tyco Electronics ATA010A0X3-SR 电源模块 (DOSA 标准)。它们都需要很少的外部支持元件,引脚区面积在 1.1X0.7 英寸左右。这些模块有助于减小引脚区面积,优化与开关稳压器电路相关的杂散效应,如图 1 所示。

图 1. 电源模块,POLA 和 DOSA 标准

单片封装解决方案

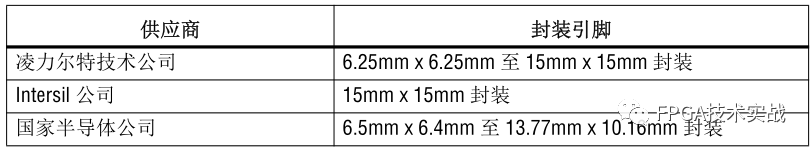

一些供应商现在提供开关稳压器,在一个封装中集成了所有电源供电元件,例如凌力尔特公司的Module 系列、Intersil 公司的电源模块系列,以及国家半导体公司的简单开关电源模块系列等,如图 2 所示。

图 2. 单片封装解决方案

例如,凌力尔特公司的 Module 采用与开关稳压器电路相关的所有元件,将其封装在一个基底上。DC/DC 变压器、MOSFET、电感等主要模块位于独立的基底上,彼此之间相互连接。与 POLA 和 DOSA 模块相比,这一技术更优化,进一步减小了引脚区面积。表 1对比了每一封装的引脚区面积。

表 1. 封装引脚区对比

2.FPGA 电源隔离指南

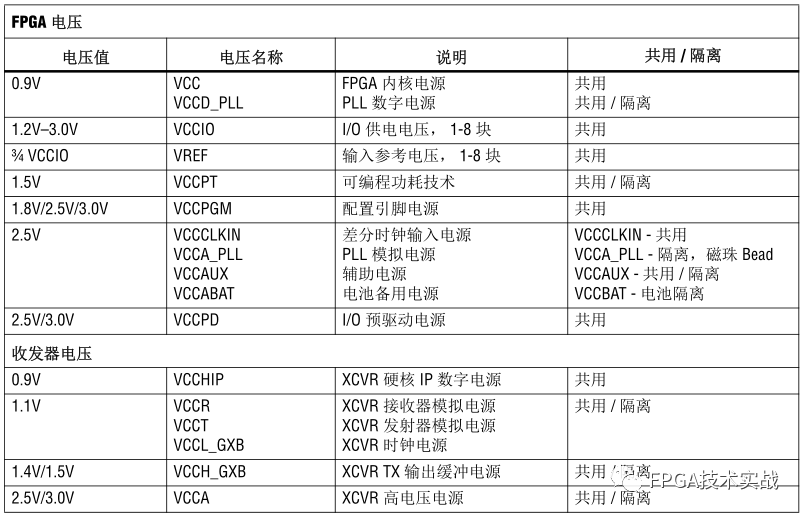

典型的 FPGA 器件含有很多电源线,甚至需要更多的电源线对噪声敏感的 SERDES 收发器进行供电。例如,表 2 显示了所推荐的 Altera 收发器 Stratix IV GX FPGA 器件电源线隔离方案。虽然这一 FPGA 中有很多电源线,但是,取决于具体设计,某些电源线共用了同一稳压器。然而,由于噪声和性能问题,需要对这些电源线进行隔离。设计人员必须严格按照生产商的建议进行设计,以满足电源要求。一些对噪声敏感的电路需要低噪声电源。如果在关键区域不能提供干净的电源,那么将影响抖动发生和 PLL功能。

表 2.Stratix IV GX FPGA 中的电源线隔离实例

2.1 铁氧体磁珠滤波

您可以使用铁氧体磁珠作为另一种隔离方式,帮助克服设计高速 FPGA 的高效 PDN 和多条电源线所面临的问题。可能需要多个稳压器才能隔离关键区域的敏感电源。但是,通过使用铁氧体磁珠,多条电源线可以共用同一稳压器,同时保持与其他电源平面的隔离。低 Q 铁氧体磁珠在很宽的高频范围内都具有高阻抗特性,非常适合实现低通噪声滤波器。设计人员应避免铁氧体磁珠常见的不利影响,例如,电压振铃和反共振等。

2.2 去耦合分析

去耦合设计是 PDN 的关键组成。一般的去耦合方法无法满足高速 FPGA PDN 的要求。您可以使用 Altera 的 PDN 工具进行大量的分析,实现精细的去耦合设计。PDN 工具分析每一电压平面,在以下因素基础上开发去耦合设计:

分布电感

电容装配和电感

BGA 和电感

平面电容

稳压器类型

分析中包括了电源线的所有元件,支持设计人员准确的去耦合电压平面。

3.推荐的单片封装解决方案

凌力尔特技术公司、国家半导体公司以及 Intersil 公司提供单片封装解决方案,在封装中集成了 DC/DC 控制器、电感和电源 MOSFET。供应商一般会为测试各种类型的稳压器提供评估板。Altera 建议您在进行选择之前使用这类电路板来评估所需电源的性能。

3.1 凌力尔特技术公司(ADI)

凌力尔特技术公司的 Module 电源是高速收发器 PDN 设计解决方案。这些集成开关电源能够提供高效的大电流解决方案,保证与传统开关稳压器一样具有较低的输出电压波纹以及较低的开关噪声。利用电流模式体系结构,可以在输出端增加额外的电容,降低波纹,而且不会影响电源的稳定性。在一个封装中集成电源元件能够有效的控制杂散电容和电感,从而降低了电源的 EMI 和开关噪声。下面重点解释了为什么这些电源适用于高速收发器:

小外形封装

紧密耦合负载 / 线性稳压

非常低的输出波纹

13×C/W 至 15×C/W 热阻

多路输出器件

作为单片 IC 进行测试 / 特性测量

不会有电源周期失败问题

支持各种 I/O 电平

支持各种输出电流电平

与 LDO 设计一样简单

3.2 国家半导体公司

国家半导体公司的 SIMPLE SWITCHER 电源模块是高速收发器和其他噪声敏感信号通路IC 的电源解决方案。这些模块为提高散热性能和可靠性而采用了单片露底封装技术。这些模块集成了屏蔽电感和关键的信号通路控制电路,减小了杂散电容和走线电感。模块实现了高效的同步开关稳压器,以及简单的线性稳压器。开关单元全部置入封装中,这些器件具有较低的 EMI 性能。国家半导体公司电源模块还在每一系列的电流选项上提供引脚至引脚兼容功能,表明只需要一种设计和布板就能够支持六种不同的电源。

3.3 Intersil 公司

Intersil 公司的 ISL8200M 是大功率电流共享 DC/DC 电源模块,适用于数据通信、电信和 FPGA 应用。获得专利的多相位工作电流共享技术减小了波纹电流,降低了复杂度。这种稳压器的并行配置功能能够提供 60 安培的电流。ISL8200M 的散热增强紧凑 QFN 封装能够工作在全负载和过温状态下,不需要强制空气散热。

4.PDN 性能实例

该部分介绍 PDN 噪声对抖动分量的影响,然后是 PDN 对 Altera Stratix IV GX 器件收发器性能影响的测试案例,它使用了各种 PDN 配置。

4.1 受影响和不受影响的抖动分量

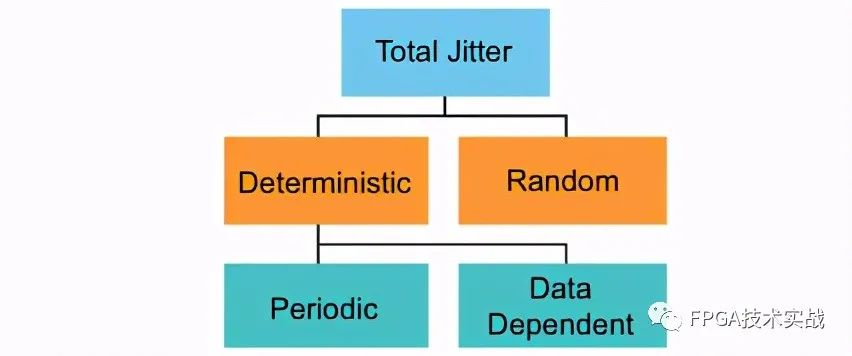

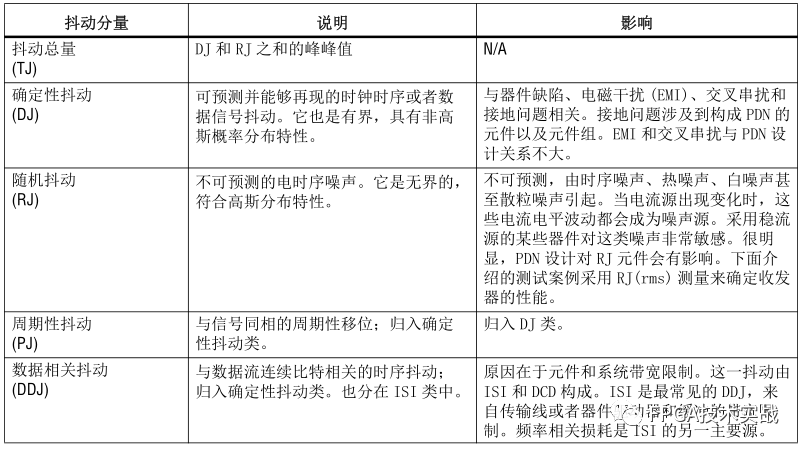

PDN 噪声对抖动分量有较大的影响。图 3 解释了表 3 中的各种抖动分量

图 3. 抖动树 为确定 PDN 设计中受影响的抖动分量,根据其产生原因来定义每一抖动分量。例如,当周期性抖动 (PJ) 具有正弦属性时,它通常与数据码型干扰以及电源波动相关。PDN缺陷会影响 PJ。例如,欠额稳压器会成为电源波动的原因。耦合较差的设计会导致电压下陷。表 3 详细介绍了 PDN 噪声对抖动分量的影响。

表 3. 噪声对抖动分量的影响

4.2 收发器性能试验

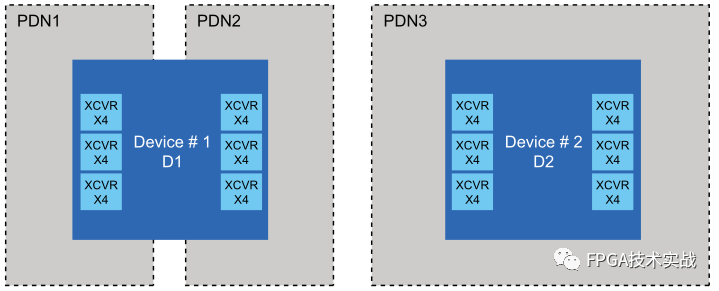

下面的试验使用了两块 Stratix IV GX (EP4SGX230KF40C2) 测试板来测量收发器在不同 PDN 配置时的性能。收发器位于器件的每一侧,如图 4 所示。

图 4.Altera 电源共用电路板图 1 号器件在设计上每一侧都有自己唯一的 PDN。2 号器件的所有侧都有唯一的 PDN 设计。这种设置建立了三种 PDN 设计,共用或者隔离收发器电源线。这三种配置被称为“PDN1”、“PDN2”和 “PDN3”。在每一种配置中,出于试验和对比目的,设定了各类电源共享、隔离和稳压器。

这一试验的目的是确定共用关键收发器电源线效果,采用各种类型的稳压器来驱动它们。该测试测量了被干扰收发器通道 RJ(rms) 值 ( 通过高频码型 - 1010),而其他所有收发器通道都运行 PRBS31 数据。针对不同的配置和 4.25Gbps 到 8.5Gbps 的多种数据速率来采集数据。RJ(rms) 参数为衡量性能提供了关键指标,因为这一参数对性能的影响最大。

PDN 第 1 种配置

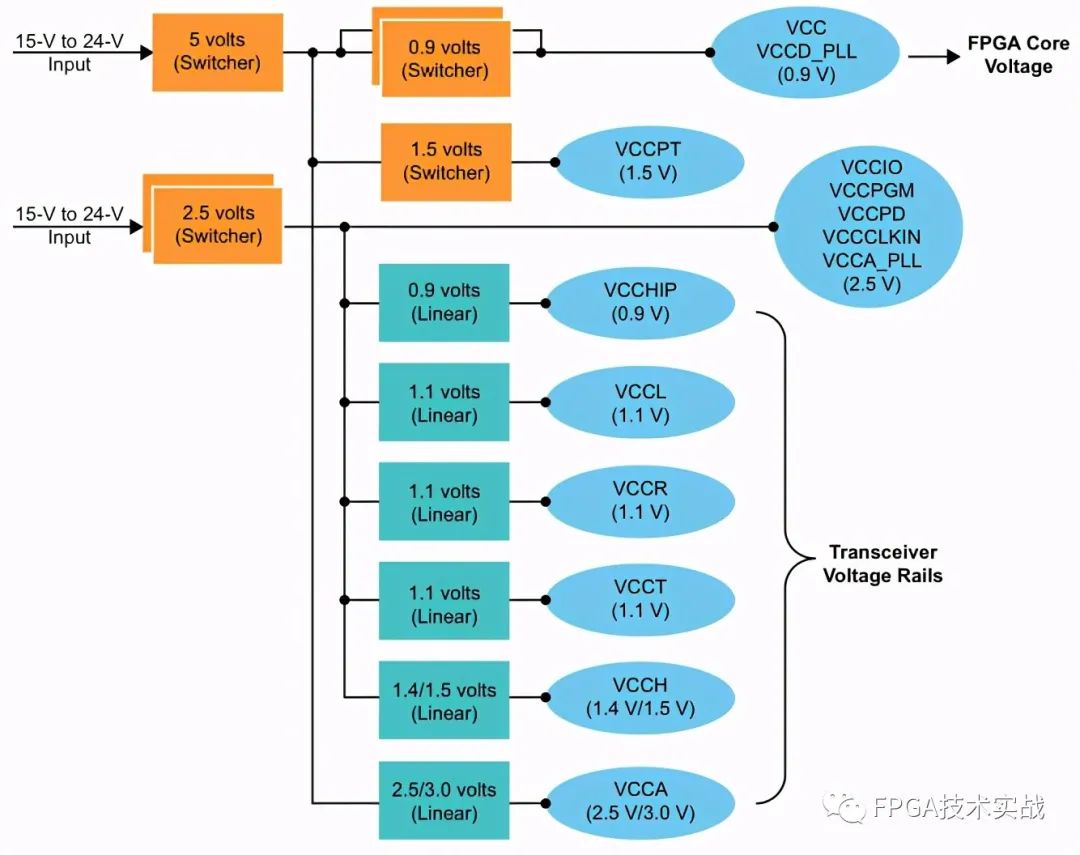

在 PDN1 中,隔离了所有六条收发器电源线,由线性稳压器进行驱动。每一电源线都有自己的电压平面,如图 5 所示。

图 5.PDN1 电源树

PDN 第 2 种配置

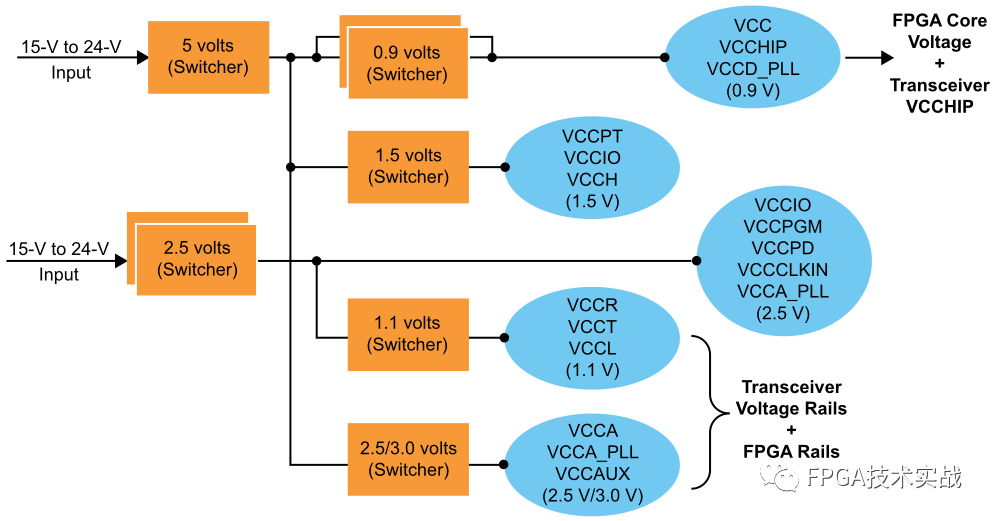

在 PDN2 中,所有收发器电源线与其他电源线共用。共用电源线有自己的电压平面。所有电源线都由凌力尔特技术公司的 Module 开关稳压器进行驱动,如图 6 所示。

图 6.PDN2 电源树

VCCHIP (0.9V) 与 VCC (0.9V) 共用

VCCR (1.1V) 与 VCCT (1.1V) 共用,与 VCCL (1.1V) 共用

VCCH (1.5V) 与 VCCPT (1.5V) 共用

VCCA (2.5V) 与 VCCIO (2.5V) 共用

注意:由于电路板的设计约束,所以 PDN2 配置不支持 8.5Gbps。

PDN 第 3 种配置

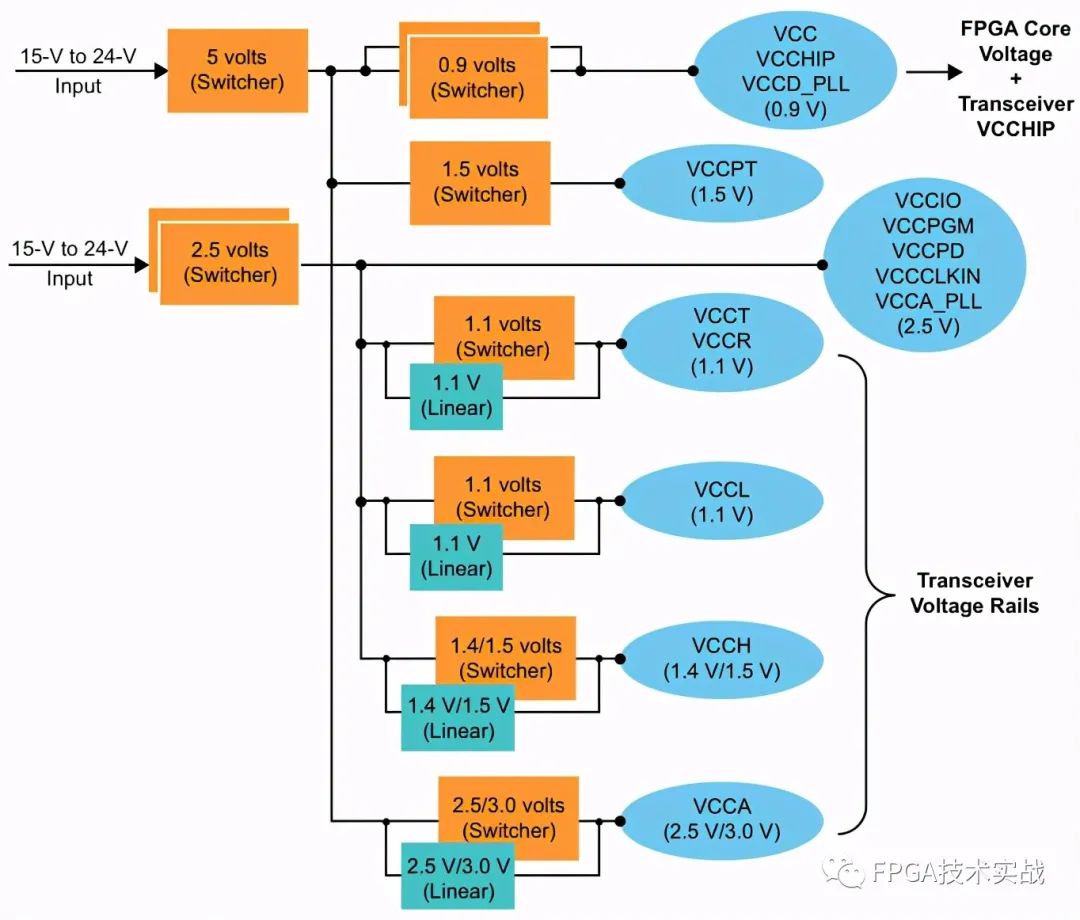

在 PDN3 中,共用两条收发器电源线,由线性稳压器或者凌力尔特技术公司的 Module开关稳压器进行驱动。

VCCHIP (0.9V) 与 VCC (0.9V) 共用

VCCR (1.1V) 与 VCCT (1.1V) 共用

隔离其余的收发器电源线,有自己的电压平面。这些电源线由线性稳压器或者凌力尔特技术公司的 Module 开关稳压器进行驱动,如图 7 所示。

图 7.PDN3 电源树

测试案例

测试案例包括 12 个收发器通道传输数据。将一个通道设定为被干扰通道,其 TX 输出接入频谱分析仪的输入。这一被干扰通道传输高频码型 (1010)。其他的 11 个干扰源通道都在外部环回,传输来自 FPGA 器件内核中的 PRBS31 数据码型。对每一测量都复制了多次,以确保结果能够再现。

最初的测试从 PDN1 数据采集开始,建立基线。考虑到隔离了所有收发器电源线,因此PDN1 应该得到最佳结果。然后,测试了其余配置的其他组合,对数据进行采集。采用Agilent E4440A 频谱分析仪来测量所有数据,以皮秒单位来测量相位噪声或者RJ(rms)。

测试结果

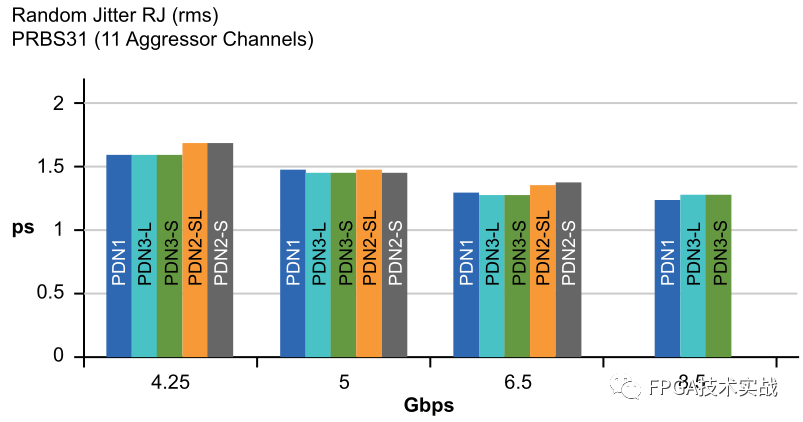

图 8 总结了 5 种不同配置时采集的数据。PDN1、PDN2 和 PDN3 配置展示了隔离和共用电压平面。PDN2 和 PND3 还提供其他功能,针对某些收发器电源线,在开关稳压器和线性稳压器之间进行选择。各种配置曲线如下所示:

PDN1 - (XCVR 电源线 = 所有线性稳压器 )

PDN3 - L (XCVR 电源线 = 所有线性稳压器 )

PDN3 - S (XCVR 电源线 = 所有开关稳压器 )

PDN2 - SL (XCVR 电源线 = 线性 / 开关稳压器的组合 )

PDN2 - S (XCVR 电源线 = 所有开关稳压器 )

图 8.RJ(rms) 数据

如前所述,RJ(rms) 参数对总体性能的影响最大。测试案例采用不同条件处理相关测量,重点是 RJ(rms) 值,作为评估性能的标准。由于组合了电源线,改变了稳压器类型,因此,这一试验清楚的展示了收发器性能不受影响。

5.结论

本文介绍了设计人员怎样通过均衡抖动余量和稳压器数量,使用高级开关稳压器来提高低噪声应用的性能。从这些试验中采集的数据表明,采用 Altera 的 Stratix IV GX器件时,不同配置的性能略有不同。这一数据涵盖了高达 8.5Gbps 的配置。设计人员可以组合电源线,使用新的电源模块技术,实现更简单、更高效的 PDN 设计。

审核编辑:汤梓红

-

开关稳压器和线性稳压器的比较2025-01-03 2820

-

什么是开关稳压器和线性稳压器2024-09-02 1920

-

开关稳压器与线性稳压器的区别2024-05-31 3276

-

开关稳压器的特点 与线性稳压器的区别2023-02-28 2682

-

线性稳压器的相关资料下载2021-11-15 1621

-

为何使用线性稳压器?2021-03-11 2789

-

何谓DC/DC转换器? 线性稳压器和开关稳压器(1)2019-05-15 2328

-

线性稳压器的基础2018-11-29 2868

-

怎么选择线性稳压器与开关稳压器2018-10-24 3966

-

线性稳压器与开关稳压器的联系和区别2018-10-09 3836

-

线性稳压器与开关稳压器有什么不同2018-09-29 4838

-

非隔离稳压模块电源与三端稳压器的主要区别2018-08-04 4299

-

线性稳压器和开关稳压器比较2018-07-02 22274

-

线性稳压器与开关稳压器的比较2011-07-09 3895

全部0条评论

快来发表一下你的评论吧 !