实现可编程逻辑电路的三种主要技术

电子说

描述

实现可编程逻辑电路可以选择三种主要的技术,它们有两种主要的特性:是否可重新编程以及是否易失。我们将介绍三种主要的器件,它们是支持可编程电路的技术基础: 反熔丝、双栅晶体管和基于SRAM的可编程电路。

01反熔丝

反熔丝的概念至少可以追溯到1957年,那时人们考虑将其用在存储器中。当一个编程电流加在反熔丝器件上时,它会由正常的开路状态变为短路状态。它可以通过将一层绝缘层加在两层导电层中间实现,当通以大电流时会在较小的面积上产生较大的功率耗散,会熔断绝缘层。这是一种可单次编程的技术,因为编程后绝缘材料已被破坏不可恢复。制造反熔丝器件可以采用两种主要结构:多晶硅扩散区结构和金属-金属反熔丝结构。

02双栅晶体管

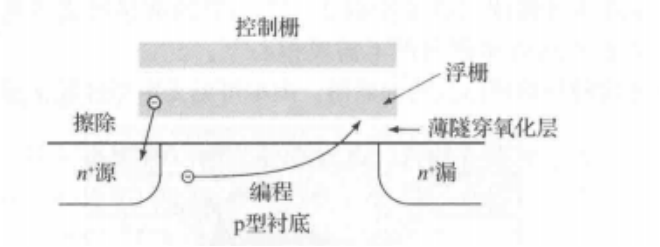

反熔丝技术的主要缺陷在于它的单次可编程特性。双栅(或者浮栅)器件是一种特殊的晶体管,它的控制栅和晶体管沟道之间还有一个浮栅,可以进行非易失性的编程和擦除。Flash存储器件(闪存)便利用了浮栅器件最新的技术,即EEPROM器件。EEPROM晶体管(电可擦除)是UVEPROM器件(紫外线可擦除)的改进版,比后者更为进步---UVEPROM是一种可通过电学机制编程(即在特定的电压偏置状态下)、通过紫外光擦除(因此它们的名称里UV表示用来擦除的紫外线,而E表示通过电学方式写入)的晶体管。UVEPROM器件并不实用,因为要想重新编程,必须从系统中移出然后擦除,而且还需要昂贵的带有供紫外光通过窗口的封装结构。EEPROM晶体管利用电学偏置实现编程和擦除(因而采用EE命名)。由于它们可以现场重新编程,因而更为灵活。EEPROM晶体管的结构如下图所示,它就是一个改进的MOS晶体管。控制栅和普通晶体管的栅极类似,而浮栅被氧化层包围,并不能被电极直接连接。将存储内容写入器件需要将电子打入浮栅中,使之聚集负电荷。浮栅上的负电荷掩蔽了器件的沟道,使之在某种程度上受控制栅上和衬底之间所加电场的影响变小,因而即便控制栅加到Vdd的电平,导电沟道仍无法形成。因此,写入信息后的器件不会导通,而未写入的器件的特性则像普通晶体管一样。

写入过程是这样完成的:将器件置于过饱和区,这样沟道中的热电子被加速,与衬底中的原子碰撞,然后离开衬底,通过薄的氧化层隧穿到浮栅。擦除过程则是通过将控制栅压反置为负,让电子从浮栅中隧穿回晶体管的源极。

03SRAM

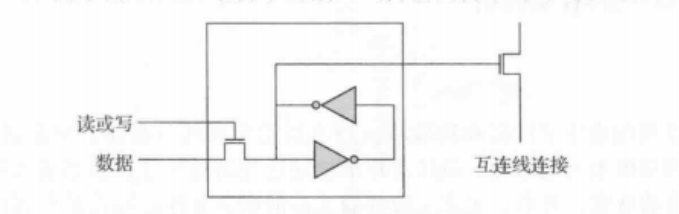

静态RAM开关技术使用了典型的采用交叉耦合反相器的SRAM单元,以存储传输晶体管或者下图所示的FPGA结构中的嵌入式传输门传来的导电状态。

这种技术的优势从根本上来讲在于其与浮栅器件相比,需较短的编程时间。而其缺陷在于它相对较大的面积(这是由于晶体管数更多),并且在每次上电后还需要重新写入。早期的FPGA在每次上电之后都必须从外部ROM或者flash电路中重新写入。现今,许多基于SRAM技术的FPGA都含有flash存储模块,它们保存了电路的配置数据,可以在每次上电后对电路进行内部写入。

作者介绍:刘红江,重庆邮电大学硕士研究生,海云捷迅FPGA硬件工程师,多年FPGA开发经验,熟悉verilog、c等编程语言以及modelsim、vcs、等工具的使用,具有较深厚的数字多媒体通信以及AI加速器开发经验。

审核编辑:汤梓红

-

什么是现场可编程逻辑阵列?它有哪些特点和应用?2024-05-23 2645

-

标准高速可编程阵列逻辑电路数据表2024-05-13 359

-

高性能冲击可编程阵列逻辑电路数据表2024-05-11 373

-

高性能Impact X可编程阵列逻辑电路TIBPAL16C数据表2024-05-07 388

-

现场可编程门阵列是什么2024-03-16 4176

-

可编程逻辑阵列PLA内部逻辑结构示意2024-02-02 5259

-

可编程逻辑器件测试2023-06-06 1296

-

可创建小型组合与时序逻辑电路的PLU可编程逻辑单元2022-12-01 2675

-

实现可编程逻辑电路的三种主要器件2022-09-08 5906

-

逻辑电路的基础知识2020-10-13 31130

-

【转】 时序逻辑电路的三种逻辑器件2016-10-25 5780

-

可编程逻辑器件2014-04-15 3674

-

EDA技术与应用(可编程逻辑器件)2012-05-23 1162

-

什么是可编程逻辑2009-05-29 3798

全部0条评论

快来发表一下你的评论吧 !