vivado使用eco模式下的Replace Debug Probes

电子说

描述

问题描述

在抓信号过程中,想看的信号忘记抓了,如果重新抓取的话将会重新走一遍综合、实现过程,浪费极大时间,漏抓的信号就1bit,实在不值得重新再跑一遍程序。

解决方法

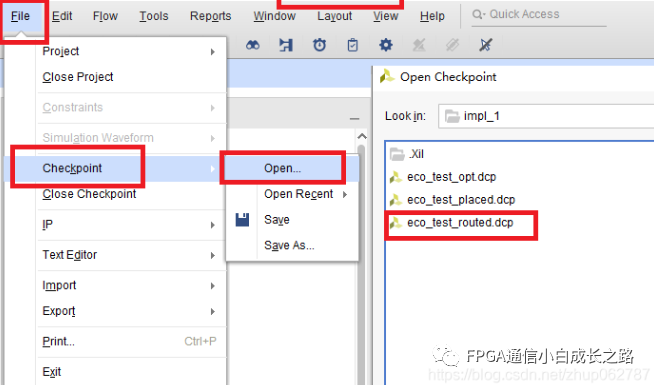

vivado工程编译完成后,在工程目录下vivado在实现(implement)过程中会将中间的过程封装成dcp文件,在/runs/impl_1下,有_opt.dcp、_placed.dcp、_routed.dcp几个dcp文件。

其中_opt.dcp是在opt_design完成之后生成,opt_design主要是完成逻辑优化等。_placed.dcp在placed_design完成之后生成,placed_design主要是完成布局工作。_routed.dcp在routed_design完成之后生成,routed_desig主要是完成布线工作。

可以根据修改的逻辑大小、类型选择DCP节点进行修改。生成bit流时,是从该节点到generate_bitstream,从而节省编译时间。

这里我参考了一篇csdn上的文章(文末附上链接),我引用一个文中提到的也是我用过的方法,剩下的场景大家可参考这篇文章。

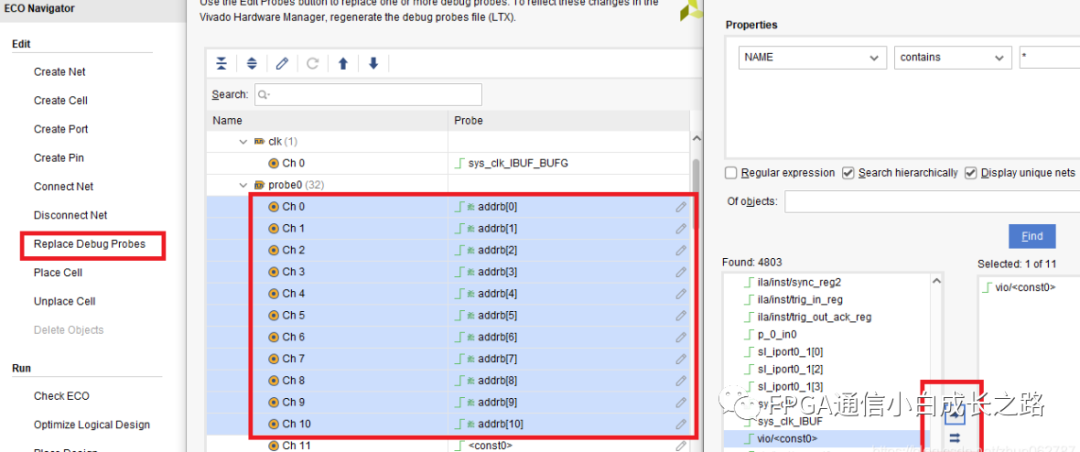

使用eco模式下的Replace Debug Probes(已经有ILA核,只是漏抓了信号)

a,打开_routed.dcp

b,选择Replace Debug probes

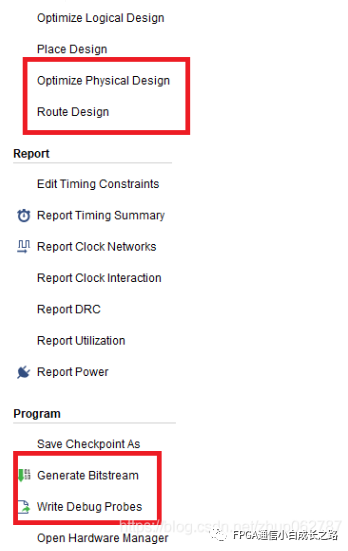

c,因为只是修改了布线,布局没有改动,所以需要Route Design。Optimize Physical Design是优化布局、时序等。大工程不优化有可能布不成功。布局完成,直接Generate Bitstream、write Debug probes

d,对于编译1.5个小时的工程。替换ILA引脚生成bit文件需要10分钟左右。

-

OpenCV4.8在Debug模式下滚动条错误问题解决与原因查找2023-10-23 1110

-

关于Vivado non-project模式2022-10-17 4893

-

如何在批模式下运行 Vivado 仿真器?2022-08-01 1512

-

浅析Vivado在非工程模式下的FPGA设计流程2021-06-19 3788

-

带大家一起体验一下Vivado的ECO流程2020-11-29 5473

-

关于Vivado中三种操作Debug的方式2020-11-11 11997

-

Vivado工程模式和非工程模式的比较2020-11-09 6045

-

一起体验Vivado 的ECO流程2020-10-26 4551

-

使用ECO进行调试有哪些好处2018-11-29 4518

-

如何在Vivado中执行工程变更命令 (ECO)2018-11-21 5915

-

汽车eco模式使用技巧_eco模式真能省油吗2017-12-14 30265

-

Vivado使用误区与进阶——在Vivado中实现ECO功能2017-11-18 5942

-

Vivado中使用debug工具步骤与调试技巧2017-11-17 64154

-

Vivado+FPGA:如何使用Debug Cores(ILA)在线调试2017-02-08 3404

全部0条评论

快来发表一下你的评论吧 !