使用基于处理系统(PS)的千兆以太网MAC(GEM)

电子说

描述

文档简介

本应用笔记描述了使用可编程逻辑(PL)中的高速串行收发器通过扩展多路复用I/O(EMIO)接口和1000BASE‑X或SGMII物理接口使用基于处理系统(PS)的千兆以太网MAC(GEM) 。

介绍

Zynq‑7000 SoC器件在单个器件中集成了基于双核ARMCortex‑A9 MPCore的PS和PL。

PL包括可编程逻辑、配置逻辑和相关的嵌入式设备。PS包括处理器单元、片上存储器、外部存储器接口和包括

两个千兆以太网控制器(GEM)的外围连接接口,它们通过扩展多路复用I/O(EMIO)接口访问PL信号以连接不同的物理接口。

在本应用笔记提供的设计中,PS‑GEM0通过简化的千兆媒体独立接口(RGMII)连接到MarvellPHY,这是ZC706板的默认设置。本应用笔记的重点是额外以太网端口的设计。本应用笔记中描述的设计有:

‧PS以太网(GEM1),通过EMIO接口连接到PL中的1000BASE‑X或SGMII物理接口

‧PL以太网在PL中实现为软逻辑并连接到1000BASE‑X或SGMIIPL中的物理接口

通过EMIO使用PS GEM

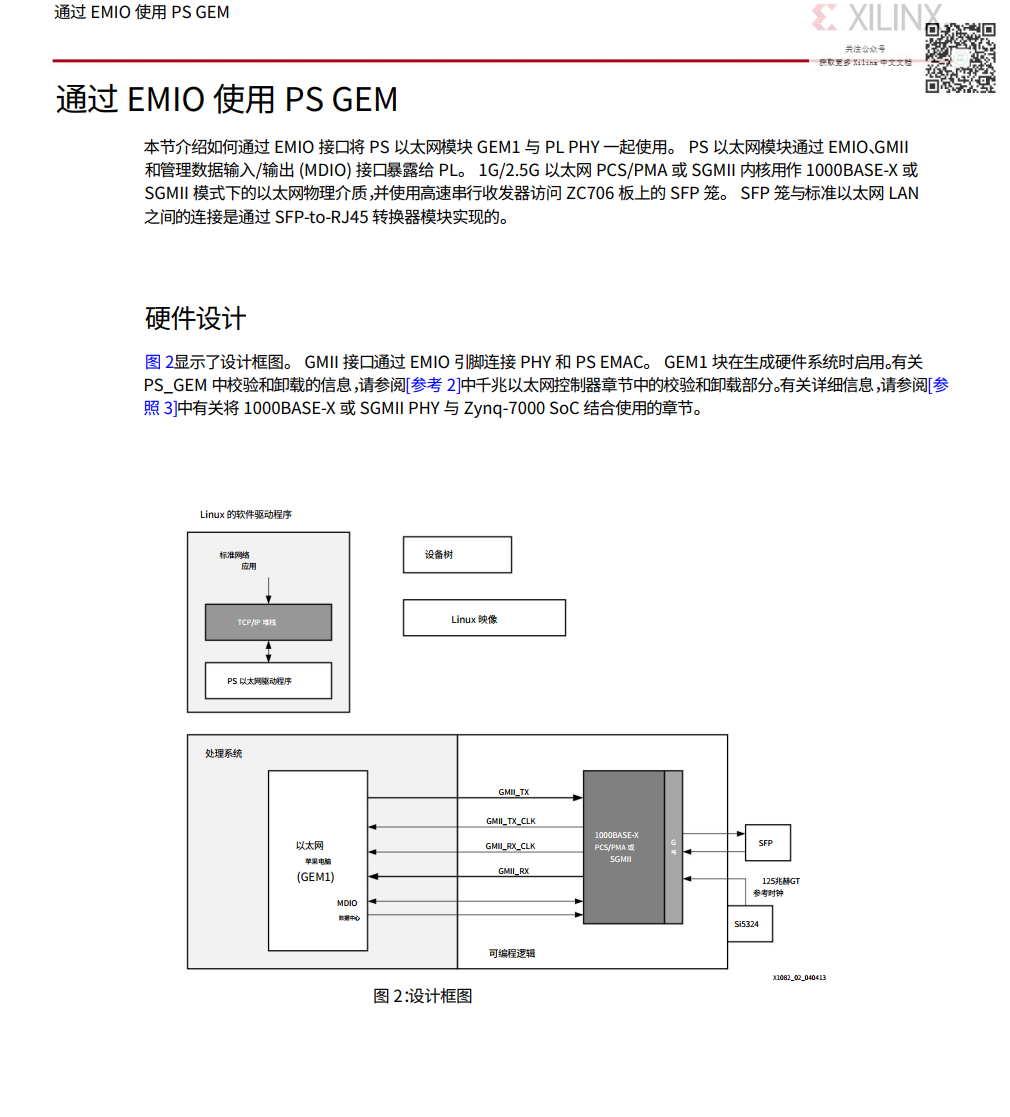

本节介绍如何通过EMIO接口将PS以太网模块GEM1与PLPHY一起使用。PS以太网模块通过EMIO、GMII和管理数据输入/输出(MDIO)接口暴露给PL。1G/2.5G以太网PCS/PMA或SGMII内核用作1000BASE‑X或SGMII模式下的以太网物理介质,并使用高速串行收发器访问ZC706板上的SFP笼。SFP笼与标准以太网LAN之间的连接是通过SFP‑to‑RJ45转换器模块实现的。

软件设计

该设计使用PS‑GEM0和PS‑GEM1的通用macb.c驱动程序代码。要通过EMIO接口启用GEM1,必须对特定寄存器进行编程。这是Zynq‑7000SoC第一阶段引导加载程序(FSBL)使用的PS配置数据的一部分。在为第二个GEM启用EMIO的系统生成时,硬件设计的SDK导出中可用的ps7_init.tcl文件默认包含寄存器设置,它们是:

‧选择EMIO作为接收时钟、数据和控制信号的来源:

将SLCR.GEM1_RCLK_CTRL[SRCSEL]位设置为1

‧选择EMIO作为产生参考时钟的源:

将SLCR.GEM1_CLK_CTRL[SRCSEL]位设置为3

注意:要支持其他PL物理接口,例如TBI,必须编辑硬件设计和设备树。PHY特定的初始化在Linux驱动程序(macb)的phylib子系统中处理,有关PHY的信息可以在设备树中提供。要将phylib子系统用于PHY编程,phylib子系统必须支持所需PHY的PHY初始化例程。

审核编辑:刘清

-

如何使用Vitis自带的LWIP模板进行PS端千兆以太网TCP通信?2024-04-28 8672

-

简谈基于FPGA的千兆以太网设计2023-06-01 1313

-

Zynq-7020千兆网口的3种扩展方案2022-12-14 5806

-

如何快速分辨以太网与千兆以太网2022-05-06 6392

-

DesignWare核心以太网MAC通用评估数据手册2022-03-31 1311

-

分享!基于Zynq-7010/7020的多路千兆网口实现方案2021-10-22 8333

-

【FPGA DEMO】Lab 10:千兆以太网2021-07-30 2240

-

千兆以太网发展现状 千兆以太网技术优势2021-03-21 8849

-

千兆以太网发展现状_千兆以太网前景2020-04-20 2666

-

简谈基于FPGA的千兆以太网2018-02-03 7058

-

基于Xilinx FPGA的千兆以太网控制器的开发2015-01-23 31484

-

带优先级队列的千兆以太网MAC设计2011-05-03 1341

-

用于接入和传送应用的优化的千兆以太网映射器GEM2502010-09-10 1303

-

ATM与千兆以太网的区别2009-05-25 5658

全部0条评论

快来发表一下你的评论吧 !