三星代工厂宣布3纳米节点已进入风险生产阶段

制造/封装

描述

三星代工厂宣布其3纳米节点已进入风险生产阶段。该公告标志着三星和半导体行业的一个重要里程碑。

3纳米GAA

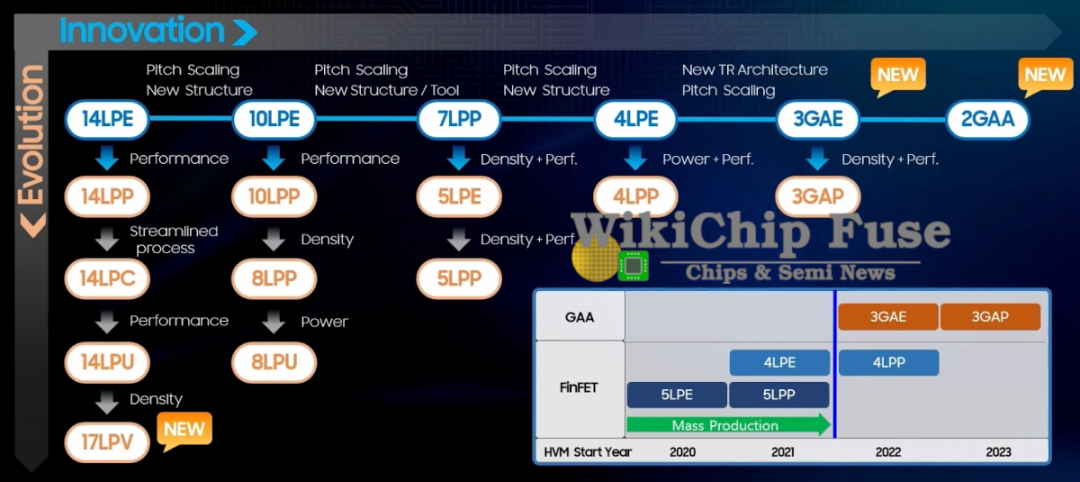

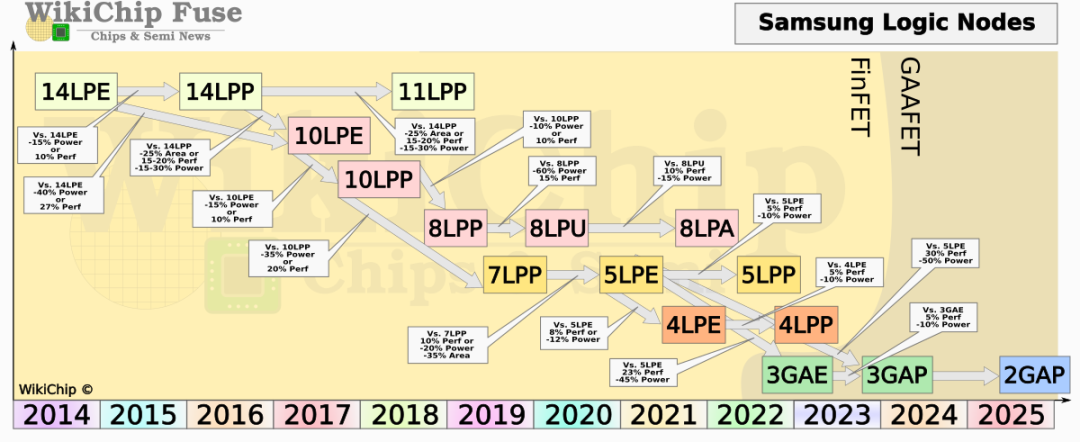

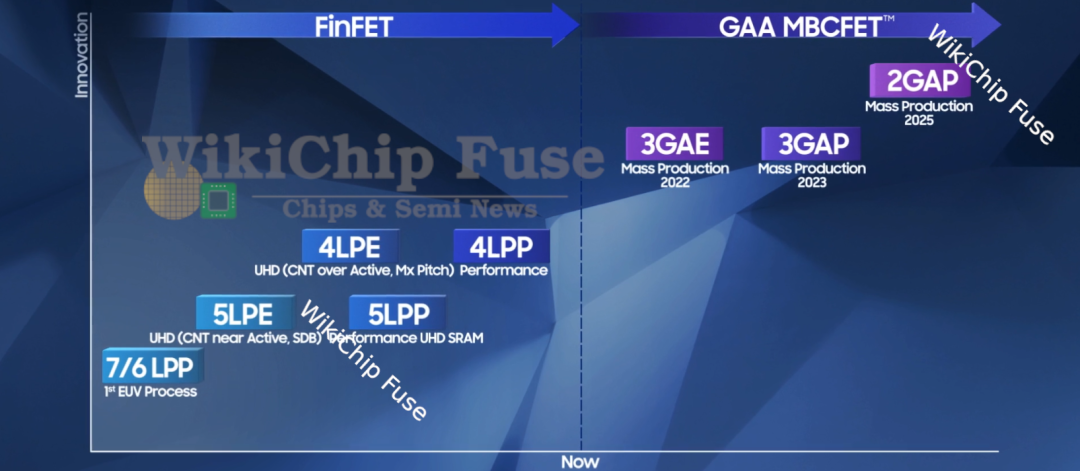

三星最新的生产工艺技术是他们的4nm节点。该节点去年年底提高了产量。这是他们最后一个基于FinFET的前沿工艺技术,尽管不是他们计划中的最后一个。公司未来的领先技术节点将采用新的GAA FET架构。三星代工厂计划推出两种3nm GAA工艺——3GAE和3GAP。

第一代3GAE已进入风险生产阶段,将在年底或2023年实现量产。与他们的5nm工艺技术相比,3GAE可以降低高达45%的功耗,提高23%的性能,并且面积减少16%。

该公司的第二代产品3GAP预计将迅速跟进,并在明年年底前进入量产阶段。三星表示,与3GAE相同的5nm工艺相比,3GAP将降低高达50%的功耗,性能提升30%,面积减少35%。换句话说,与3GAE相比,3GAP应该降低大约10%的功耗、提升5.5%的性能同时减少22%的面积。但三星没有明确说明他们比较的是哪个5nm节点。他们推出了5LPE工艺,随后是5LPP。但按照惯例,三星通常将新节点与其第一代版本进行比较(例如,将4LPE与5LPE进行比较,将5LPE与7LPE进行比较)。因此,我们假设3GAE/P也不例外,这些PPA声明是针对第一代5nm工艺5LPE的。

在功率方面,从 FinFET到GAA的过渡据称可以降低高达50%的功率。自平面晶体管时代以来,我们还没有看到过如此大幅度的功耗降低。另一方面,就性能而言,这些数字偏高,但仅略高于一些先前的节点。对于第2代3GAP,性能和功率数据与我们对后续节点的预期基本一致,与5LPP或4LPP并无太大差异。

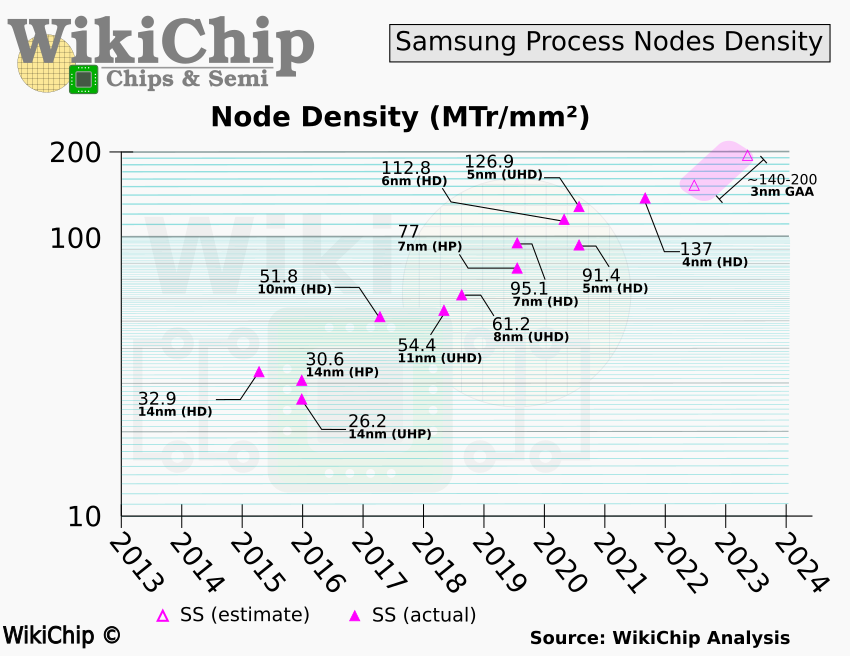

3GAP明确旨在扩展单位面积密度,而不是引入任何重大性能/功率改进。这是我们期望看到的。一种新的晶体管架构的首次推出,面积几乎没有什么改进,随后是设备优化和地址缩放。将面积减少转化为晶体管密度,第一代3GAE的密度提高了约1.2倍,3GAP的密度提高到1.54倍(仍超过5nm),这更接近于三星的全节点密度。

由于我们没有关于该过程的任何实际数据,因此很难给出确切的数字,但粗略估计,3GAE约为150 MTr/mm²,3GAP约为195 MTr/mm²。我们将能够更准确地确定公司开始披露有关流程本身和各种设计规则的更多信息的那些数字。按照估计数据,三星的3GAE将超过台积电的N5,但它完全有可能在密度方面与N4并驾齐驱。将于明年推出的3GAP可能与台积电的N3节点相当。

有关三星3nm GAA工艺的更多技术细节,我们将不得不等待他们提供。

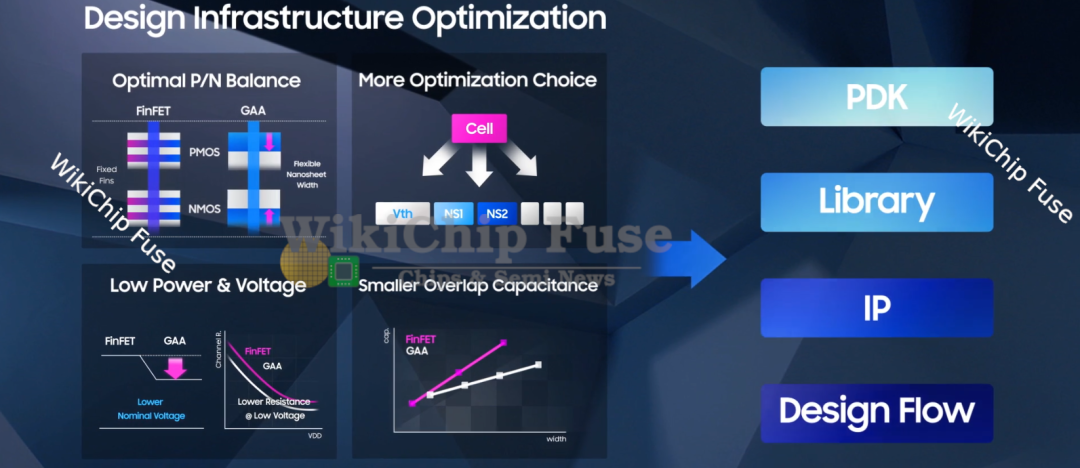

3纳米片,不同宽度

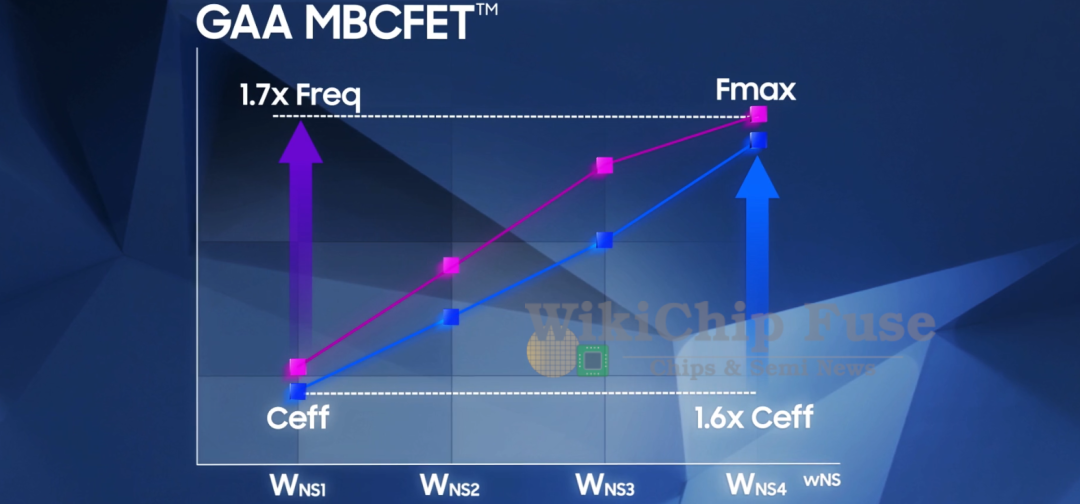

三星称他们的晶体管为多桥通道FET (MBCFET),这是他们自己的纳米片风格。那么三星的3nm有多少纳米片呢?答案是3。他们最初的3纳米工艺技术将采用3个堆叠的纳米片。以前,在基于FinFET的节点上,单元的PPA是根据单元中鳍的数量来量化的,而在3GAA上,三片是固定的,但是,可以通过栅极宽度微调性能,以获得无限的理论PPA梯度。三星已经讨论了四种预定义的纳米片宽度,它们提供了密度和性能之间的权衡。

最宽的纳米片以1.6倍的附加电容提供1.7倍的频率。三星表示,这比等效的FinFET多鳍有更好的改进。

2nm和时间线

三星预计3GAE将在2023年开始生产移动处理器。3GAP将是3GAE的改进版本,并将在明年年底快速增长。三星表示,它希望将其所有生产知识从3nm转移到2nm。为此,三星表示预计2nm将在3GAP之后的两年内推出。他们的2纳米节点称为2GAP,计划于2025年进入量产阶段。

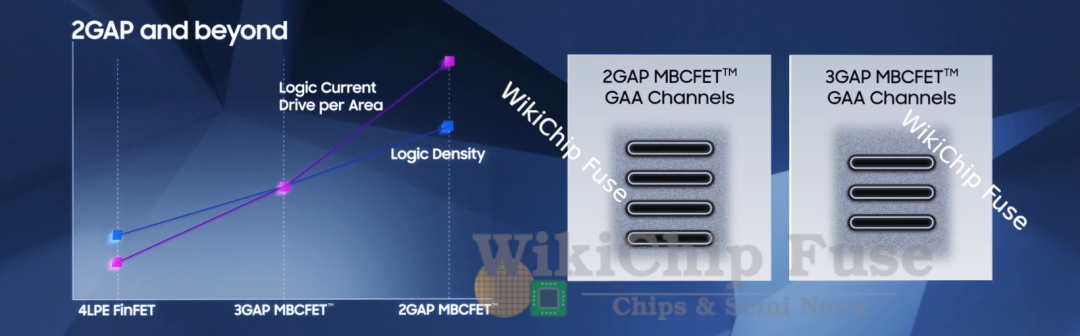

三星表示,2GAP将包括间距缩放以提高晶体管密度。此外,2GAP还将多添加一个纳米片,提供4个堆叠的纳米片,以提高驱动电流。

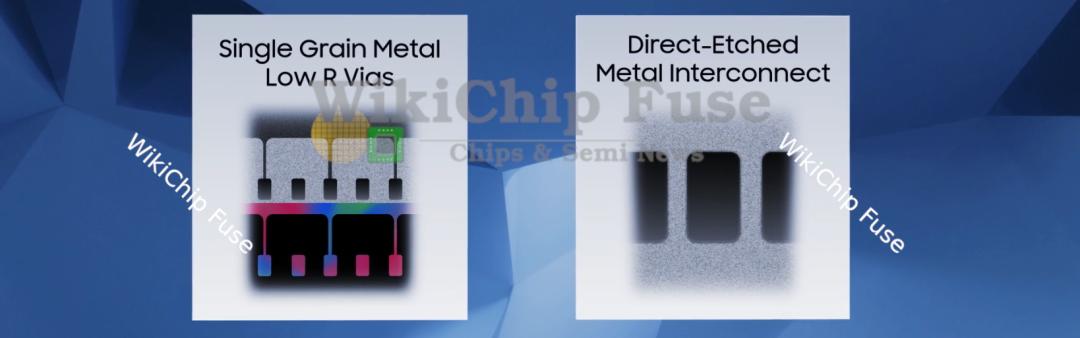

三星表示,他们正在为 2GAP 及其他产品进行多项金属化堆叠改进,包括用于低电阻和直接蚀刻金属互连的单晶粒金属。

编辑:黄飞

-

全球十大晶圆代工厂【经典收藏】2011-12-01 0

-

夏普将沦为三星OEM代工厂?2013-08-05 0

-

三星位于西安的半导体工厂正式投产2014-05-14 0

-

交期受设计资料与PCB代工厂匹配性影响,如何在下单前把控?2022-08-12 0

-

Mentor Graphics 优化工具和流程助设计师成功应对 三星代工厂10 纳米 FinFET 工艺2016-03-11 1371

-

基于三星11LPP的物理IP平台概述2018-06-21 5269

-

三星宣布他们有17种FD-SOI产品进入大批量产阶段2018-08-02 4703

-

三星宣布已正式使用7纳米LPP制程来生产晶圆 功耗降低50%效能提升提高20%2018-10-18 4791

-

AMD12纳米制程订单将由三星或格芯代工2018-11-19 3593

-

英伟达和高通为何考虑转向三星 有哪些要素将影响芯片巨头对代工厂商的抉择2019-06-25 3742

-

三星开始批量生产6纳米芯片,缩小与台积电差距2020-01-06 3191

-

三星近日已开始生产5nm LPE半导体制造节点,芯片即将面世2020-11-02 2846

-

晶圆代工厂商们的“新大陆”2021-05-18 2351

-

概伦电子提取平台SDEP™助力三星代工厂设计团队实现快速迭代2022-06-09 1427

-

三星否认晶圆代工厂生产缺陷传闻2024-06-27 791

全部0条评论

快来发表一下你的评论吧 !