SOI工艺的广泛应用

电子说

描述

绝缘体上硅(SOI)硅片由顶层硅膜、埋氧层和硅衬底三部分组成。随着集成电路技术的发展,体硅衬底CMOS集成电路面临着诸多挑战,如寄生闩锁效应(Latch-Up Effect)、短沟道效应、泄漏电流增大、阈值电压漂移、寄生电容增大等,SOI集成电路则可减少上述困扰。SOI集成电路可以实现集成电路中器件之间更有效的介质隔离,并彻底消除体硅衬底CMOS电路中的寄生闩锁效应,同时降低寄生电容和RC延迟,提高电路操作速度,减少光掩模版数量,减缓短沟道效应,降低功耗。

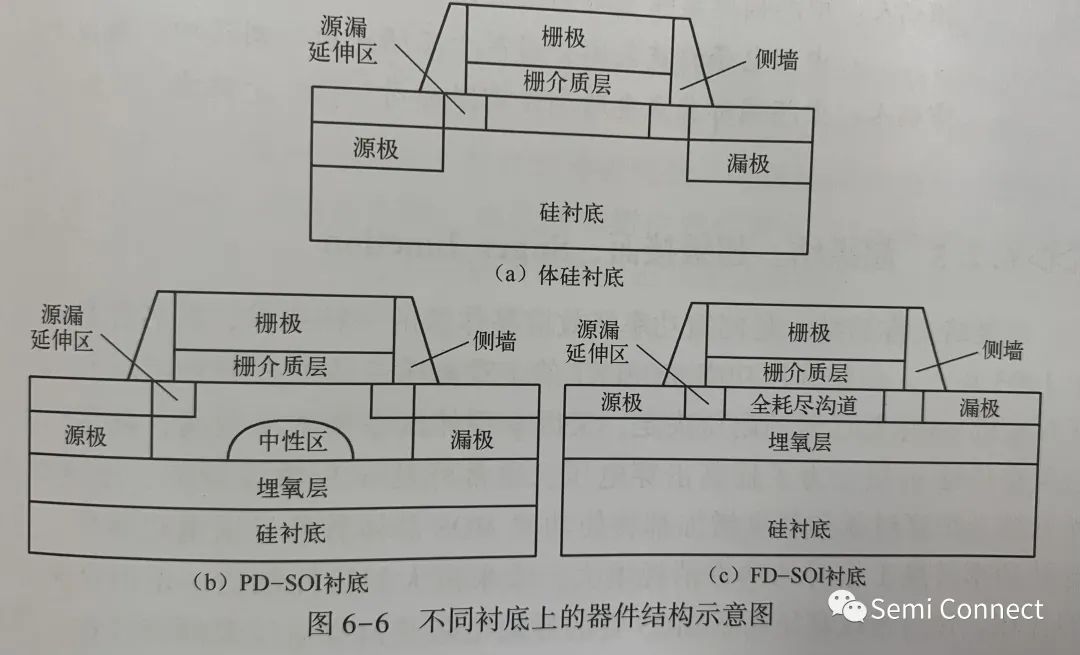

根据器件工作时沟道区域是否存在中性区,将SOI器件分为部分耗尽型SOI(Partially Depleted SOI,PD- SOI)器件及全耗尽型SOI(Fully Depleted SOI, FD-SOI)器件两种类型,如图6-6所示。FD- SDI器件的顶层硅膜较薄,导通状态下硅膜处于完全耗尽状态,消除了中性体区引起的翘曲效应(Kink Effect)和寄生n-p-n管效应。同时,超薄的顶层硅膜使栅极对沟道控制能力得到提高,亚阈值摆幅得到改善,因此FD-SOI器件具有良好的短沟道特性。

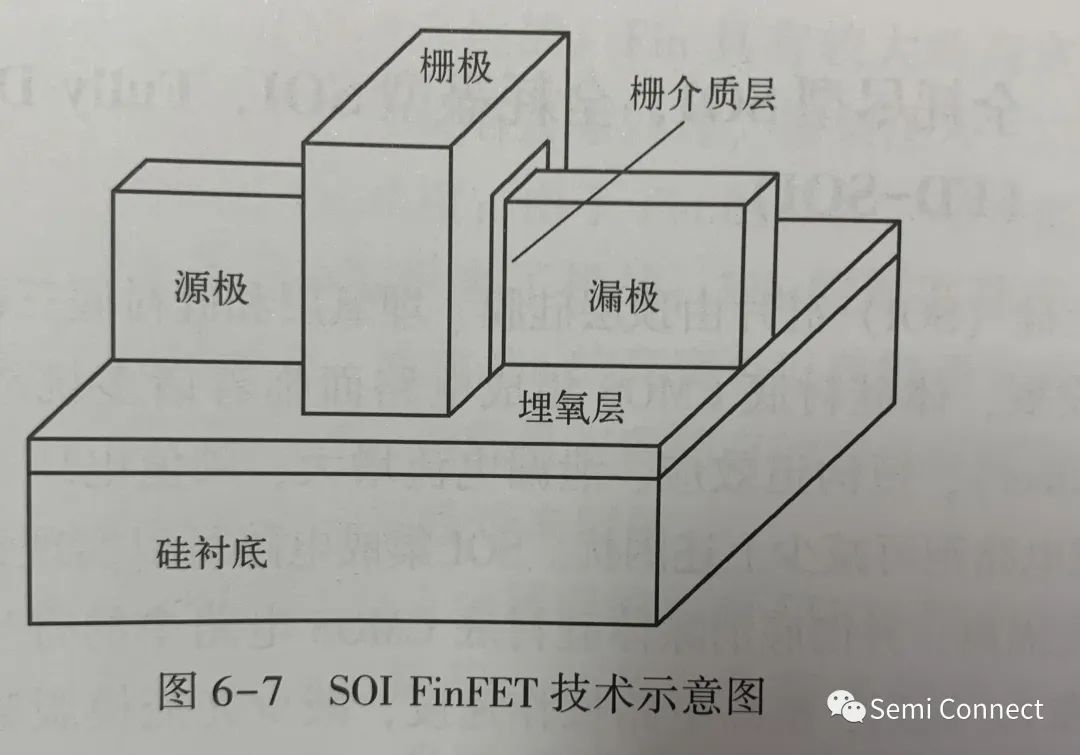

有分析认为,从28nm/20nm节点开始,基于体硅CMOS和FinFET工艺的集成电路主流技术的单个晶体管的成本出现不降反升的局面。而作为FD-SOI技术的主要支持者(如IBM、意法半导体、格芯等)认为,在先进节点上,FD- SOI技术将更具备竞争优势。FD- SOI技术可延续平面CMOS器件的微缩进程。此外,也有一些公司和科研机构正在研究FD- SOI FinFET工艺,如图6-7所示。

相对于体硅FinFET,FD-SOI因目前仍然采用平面架构,其工艺实现难度及制造成本相对较低。虽然在SOI衬底上制备集成电路的工艺相对简单,但其原材料成本较高,限制了SOI工艺的广泛应用。除了介个因素,FD- SOI的产业生态环境也是制约其发展的重要因素,模拟仿真软件、设计IP、设计工具尚不及普通体硅技术健全,因此FD- SOI目前主要应用于低功耗、低漏电等领域。

-

SOI工艺技术介绍2025-10-21 2543

-

一文详解BSIM-SOI模型2025-09-22 2580

-

RF-SOI具有的优点2022-09-27 5565

-

《炬丰科技-半导体工艺》III-V/SOI 波导电路的化学机械抛光工艺开发2021-07-08 3584

-

绝缘轴承因其独特的工艺和特性而有着广泛应用2020-06-15 870

-

关于0.2微米射频SOI工艺设计工具包的分析和介绍2019-10-21 3822

-

高级工艺未来分化,FD-SOI受益2019-08-06 4602

-

新傲科技SOI30K生产线项目首台工艺设备搬入2019-03-14 4688

-

超声波焊接机为什么能广泛应用?2018-09-01 3251

-

SOI先进工艺发展如此迅速的原因在哪?2018-07-11 8034

-

5G射频前端 | RF MEMS与RF SOI 两种工艺谁才是主流?2017-07-13 9014

-

FD-SOI(全耗尽型绝缘层上硅)2016-04-15 7046

-

SOI技術介紹2011-07-06 3946

-

SOI和体硅集成电路工艺平台互补问题的探讨2009-12-14 722

全部0条评论

快来发表一下你的评论吧 !