PCB板中哪些因素对传输线损耗有影响

PCB设计

描述

编者注:本文的内容其实比较简洁,前面两个因素结合ADS仿真原理图给大家介绍,有兴趣的也可以照着做做。很多总线都会给处损耗的要求,所以对于设计工程师而言,就需要哪些因素主导着损耗的变化。

我们经常讨论PCB中损耗大小的问题。有的工程师就会问,哪些因为会影响损耗的大小呢?其实,最常见的答案通常会说PCB材料的损耗因子、PCB传输线的长度、铜箔粗糙度,其实答案肯定远不至于此。下面我们分别就相应参数做一些实验给大家介绍下PCB板中哪些因素对传输线损耗有影响。

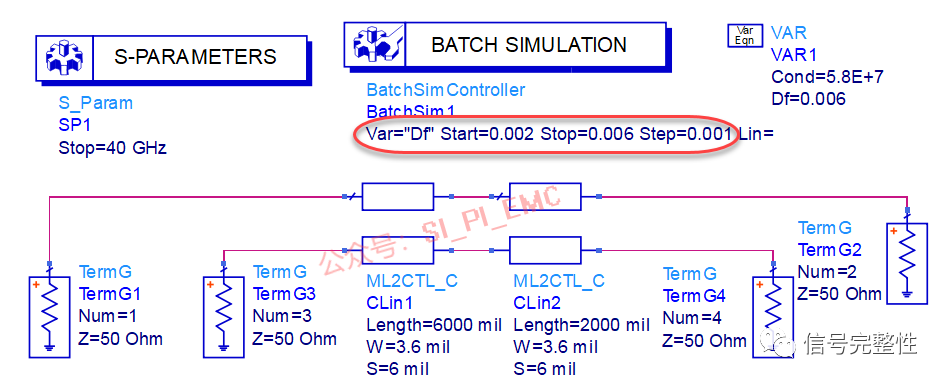

首先看看介质损耗因子Df对损耗的影响,以Df为变量,分析Df的变化对损耗的影响,下图是分析的原理图:

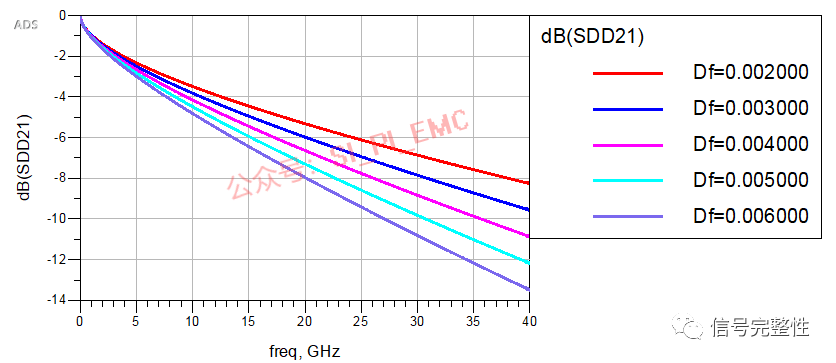

仿真对比结果如下,显然,随着PCB介质损耗因子的变大,损耗越来越大:

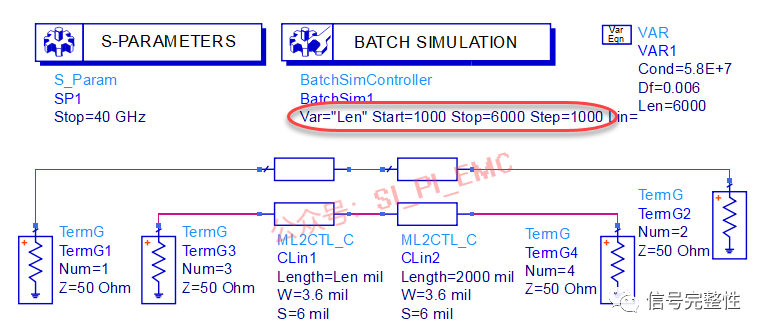

长度也是损耗的主要因素之一,把传输线长度设定为Len变量,分析Len的变化对损耗的影响,下图是分析的原理图:

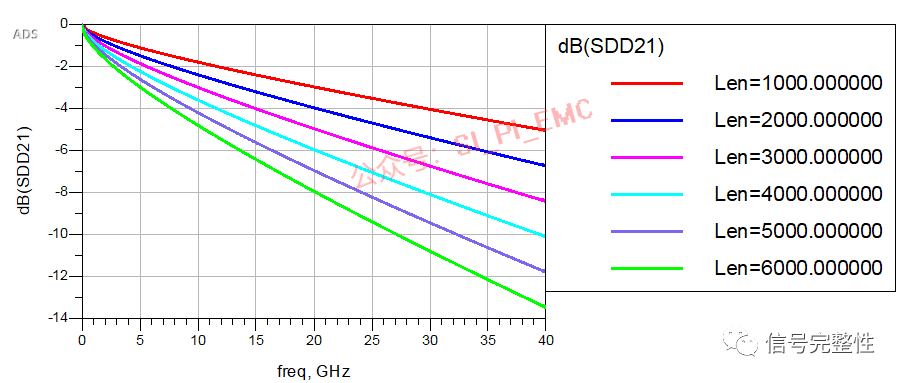

仿真对比结果如下,显然,随着传输线长度越来越大大,损耗越来越大:

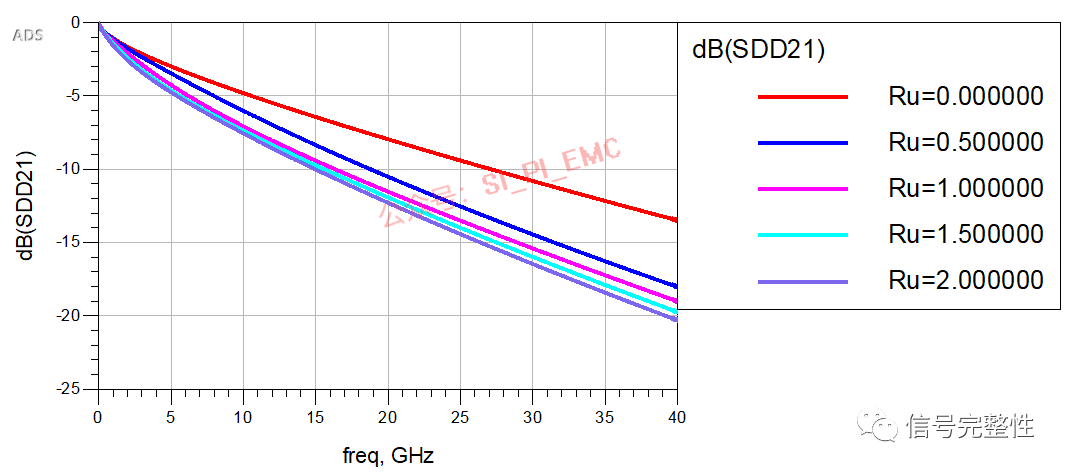

铜箔是PCB中常用的导体,其粗糙度的大小也会对损耗造成影响,通过分析,粗糙度的变化对损耗的影响如下图所示:

从上图中可以看到铜箔粗糙度越大,损耗越大。

这三个影响因子是工程师们很容易能理解。为了减小,工程师们通常想到的方式就是使用低介质损耗角因子、减短传输线长度以及减小铜箔粗糙度。

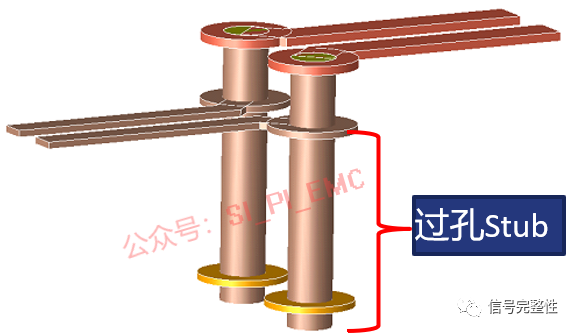

除了这三个影响因子,还有诸如过孔、传输线对内不等长、串扰等对损耗有影响。如高多层板中的过孔,很多时候都会存在的过孔残桩(Stub),如下图所示:

过孔残桩(Stub)就会导致损耗变大,如下图所示为相同的过孔,没有残桩和有残桩的损耗结果,有残桩的时,会存在一个非常大的谐振点,即在此谐振点处,损耗非常大。

并且,随着残桩越来越大,谐振的频率会越来越小(相对应在特定的频率处损耗也会变大)。

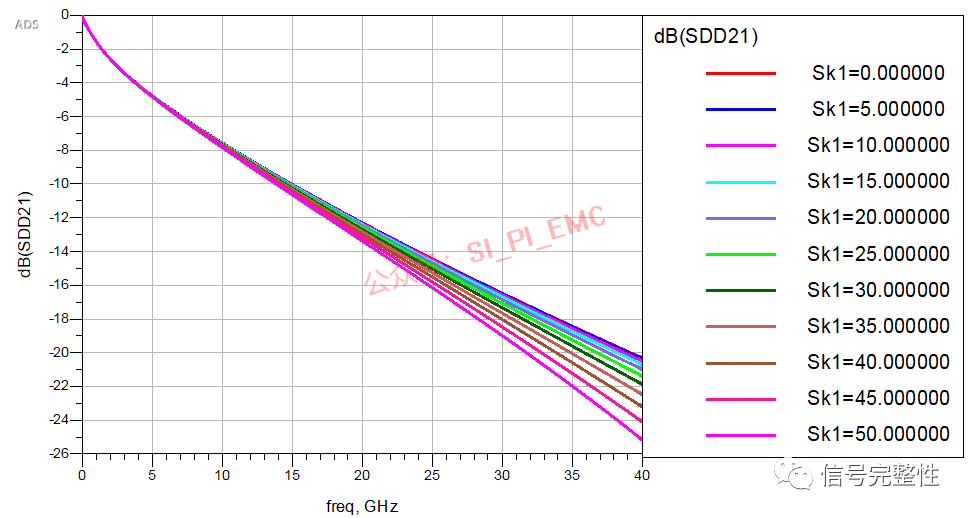

在PCB设计中,经常会出现差分对内不等长(偏差skew)的现象,经过实验发现,随着偏差长度的变化,损耗也会不一样。如下图所示,随着偏差长度的越来越长,相同频率点处的损耗也越来越大。

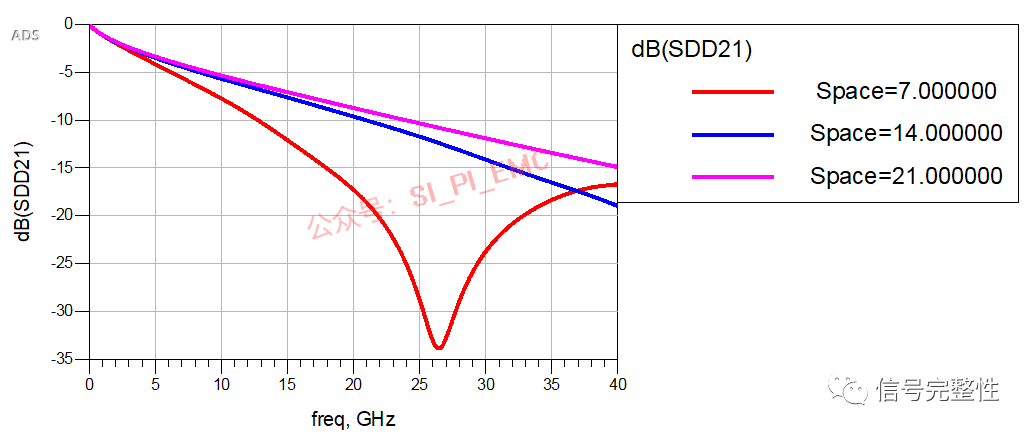

在集成度越来越高的产品设计中,串扰是工程师一直都在担心的问题。因为严重的串扰会导致很多信号完整性的问题,比如对损耗的影响就是其中之一。如下图所示为微带线时,当传输线与传输线的间距变化时的损耗对比结果。

显然,在保持其它设置不变时,间距越大,在相同特定频率点处,传输线的损耗衰减越小。其实串扰对损耗的影响还有一些比较有趣的现象,比如什么时候串扰会造成损耗的谐振点,等等。

以上几个因素对PCB传输线的损耗影响非常大。当然,还有一些其它的因素的实验结果后续有机会再给大家分享。大家也可以在文末留言共同讨论。

审核编辑:汤梓红

-

传输线损耗:模型和方程式2023-11-25 2467

-

传输线的类型有哪些?PCB上什么样的线才是传输线?2023-09-28 5599

-

PCB板加工流程中哪些因素会影响到传输线阻抗2023-06-06 865

-

PCB设计之实例解析传输线损耗2022-11-10 2255

-

如何量化传输线中的导体损耗和介质损耗呢2022-08-15 11952

-

PCB板上多长的走线才是传输线?2020-11-06 6896

-

传输线的损耗原理是什么?2019-08-02 2796

-

PCB传输线原理2018-11-23 1954

-

印制电路板传输线信号损耗测量方法2018-09-17 2385

-

PCB传输线参数2018-09-03 2953

-

基于高速PCB传输线建模的仿真2018-08-27 2675

-

传输线端接对电磁兼容的影响2011-11-21 731

-

传输线的特性阻抗分析2009-09-28 9504

-

过孔对传输线信号的影响详解2007-10-10 4991

全部0条评论

快来发表一下你的评论吧 !