Design Compiler软件有哪几种模式

电子说

描述

Design Compiler软件有四种模式,分别为:

• Wire Load Mode (Default)

• Topographical Mode

• Multimode

• UPF Mode

其中Wire Load Mode和Topographical Mode是工具模式,我们可以在启动软件的时候决定启动哪种模式。如果用dc_shell或者design_vision后边什么option不加,工具默认以Wire Load Mode启动软件。如果启动软件的时候后边加上-topo或者-topographical_mode,则软件以topo模式启动。

另外两种模式Multimode和UPF Mode并非工具启动的模式而是topo下的两种模式,分别支持多个工作条件、多个模式以及UPF低功耗。

Wire Load模式 - DC

在线负载模式(Wire Load Mode)下,工具使用Wire Load Model(线负载模型)来估算Wire上的Delay。

默认启动DC的时候就是启动Wire Load Mode:

dc_shell或者design_vision

这种模式在老的工艺下用的比较多,深亚微米下用的不太多,你可能会发现有些Foundary的库里面已经没有Wire Load Model了,对于大型Design,我们可以使用下面介绍的Topo模式。

Topo模式 - DCT

在拓扑模式(Topographical Mode)下,我们可以读入一些物理Floorplan信息以及物理约束信息,DC也只有该模式可以读入这些信息。在该模式下,工具不用借助Wire Load Model来估算Wire delay。因为有了物理信息,因此在逻辑综合过程中,工具可以借助布局以及优化的技术来优化Timing、Power、Area,使得优化结果更加棒,另外和布局布线后的Timing结果也更加接近。

如前所述,在启动dc的时候我们后边加上-topo即可启动topo模式:

dc_shell -topographical_mode

我们可以在topo模式下运行两种编译方法:

compile_ultra

这个大家应该都不陌生,下面着重讲另一种DCG:

compile_ultra -spg

DCG(Design Compiler Graphical)

在DC的topo模式下,运行下面的命令进行综合便会调用DCG:

compile_ultra -spg

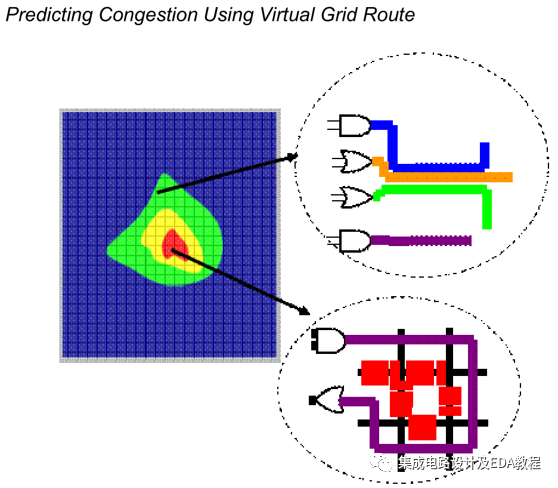

该命令在编译过程中会使用DCG(Design Compiler Graphical)来对MCMM的Design进行优化,还可以优化Congestion(如下图所示),做AHFS(Automatic High-Fanout Synthesis)来解逻辑DRC,提高与ICC/ICC2在PPA上的Correlation,优化ICC/ICC2中的runtime,另外我们还可以在DCG中使用Floorplan exploration创建以及修改Floorplan。

需要注意的是运行DCG需要DC Ultra和Design Compiler Graphical的license支持。

审核编辑:刘清

-

如何对keil软件进行调试?有哪几种模式?2021-07-27 1394

-

MBD有哪几种设计模式?2021-10-13 1427

-

伺服电机模式有哪几种?2021-10-29 3235

-

常见的约束命令有哪几种呢2021-11-02 3182

-

STM32的启动模式有哪几种?2021-11-23 2106

-

IO口模式有哪几种?2021-11-25 919

-

bootloader的升级模式有哪几种?2021-11-26 2119

-

ADC的转换模式有哪几种?2021-12-02 9511

-

GPIO工作模式有哪几种?2022-02-11 1560

-

SMT元器件有哪几种类型2020-11-27 3292

-

风机轴维修有哪几种工艺2021-12-03 908

-

轴承跑内圆有哪几种修复方式2022-01-23 1230

-

轴承孔磨损维修有哪几种方法?2022-04-01 1184

-

ESD模型有哪几种你知道吗?2023-05-09 3370

-

EMI滤波器有哪几种应用和选择?2023-10-09 3132

全部0条评论

快来发表一下你的评论吧 !