AD9958高性能可双路输出的DDS器件

模拟技术

描述

AD9958是Analog Devices公司生产的一款高性能、动态特性优异、可双路输出的DDS器件,每路可单独控制频率,相位/幅度。这种灵活性可用于校正信号之间由滤波、放大等模拟处理或PCB布局失配而引起的不平衡问题。由于两个通道共享一个公共系统时钟,因此它们具有固有的同步性,可支持多个设备的同步。AD9958内部集成了10 bit的输出幅度控制,内部工作频率高达500 MHz,使其可产生最高频率为250MHz的双路信号。其内部有许多用于控制输出信号参数的控制寄存器,具有32位频率调整分辨率、14位相位失调分辨率、10位输出幅度可缩放分辨率,有增强数据吞吐率的串行SPI口。可工作于多种模式,支持单频信号模式(single-tone)、调制模式(modulation mode)、线性扫频模式(linearsweep)以及混合信号模式。可以执行高达16阶的频率、相位或幅度调制(FSK、PSK、ASK)。

1 AD9958的结构

AD9958的串行I/O端口可支持多种配置,提供了极大的灵活性。与ADI公司以往DDS产品中提供的SPI工作模式类似,串行I/O端口提供SPI兼容工作模式。四个数据引脚(SDIO_0/SDIO_1/SDIO_2/SDIO_3)对应串行I/O的四种可编程模式,从而提供了高灵活性。AD9958采用高级DDS技术,可在低功耗下提供高性能。这款器件集成了两个具有卓越宽带和窄带SFDR性能的高速10bitDAC。每个通道均具有专用的32bit频率调谐字、14bit相位偏移和10bit输出比例乘法器。DAC输出以电源电压为参考源,必须经由电阻或AVDD中心抽头变压器连接到AVDD。每个DAC均具有各自的可编程基准源,用于实现每个通道不同的满量程电流。当使用REF_CLK作为输入,并由DAC提供输出时,这款DDS可用作高分辨率分频器。两个通道共用REF_CLK输入源,REF_CLK输入源可被直接驱动,或与高达最大值500MSPS的内置REF_CLK乘法器(PLL)配合使用。 PLL倍增因数的可编程范围为4~20,步进为整数。REF_CLK输入还具有振荡电路,可将外部晶振用作REF_CLK源,晶振的频率必须在20 MHz与30 MHz之间,晶振可与REF_CLK乘法器配合使用。

AD9958采用节省空间的56引脚LFCSP封装。DDS内核(AVDD和DVDD引脚)采用1.8 V电源供电。数字I/O接口(sPI)在3.3 V电压下工作,并需要将DVDD_I/O引脚(引脚49)连接至3.3 V电压。AD9958可在-40℃~+85℃的工业温度范围内工作。

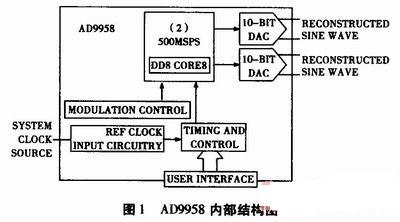

AD9958的内部结构如图1所示,主要特性如下:

*两个500 MSPS同步DDS通道

*所有通道之间独立的频率/相位/幅度控制

*频率、相位和幅度变化时的延时匹配

*卓越的通道间隔离

*线性频率/相位/幅度扫描功能

*高达16阶频率/相位/幅度调制(引脚选择)

*内置两个10 bit数模转换器(DAC)

其主要应用在以下几方面:

*捷变本振(ALO)频率合成

*相控阵雷达/声纳

*仪器仪表

*同步时钟

*用于AOTF(声光可调滤波器)的RF源

*单边带抑制载波

*正交通信

2 引脚说明

AD9958采用56脚LFCSP封装,其引脚图如图2所示,其主要引脚功能如下:

SYNC_IN:同步多片AD9958的输入信号,使用时与主器件AD9958的SYNC_OUT相连;

SYNC_OUT:同步多片AD9958的输出信号,使用时与从器件AD9958的SYNC_IN相连;

MASTER_RESET:复位引脚,高电平有效;

PWR_DWN_CTL:电源掉电控制引脚;

CH0_IOUT、CH1_IOUT:通道0、1输出端,无需上拉电阻,输出范围可达AVDD;

CH0_IOUT、CH1_IOUT:通道0、1互补输出端,无需上拉电阻,输出范围可达AVDD;

DAC_RSET:DAC复位端,为DAC创建参考电流,通过一个1.91 kΩ的电阻接至AGND端;

REF_CLK、REF_CLK:参考时钟或晶振输入端;

CLK_MODE_SEL:振荡器模式控制引脚,为1时使能振荡器为REF_CLK源,为0时不使能;

LOOP_FILTER:与锁相环环路滤波器的零点补偿电路连接,此引脚与AVDD间串接一个0 Ω电阻和680pF电容。

P0,P1,P2,P3:调制数据引脚;

I/O_UPDATE:I/O口更新寄存器控制端,此引脚上升沿数据从串口缓冲器送入寄存器。

:片选端,低电平有效,允许多芯片共用SPI总线;

SCLK:I/O口读写时的串行数据时钟输入端,上升沿写操作,下降沿读操作;

SDIO_0:专用串行I/O口引脚;

SDIO_1,SDIO_2,SDIO_3:用作串行I/O口引脚或初始化DAC输出幅度增减量控制引脚;

SYNC_CLK:同步时钟输出引脚,为系统时钟的4分频。

-

请问DDS参考时钟的输入功率(AD9958)是如何计算的?2018-10-09 5223

-

求AD9958测试程序2018-10-19 2128

-

AD9958输出幅度不稳定该如何解决?2018-12-11 4118

-

具有10位DAC的AD9958直接数字频率合成器的评估板AD9958/PCBZ2019-02-27 2792

-

可双路输出的DDS芯片AD9958相关资料下载2021-03-29 1745

-

请问AD9958的输出相位受温度的影响大吗?2023-11-14 528

-

AD9958,pdf datasheet (2-Channe2009-10-24 715

-

基于AD9958型DDS的LPI雷达多波形设计2010-12-22 1209

-

基于AD9958的雷达信号源软硬件设计2010-12-23 1130

-

高性能双通道DDS芯片AD9958及其应用_陈昶2017-07-24 2253

-

基于AD9958的双通道正弦信号源的设计2017-11-14 2283

-

利用AD9958/AD9959多通道DDS实现相位相干FSK调制器的设计2019-06-12 12334

-

AD9958评估板数据手册2021-03-20 756

-

AN-1576:采用AD9958 500 MSPS DDS或AD9858 1 GSPS DDS和AD9515时钟分配IC的高性能ADC的低抖动采样时钟发生器2021-04-30 969

-

AD9958:高性能2通道DDS芯片的深度剖析2026-04-16 66

全部0条评论

快来发表一下你的评论吧 !