关于DDR4的绕等长,您想知道的都有

电子说

描述

对于DDR4的设计,相信攻城狮们经历过万千项目的历练,肯定是很得心应手,应该已经有自己的独门技巧了。比如选择合适的拓扑结构,信号同组同层,容性负载补偿,加上拉电阻等等。但是对于时序方面的控制,理论上只有一个办法——绕等长,速率越高的DDR4,等长控制越严格,从±100mil,到±50mil,甚至±5mil……

一个平平无奇的日子,网红芬带着新合作的客户项目经理李工来找我,客户对我们做某FPGA DDR4设计要求有疑问,说我给的等长规则不对,为啥要按时间设置等长,以及他看到规则管理器的长度差很大,其中时钟和地址信号长度明显超过了手册spec要求,以前用P软件设计从来没有出现这样的问题。紧接着李工急促说道:“我们设计的DDR4项目本来就运行不到2400Mbps,找你们debug优化设计,就是信任你们的品牌,你们这样做设计让我感觉很不专业,我们项目很重要……”

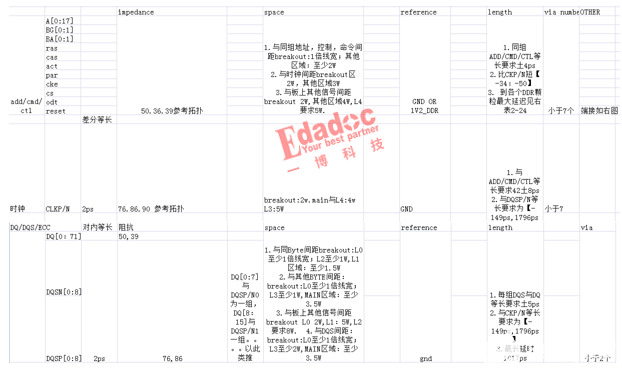

某FPGA等长要求

对于李工个中艰辛自不必多说,我们相当明白他的痛点。我问道:“李工你们对于DDR4换层过孔的补偿在P软件是如何考量的?pin delay是怎样设置的?表层布线和内层布线长度一样,就是时序一样了吗?”李工当场就愣住了!

高速先生以前说过,等长从来都不是目的,DDRx系统要求的是等时,除了差分对内的等时是为了相位之外,绝大多数的等时都是为了时序!现在流行重要的事情说三遍:等时,等时,等时!那如何保证我们的DDR4 PCB设计是等时的呢?大致可以按照下面的操作步骤来。

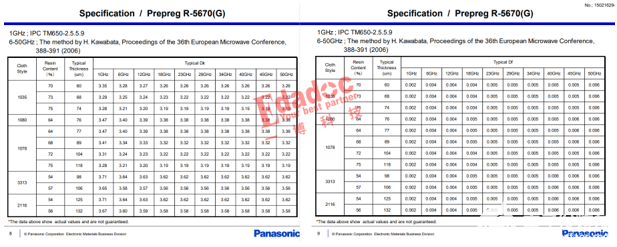

做等长第一步是要设置准确的层叠参数,介质厚度和Dk。在设计过程中我们需要将设计层叠发送给板厂做加工层叠确认和备料。加工备料层叠如下图所示:

根据备料层叠按照材料手册来设置相关的介质厚度和Dk/Df参数:

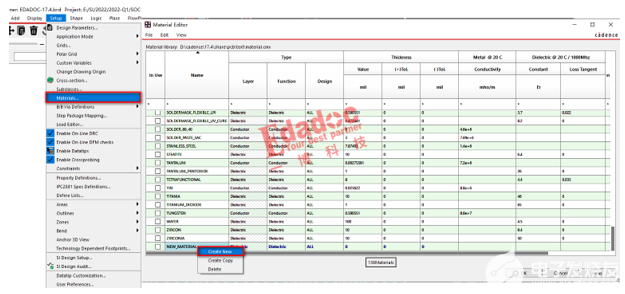

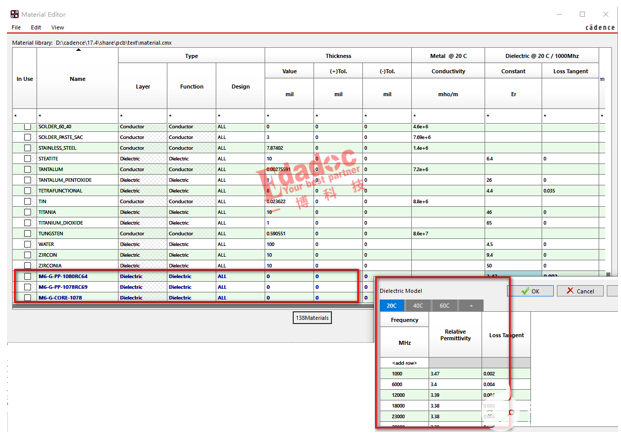

点击Setup菜单栏下方-Materials,即可以打开allegro自带的材料参数表,由于我们使用M6-G材料需要自定义增加相关材料参数,选中表格点击右键即可增加自定义的材料参数。

自定义一个自己使用习惯的名字,既可设置不同频率下的Dk/Df,也可设置不同温度下的Dk/Df,相关数据设置如下所示:

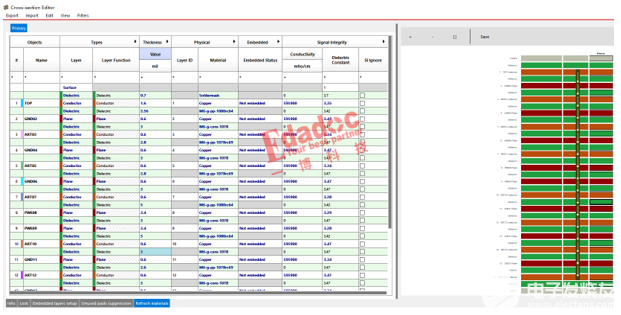

设置好材料参数之后,就可以打开层叠将相关参数设置好,这样我们对于层叠部分的设置就基本完成了,如下所示:

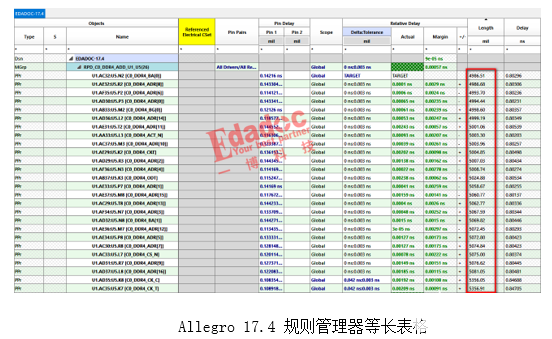

接着就可以导入Pin delay和设置等长规则了,我们的网红芬就是按照上述操作设置的相关规则。

审核编辑:刘清

-

DDR4的主要参数2024-09-04 14552

-

DDR4和DDR3内存都有哪些区别?2023-10-30 14960

-

高速设计:用于DDR3/DDR4的xSignalAltium 2023-06-25

-

关于DDR4的绕等长,您想知道的这本书上都有2022-09-19 1696

-

速率越高的DDR4,等长控制越严格?2022-09-13 2103

-

DDR4原理及硬件设计2021-11-06 3462

-

佛山回收DDR4 高价回收DDR42021-07-15 942

-

关于一个一个等时不等长的DDR设计2021-03-26 3350

-

DDR4设计规则及DDR4的PCB布线指南2019-07-26 52642

-

Allegro中关于绕等长的自动功能2018-10-19 30815

-

DDR4技术有什么特点?如何采用ANSYS进行DDR4仿真?2018-10-14 28375

-

ddr4和ddr3内存的区别,可以通用吗2017-11-08 32666

-

AD中关于绕等长的方式与方法2016-09-12 2346

-

DDR4,什么是DDR42010-03-24 4258

全部0条评论

快来发表一下你的评论吧 !