D触发器实现的原理

描述

从D触发器的角度说明建立和保持时间。

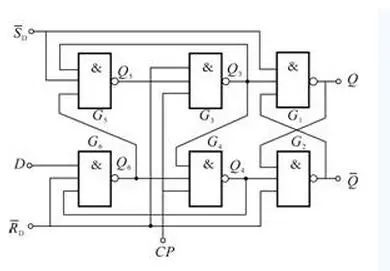

上图是用与非门实现的D触发器的逻辑结构图,CP是时钟信号输入端,S和R分别是置位和清零信号,低有效; D是信号输入端,Q信号输出端;

这里先说一下D触发器实现的原理:(假设S和R信号均为高,不进行置位和清零操作)

CP=0时: G3和G4关闭,Q3和Q4输出为’1’。那么G5和G6打开,Q5=D,Q6=/D。Q5,Q6

的信号随输入信号D的改变而变化; G1和G2构成一个SR锁存器,我们知道,当SR锁存器的S、R的输入均为高的时候,锁存器的输出保持不变,所以Q和/Q保持不变。

CP从0跳变为1时: G3和G4打开,Q3=Q6=/D,Q4=Q5=D。由SR锁存器的特性,Q=Q3=D,/Q=/D;CP=1时: 不管D怎么变化,Q3和Q4的信号都不会发生变化,所以输出也不会改变,具体原因由兴趣的可以推一下;下面就又重复CP=0的时刻了。

从上面的分析可以知道,输入信号D是在CP=0的时刻,经过与G5和G6两个与非门的延迟Tsu之后才传输到Q5和Q6端的,然后再CP跳变为1的时候被锁存到输出端的。

我们假设Tsu=5ns,如果D输入信号在CP跳变为1之前4ns(《5ns)的时候,才发生变化,那么在CP跳变为1时,输入信号D还没有传输到Q5和Q6,SR锁存器锁存的将是D变化之前的数据。也就是说D输入信号只有在CP跳变之前》Tsu的时间里准备好,触发器才能将数据锁存到Q输出端口,也就是所说的要保证信号的建立时间。

在CP跳变为1之后,Q5和Q6的信号要经过G3和G4两个与非门的延迟(Thd)才能传递到Q3和Q4,构成SR锁存器之前的D输入的阻塞,保证在CP=1是输入数据变化不会影响锁存结果。

我们假设Thd=5ns,如果D输入信号在CP跳变为1之后5ns内发生跳变,因为此时Q3和Q4还没发生变化,均为’1’,Q5和Q6的状态将会发生跳变。在CP=1的时刻,Q3和Q4跟随Q5、Q6的改变也发生跳变,末端SR锁存器的输出Q也发生跳变,造成输出结果不对。 也就是说在CP跳变为1之后的Thd时间内,D信号不能发生变化,也就是所说的要保证信号的保持时间(Thd)。

-

基于D触发器实现时钟电路同步设计2020-08-06 5529

-

如何实现半个时钟周期延时2015-04-27 6176

-

如何用D触发器实现2分频 原理2016-07-03 9744

-

用D触发器实现2倍分频的逻辑电路?2019-08-02 3313

-

D触发器怎么实现二分频电路?2020-03-02 6778

-

数字电路D触发器怎么实现状态机2020-04-03 4249

-

用D触发器实现延迟线的代码,仿真波形总是不对,帮忙看看代码有什么问题。2020-12-06 1960

-

D触发器2008-10-20 3228

-

D触发器实现二分频电路(D触发器构成的2分频电路)2009-06-12 81658

-

D触发器,D触发器是什么意思2010-03-08 5416

-

怎样使用D触发器实现二分频器2012-11-10 5272

-

verilog模型举例:利用D触发器实现时钟使能2021-10-01 8533

全部0条评论

快来发表一下你的评论吧 !