如何将电桥连接到激励电压和ADC

电子说

描述

将电桥连接到 ADC 通常需要在四线或六线电桥之间进行选择时,实施比例式测量。后面的章节更详细地讨论这些概念,并演示如何将电桥连接到激励电压和 ADC。

比例式测量

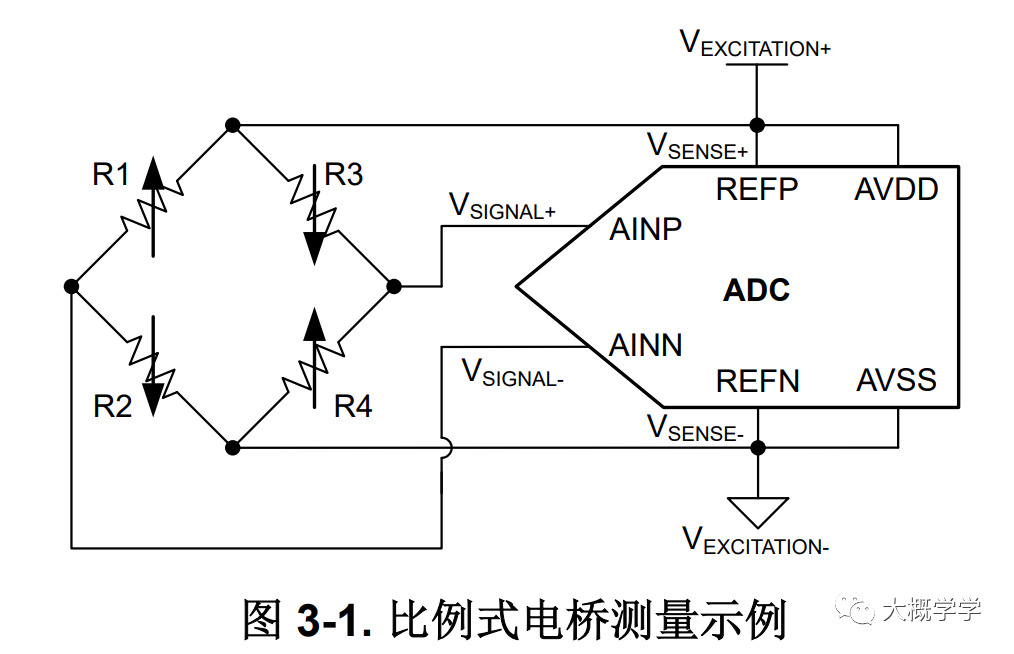

图3-1显示了通常如何使用比例基准配置进行电桥测量。电桥的输出由 ADC 进行测量,而单个电源被用作电桥激励电压和ADC基准电压。

ADC 对输入电压 VIN 采样,并将其与基准电压 VREF 进行比较。VIN 是 VSIGNAL+ 和 VSIGNAL–(或 AINP 和 AINN)之间的电压差,而 VREF 是 VSENSE+ 和 VSENSE–(或 REFP 和 REFN)之间的电压差。ADC 按照方程式 14 生成与 VREF 成正比的输出为:

方程式 14 用 AVDD 代替 VREF 项,因为在图 3-1 中 AVDD 连接到 REFP 并且 REFN 接地。还要注意,方程式 13 说明 VOUT 等于 VEXCITATION 乘以 ΔR 与 R 之比。在图 3-1 中,AVDD = VEXCITATION+ - VEXCITATION-,而 VOUT (Bridge) = VIN (ADC)。代入后可得出方程式 15:

用方程式 15 代替方程式 14 中的 VIN 项可得到方程式 16:

方程式 16 中的输出代码与 ΔR 成正比。此外,方程式 16 表明不需要 AVDD 和 VIN 的准确值。输出代码与电桥上的应变片成正比。比例式测量的一个优势是,测量值针对 VREF 的变化相对恒定。这在方程式 16 中也有体现,公式中的输出与 ΔR/R 成正比,因此与 VREF 或 VEXCITATION 的准确值无关。因此,比例式测量不太容易受 VEXCITATION 随时间和温度的漂移所影响。假设基准输入和测量输入中的噪声是相关的,那么 VEXCITATION 源中的任何噪声也应会抵消。通常,如果基准输入和测量输入的滤波器带宽相同,则上述噪声源就比较有相关性。

四线电桥

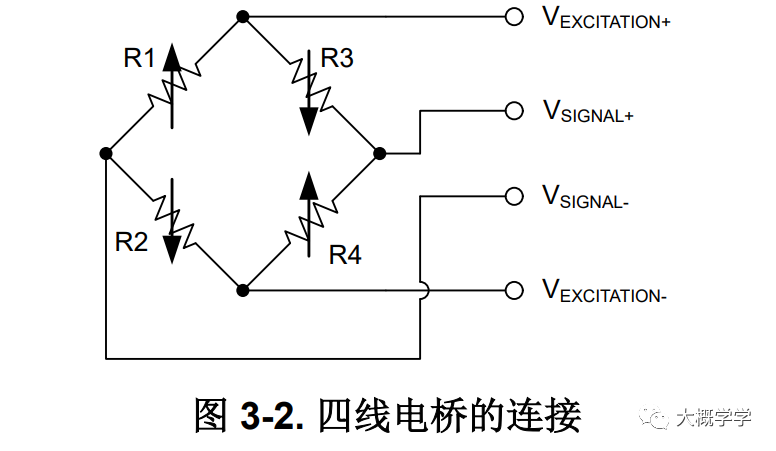

图 3-2 显示了四线电桥的连接。有两条线用于激励电桥(VEXCITATION+ 和 VEXCITATION–),两条线用于测量(VSIGNAL+ 和 VSIGNAL–)。ADC 测量差分电桥输出电压,ADC 正负基准输入分别连接到激励线路充当 VEXCITATION+ 和 VEXCITATION–。

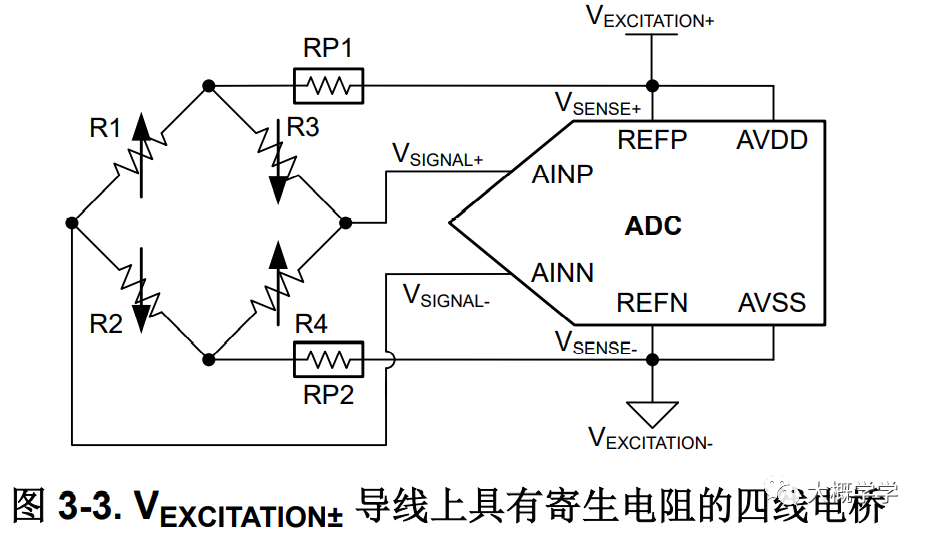

四线电桥适用于许多数据采集系统中的基本测量。但是,VEXCITATION+ 和 VEXCITATION– 的长导线可能具有不可忽略的电阻,增加 ADC 测量的误差。图 3-3 显示了一个与四线电桥相连的 ADC,电桥的激励导线上具有串联电阻 RP1 和 RP2。

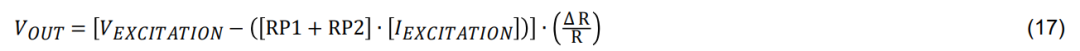

理论上,REFP 输入端的 VEXCITATION+ 和 REFN 输入端的 VEXCITATION– 与电桥的激励电压相同。不过,串联导线电阻会降低电桥本身的电压,从而改变电桥输出电压,如方程式 17 所示。

即使 RP1 和 RP2 很小,流过电桥的电流 (IEXCITATION) 也可能很大,从而导致显著的误差。例如,VEXCITATION = 5V 且电桥电阻为 350Ω 时,IEXCITATION = 14.3mA。即使 RP1 = RP2 = 1Ω,寄生电阻也会导致 0.6% 的测量误差。请注意,电桥输出(图 3-2 中的 VSIGNAL±)导线可能具有与 RP1和 RP2大小相同的串联电阻。但是,ADC 输入阻抗通常很高,通过 VSIGNAL± 拉出的电流比IEXCITATION小若干个数量级。因此,与 VSIGNAL± 导线电阻相互作用的任何电流所增加的误差可以忽略不计。

六线电桥

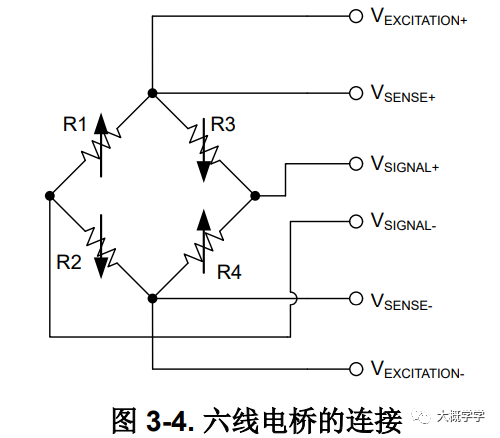

六线电桥可消除与四线电桥相关的导线电阻误差。六线拓扑结构具有与四线电桥相同的四条导线,同时它有额外的两条导线 (VSENSE±) 连接到电桥的顶部和底部。图 3-4 显示了六线电桥。

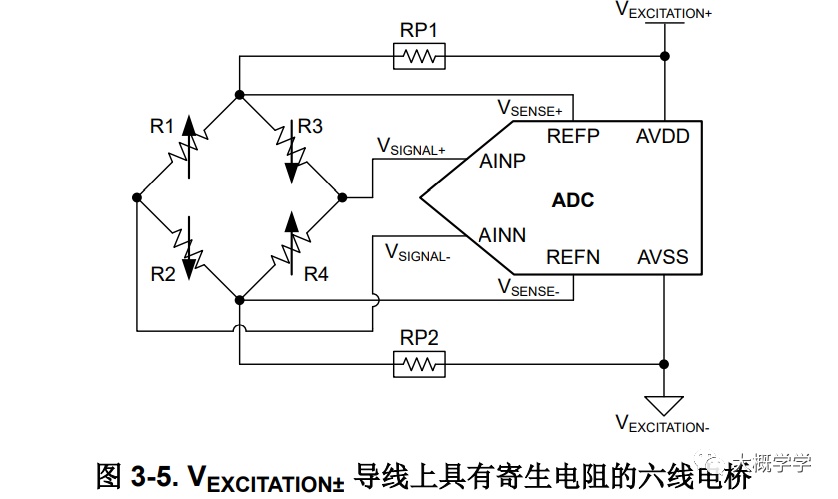

在此拓扑结果中,电桥顶部和底部的 VSENSE± 导线用作开尔文(或强制检测)连接,用于消除导线电阻的影响。此连接使用 VEXCITATION± 导线作为强制线路,将电压驱动至电桥。VEXCITATION± 可能是高电流,并在与电桥相连的寄生电阻两端产生压降,如节3.2所述。VSENSE± 导线通过绕过承载高电流的寄生导线电阻,用于准确测量电桥顶部的电压。同时,由于流过每条导线的输入电流小得多,VSENSE± 导线上的任何电阻会使电压误差显著降低。图 3-5 显示了六线电桥与ADC的连接方式,还显示了 VEXCITATION± 导线上的串联电阻。

使用六线电桥拓扑结构可确保 ADC VREF 与驱动电桥的电压相同。与四线拓扑结构类似,尽管流过这些导线的电流显著小于 IEXCITATION,VSIGNAL± 和 VSENSE± 导线上的电阻仍可能会增加误差。这个较低的电流会尽可能减小引入到 ADC 输入和基准通路的误差,从而提高系统总体精度(与四线电桥相比)。

审核编辑:汤梓红

-

如何将光敏电阻连接到Arduino板并读取电压2024-02-11 7517

-

如何将ADC连接到8051单片机?2023-07-07 5926

-

如何将Murata模块连接到EVK?2023-03-27 793

-

AN5027_如何将PDM数字麦克风连接到STM32单片机2022-11-21 1033

-

如何将手机连接到Azure IoT Central2022-11-01 1010

-

如何将PCF8591 ADC模块与Raspberry Pi连接2022-08-26 5807

-

如何将网关连接到TTN服务器2021-08-23 2007

-

EE-37:如何将LCD连接到21xx和2106x系列DSP2021-04-14 891

-

如何将高速ADC与串行LVDS输出连接到virtex 7 fpga?2020-07-26 3275

-

如何将树莓派网关与外网连接——手把手教你如何将树莓派网关连接到服务器之第三篇2020-04-16 3013

-

如何将SCLUB的输出连接到内部ADC Delsig的输入?2019-06-28 2180

-

如何将Arduino板连接到的计算机上的30个项目2018-12-11 1781

全部0条评论

快来发表一下你的评论吧 !