电磁干扰(EMI)设计中元件的选择

EMC/EMI设计

描述

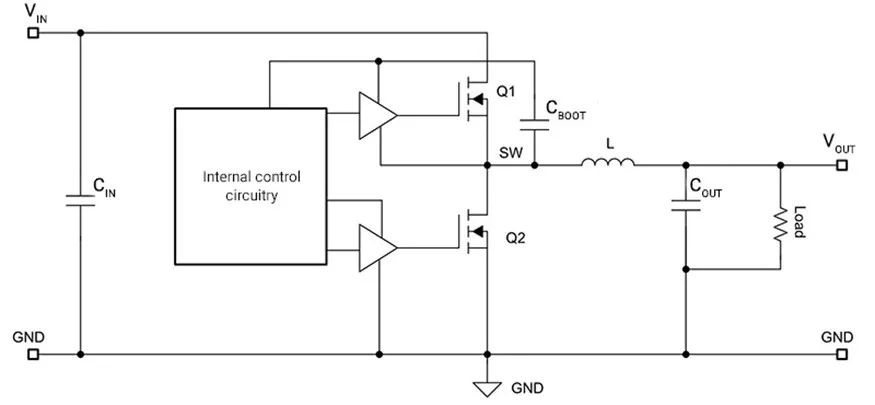

在实现高效紧凑设计的同时遵守国际无线电干扰特别委员会 (CISPR) 等组织提出的严格电磁干扰 (EMI) 要求是一项挑战。因此,元件的选择成为设计过程的关键。与大多数设计决策一样,在不同元件之间进行选择几乎总是归结为基于关键设计目标的权衡评估。降压稳压器以高效率和良好的热性能著称,但通常不被视为具有低 EMI。幸运的是,您有多种选择来降低此类稳压器产生的 EMI。为方便进一步讨论,图 1 展示了降压稳压器的简化原理图。

图 1:降压稳压器简化原理图

电路板布局布线注意事项

当设计必须符合 EMI 要求时,除了选择适当的无源器件值确保功能设计之外,电路板布局布线应该是需要考虑的首要因素。有两个降压稳压器电路板布局布线通用规则可帮助有效降低 EMI:

使输入电容器和自举电容器尽可能地靠近集成电路的 VIN 和 GND 引脚,从而更大程度地减少高瞬态电流 (di/dt) 的环路面积。

尽可能减小开关节点的面积,从而更大程度地减小高瞬态电压 (dv/dt) 节点的表面积。

电路板布局布线无法实现优化时,还有其他选项。要详细了解其他选项,请前往 TI E2E 中文支持论坛,阅读技术文章《器件级功能和封装选项如何帮助有效降低汽车设计中的 EMI》。

集成输入电容器

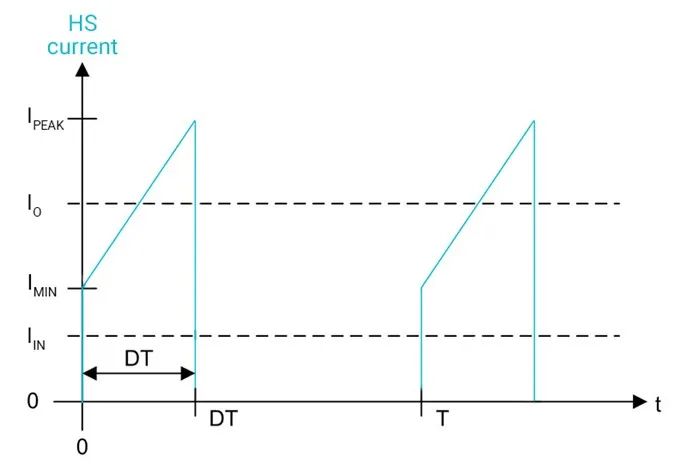

如前所述,在 EMI 要求限制之下进行开关稳压器的设计时,减小高瞬态电流 (di/dt) 环路的面积非常重要。在降压稳压器中,需要从 EMI 的角度考虑输入电压对地环路。降压稳压器通过开启和关断电源连接将较高的直流电压降为较低的电压,从而在高侧产生金属氧化物半导体场效应晶体管 (MOSFET) Q1 电流,如图 2 所示。

图 2:降压稳压器的输入电流波形

MOSFET 快速开启和关闭,产生由输入电容器提供的非常尖锐且几乎不连续的电流。某些器件,例如 TI 的 3A LMQ66430-Q1 和 6A LMQ61460-Q1 36V 降压稳压器,在封装内集成高频输入电容器,从而尽可能减小输入电流环路的面积。减小输入电流环路的面积可降低输入端的寄生电感,从而减少电磁能量的输出。

集成自举电容器

需要考虑的另一个高瞬态电流 (di/dt) 环路就是自举电容环路。自举电容器负责在导通期间为高侧 MOSFET 栅极驱动器提供电荷。内部电路在关断期间对该电容器重新充电。高侧 MOSFET 的源极端子连接至开关节点而不是 GND。将自举电容器连接到 MOSFET 的源极引脚可确保栅源电压 (VGS) 足够高以开启 MOSFET。对于大多数降压稳压器,必须在电路板上留出一些可用的开关节点区域来连接自举电容器,尽管这在通过尽可能减小开关节点面积来降低 EMI 过程中可能产生适得其反的效果。通过在封装内集成自举电容器,LMQ66430-Q1 不仅遵循之前提到的两个规则,同时还减少了对外部元件的需求。

结语

在严格的 EMI 要求下实现空间紧凑的电源设计并不简单。具有集成电容器的降压稳压器可以使符合 EMI 要求的设计实现起来更容易,同时还有助于减少整体外部元件的数量。

审核编辑:汤梓红

-

电磁干扰的检测仪器选择 EMI电磁干扰的常见误区2024-11-20 2385

-

收藏这篇,轻松拿捏电磁干扰EMI2024-08-30 3193

-

EMI电磁干扰厂家:如何专业解决电磁干扰问题2024-05-13 1281

-

EMI电磁干扰:EMI电磁干扰的识别与解决之道2024-04-25 2833

-

EMC与EMI:电磁兼容与电磁干扰的原理与影响2024-04-09 2183

-

【EMI测试】EMI测试中传导骚扰是什么意思?和辐射干扰有啥区别?#电磁干扰 #电路知识 #EMI测试安泰小课堂 2023-11-30

-

如何抑制MEI电磁干扰传导?如何选择EMI滤波器?2023-11-29 1710

-

EMI(电磁干扰)对策有哪些?2023-02-08 4730

-

EMI电磁干扰的来源和分类2022-01-06 1064

-

EMI电磁干扰有哪些类型2021-12-28 1920

-

电磁干扰EMI的原理及产生2020-05-15 11034

-

EMI电磁干扰的传播过程2019-05-31 1884

-

OrCAD中对原理图中元件的基本操作2011-12-02 13984

全部0条评论

快来发表一下你的评论吧 !