同步计数器的基本概念及工作原理

描述

计数器可以定义为用于根据发生的事件对特定事件进行计数的设备,计数器在计算机或数字逻辑系统中的主要作用是根据CLK信号计算和存储过程或事件发生的次数。

最常见的计数器类型是包含单个CLK和多个输出的时序逻辑电路。这里的输出用二进制代码表示二进制或十进制数字。每个CLK信号要么增加数量,要么减少数量。按照计算方式的不同,计数器可以分为多个种类,例如同步计数器、异步计数器等。在本文中,小编简单介绍下同步计数器的电路图、主要类型及工作原理。

基本概念

使用时钟信号改变其转换的计数器称为“同步计数器”,这意味着同步计数器依赖于它们的时钟输入来改变状态值。在同步计数器中,所有触发器都连接到相同的时钟信号,所有触发器将同时触发。此计数器的另一个名称是同时计数器,该计数器没有传播延迟和涟漪效应。

与同步计数器相比,异步类型的计数器设计非常简单,但异步计数器有最大工作频率的限制。为了克服这个限制,但异计数器主要是通过提供同步时钟来设计的,因此输出通过时钟的输入同步变化。

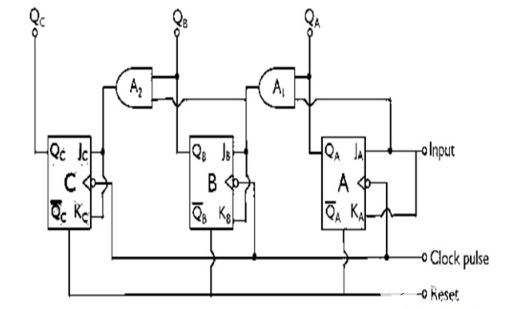

下面是一个3位同步计数器的电路图,该电路设计有2个AND逻辑门,3个JK触发器和一个用于启用触发器的CLK信号。

在该电路中,向触发器A的输入端提供高电平有效信号。因此,它在每个CLK输入的下降沿触发。类似地,AND门被提供给触发器-B,在这种情况下,输出主要取决于先前的触发器输入和输出B。一旦AND门打开,触发器B将在触发器A输出为高电平时简单地切换。

这时候,触发器C的输入将成为第二个AND门的输出。因此,一旦A2逻辑门被激活,触发器C就会触发。当A1逻辑门和触发器-B的输出为高电平时,A2逻辑门将被激活。

其电路工作过程简单的表示如下:

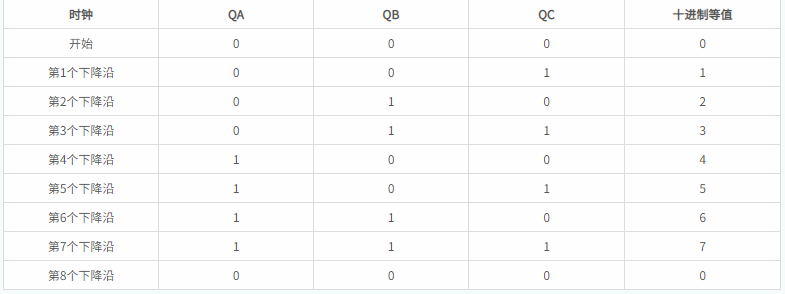

在电路开始时,触发器排列在0,三个触发器输出将为零,即QCQBQA=000。但在主CLK信号的下降沿,触发器A输出切换从零到一。所以在触发器 B和C 处,不会发生任何变化,因为这两个触发器的输入端都是0,直到下一个CLK信号到来。

在提供第一个CLK信号时,触发器的输出将为QCQBQA =001。在应用第二个时钟信号之前,由于栅极A1输出为高电平,因此A和B输入等触发器均为 1。因此,在第二个CLK信号的下降沿,两个触发器将再次切换。因此,这会将 FFA 输出从1更改为0,并将FFB输出从0更改为 1。因此,输出将是 010;A1和A2等逻辑门都将关闭。

一旦应用了第三个时钟信号,触发器A的输出将翻转,逻辑门A1和A1将打开,因此输出将为011。一旦应用了第四个时钟信号,则所有三个FF输入将是在电路中高。因此,第四个触发器的下降沿将触发所有触发器输出,从而将QA和QB更改为0,QC更改为1。因此,这个特定CLK信号的整体o/p将为100,因此逻辑门A1和A2将被关闭。

一旦出现下一个CLK信号,然后在第五个CLK信号的下降沿,触发器-A 输出将再次从低电平切换到高电平。结果,输出QCQBQA将为10,因此逻辑门 A1和A2将被激活。

最后施加第六个CLK信号,触发器A在其下降沿从1切换到0。触发器B的输入也因此为高电平,其输出从0切换到1。因此,在这种情况下,QCQBQA将为110。此外,此过程将继续,在第8个CLK信号的下降沿,所有触发器输出(即QCQBQA)将重置为000。

注意:在同步计数器中,一次复位电路中的所有触发器非常重要,计数器设置时间等于电路内每个触发器的传播延迟。所以,同步计数器可以通过一个高频CLK信号来控制。

真值表

3位同步计数器基于上述说明的真值表:

主要类型

在数字电子电路中,有不同类型的同步计数器,分别是:

二进制计数器

4 位同步递增计数器

4位同步递减计数器

4位同步加减计数器

可加载计数器

BCD计数器

环形计数器

约翰逊计数器

下面简单介绍几个比较常用同步计数器的工作过程。

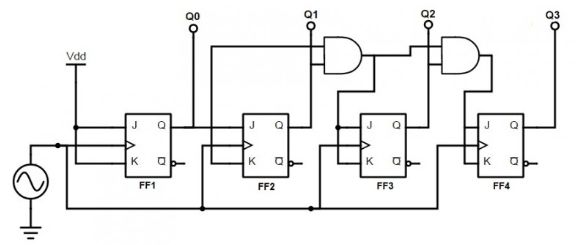

1、4位同步递增计数器

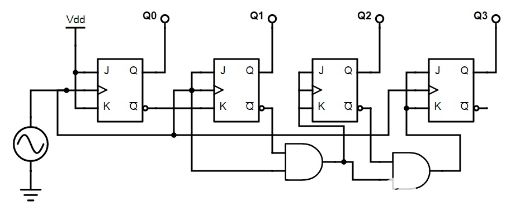

下图所示的4位递增计数器是使用JK触发器设计的,外部时钟脉冲与所有触发器并联。对于计数器的设计,首选选择JK触发器。使用JK触发器的意义在于,如果两个输入都为高电平,它可以切换其状态,具体取决于时钟脉冲。

第一个触发器的输入连接到HIGH(逻辑1),这使得触发器在每个时钟脉冲进入它时进行切换。因此同步计数器将使用单个时钟信号并随着每个脉冲改变其状态。

第一个JK触发器 (Q) 的输出连接到第二个触发器的输入。AND门(外部连接)驱动其他两个触发器的输入。这些与门的输入由前一级触发器输出提供。

如果FF2的输入直接连接到FF1的Q1输出,则计数器将无法正常工作。这是因为,Q1值在计数为210时为高电平,这意味着FF2触发器将为第三个时钟脉冲切换。这会导致错误的计数操作,计数为710而不是 410。

为了防止这个问题,在FF2和FF3 的输入端使用了AND门。只有当Q0、Q1输出为高时,AND门的输出才会为高。因此,对于下一个时钟脉冲,计数将为00012。

类似地,当Q0、Q1和Q2为高电平时,触发器FF3将触发第四个时钟脉冲。Q3输出在第8个时钟脉冲之前不会切换,并将再次保持高电平直到第16个时钟脉冲。在第16个时钟脉冲之后,所有触发器的q输出将返回0。

工作原理过程如下:

在递增同步计数器中,4位二进制序列从0000开始递增到1111。所以在了解上述递增计数器电路的工作之前,可能需要JK触发器有所熟悉。

在上述电路中,触发器的两个输入连接在一起。因此,只有两种可能的情况会发生,即两个输入要么是高电平,要么是低电平。如果两个输入为高,则JK触发器切换,如果两者均为低,JK触发器会记住,即它保持在先前的状态。

下面介绍下它的工作过程(其实类似上面的3位同步计数器)。另外,这里的时钟脉冲表示边沿触发的时钟脉冲。

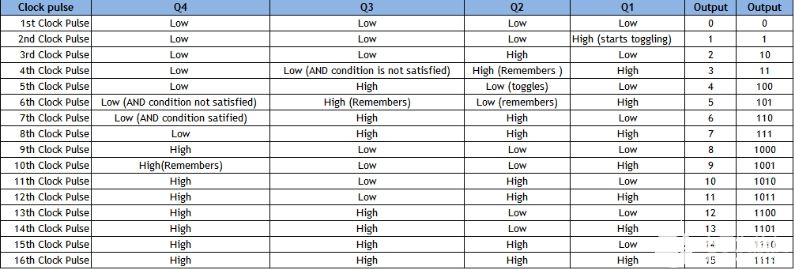

在第一个时钟脉冲中,所有触发器的输出都为0000。

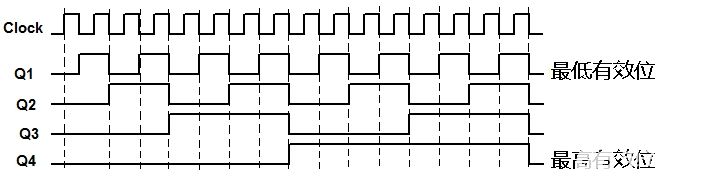

在第二个时钟脉冲中,由于J和K的输入连接到逻辑高电平,JK触发器(FF0)的输出改变其状态。因此,第一个触发器(FF0)的输出改变其状态为每个时钟脉冲。在下面的时序图中可以看到,最低有效位(LSB)交替改变其状态。从而产生-0001

在第三个时钟脉冲中,下一个触发器 (FF1) 将接收其JK输入,即(逻辑高)并改变其状态。在此状态下,FF0将其状态更改为0。因此FF1上的输入为0。因此输出为-0010。

同样,在第四个时钟脉冲FF1不会改变其状态,因为它的输入处于低电平状态,它保持在其先前的状态。尽管它向FF2产生输出,但由于AND门的存在,它不会改变其状态。FF0将再次将其输出切换到逻辑高状态。因此输出为0011。

在第五个时钟脉冲中,FF2接收输入并改变其状态。同时,FF0的输出将具有低逻辑,FF1也将处于低状态,产生0100。

这个过程一直持续到1111。

4位递增同步计数器的真值表如下图所示,可以清楚的说明上述工作过程:

上图表示4个触发器Q1、Q2、Q3、Q4的输出。第一个触发器在每个边沿触发脉冲上切换,而第二个触发器仅在其输入在给定时钟脉冲时为高电平时触发。如果两个输出Q1和Q2为高电平,则第三个触发器切换。同样,如果所有三个Q1、Q2、Q3 都为高电平,则Q4将切换。这样,再次达到零后,三个触发器切换到逻辑低电平,即0000并再次开始计数。

4位递增同步计数器时序图如下所示:

2、4位同步递减计数器

递减同步计数器按递减顺序计算数字,类似于递增计数器,不同的是减少其计数。所以JK触发器的输入连接到反相Q(Q')。下图所示的4位递减计数器是使用JK触发器设计的。相同的外部时钟脉冲连接到所有触发器,如下所示:

由于计数器必须对序列进行倒计时,因此最初所有输入都将处于高电平状态,因为它们必须对序列进行倒计时。它将以1111开始并以0000结束,类似于递增计数器。

在递减计数器中,应该记住,只有当前触发器在其输出端产生低逻辑时,前触发器才会切换。

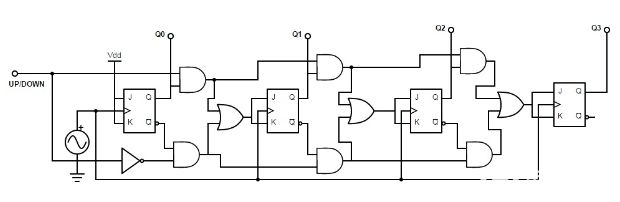

3、4位同步加/减计数器

将上述两个计数器合在一起在称为同步加/减计数器,这可以从它的输入中选择。带有JK触发器的加/减同步计数器的设计如下所示:

加/减计数器是通过2输入AND门具有“加”和“减”计数模式,用于检测计数操作的适当位数条件。OR门用于组合来自每个JK触发器的ADN门的输出。

这里还提供了一条上/下控制线,它使上或下系列AND门能够将JK触发器Q 、 Q' 的输出传递到级联布置中的下一级触发器。如果向上/向下控制线设置为高电平,则顶部与门处于启用状态,电路充当向上计数器。如果向上/向下控制线设置为低电平,则底部与门处于启用状态,电路充当向下计数器。

主要应用

同步计数器的应用包括以下几个方面,简单列举下:

机器的运动控制

电机转速计数器

旋转轴编码器

脉冲发生器

数码时钟

报警系统

数字手表

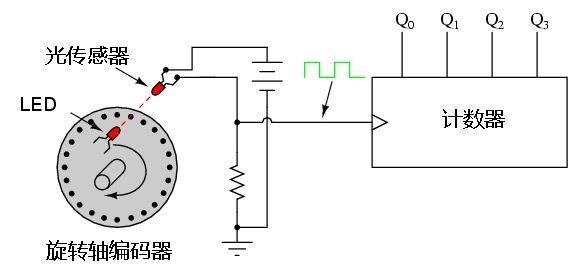

其中,最常见和众所周知的应用是机器运动控制,即旋转轴编码器将机械脉冲转换为电脉冲的过程。这些脉冲将作为加/减计数器的时钟输入,并启动电路运动。其典型的电路如下:

该电路由光电晶体管或光传感器和连接到转子轴的LED组成。这种安排连接到加/减同步计数器。当机器开始移动时,它通过连接和干扰(接通和断开)光传感器和LED之间的光束来转动编码器轴。

通过这种运动,转子产生时钟脉冲以增加向上/向下计数器电路的计数。因此,计数器会降低轴的运动并给出转子移动了多少距离的值。

为了计算转子轴的运动,这里通过沿一个方向移动轴来增加计数,并通过沿另一个方向移动来减少计数。因此,还使用了编码器/解码器电路来区分运动方向。

优缺点

同步计数器的优点包括以下几点内容:

与异步计数器相比,设计简单。

可以同时工作。

基本上没有传播延迟。

计数系列通过逻辑门控制。

更快的操作。

同步计数器的主要缺点是,它需要大量额外的逻辑来执行:

所有触发器都通过单个或公共CLK信号驱动。

需要大型组件和电路。

使用复杂的逻辑电路和比较多的状态。

总结

以上就是同步计数器电路、类型及工作原理等相关内容的介绍。不难发现,与异步计数器相比,同步计数器电路设计非常简单。更重要的是,所有触发器的CLK 输入都以相同的CLK信号相互计时,因此所有输出状态将同时改变或切换。

目前,同步计数器在数字电子电路中应用非常广泛,其特点是大大提高了计数器工作频率,可以高效的实现数字测量、逻辑运算和机电控制。

-

计数器同步和异步怎么判断2024-07-23 3823

-

二进制串行计数器工作原理是什么?2024-05-28 2319

-

同步计数器的主要类型和工作原理2024-05-24 3484

-

同步计数器和异步计数器各有什么特点2023-12-15 3515

-

同步计数器和异步计数器的区别主要在哪里2023-12-13 16276

-

同步计数器和异步计数器是什么 同步计数器和异步计数器的主要区别?2023-03-25 30244

-

单片机计数器工作原理及讲解2022-10-08 6259

-

计数器的结构和工作原理2022-01-24 1320

-

USB基本概念及从机编程方法介绍2021-11-08 1943

-

定时器的基本概念及初始化配置硬件2021-08-19 1193

-

电子计数器工作原理_电子计数器组成及各部分功能2019-09-26 38713

-

计数器,计数器的工作原理是什么?2010-03-08 62512

-

定时器/计数器的结构和工作原理2009-03-29 20444

-

十进制计数器工作原理2008-01-21 30955

全部0条评论

快来发表一下你的评论吧 !