JK触发器的工作原理及竞态条件

描述

JK触发器也称为通用可编程触发器,因为使用其J、K输入具有预置和清除功能,它可以模仿任何其它触发器的功能。

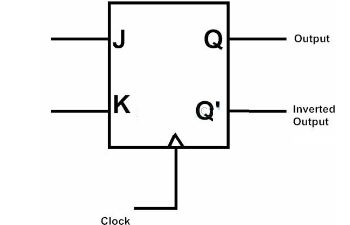

JK触发器是对SR触发器的修改,它没有非法状态。其中J输入类似于SR触发器的SET输入,K输入类似于SR触发器的RESET输入,其符号如下所示:

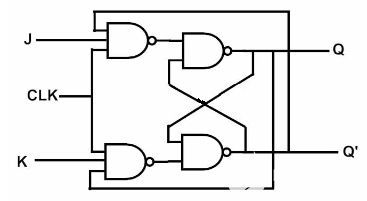

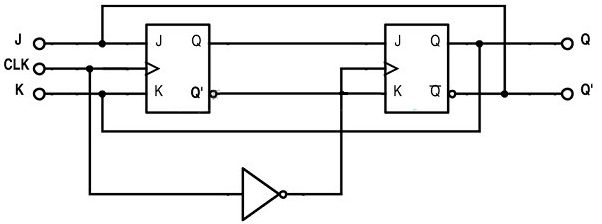

逻辑图

如上所述,JK触发器是SR触发器的修改版本,所以它的逻辑图如下图所示,它是由三输入NAND门组成,取代SR触发器中的两输入NAND门,输入S和R被J和K取代。

JK触发器的设计是这样的,一个三输入NAND门是J,时钟信号和来自Q'的反馈信号,另一个三输入NAND门是K,时钟信号以及来自Q的反馈信号。这种布置消除了SR触发器的不确定状态。

工作过程如下:

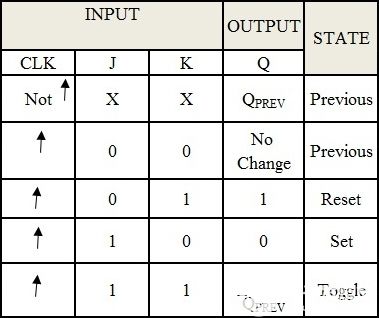

情况1:当输入J和K均为低电平时,Q返回其先前的状态值,即它保存先前的数据。当向JK触发器施加时钟脉冲并且J输入为低电平时,无论其他与非门如何,与非门1的输出变为高电平。同样,如果K输入为低电平,则与非门2的输出也为高电平。因此,输出保持在相同的状态,即触发器状态没有变化。

情况2:当J为低电平且K为高电平时,触发器将处于复位状态,即Q = 0,Q' = 1。当向JK触发器施加时钟脉冲并且输入J为低电平且K为高电平时,连接到J输入端的NAND门的输出变为1,然后Q变为 0。这将再次将触发器重置为之前的状态状态。所以触发器将处于复位状态。

情况3:当J为高电平且K为低电平时,触发器将处于置位状态,即Q = 1,Q' = 0。当向JK触发器施加时钟脉冲并且输入J为高电平且K为低电平时,连接到K输入端的NAND门的输出变为1。然后Q'变为0,这会将触发器设置为高电平时钟输入。因此触发器将处于SET状态。

情况 4:当输入J和K都为高电平时,触发器处于Toggle状态,这意味着输出将补充先前的状态。

JK触发器的真值表如下所示:

JK触发器的竞态条件(Race Around Condition)

对于JK触发器的高输入,只有较低的与非门由相互互补的输出(即Q和Q')触发。因此,当高输入连接到触发器时,在任何时刻,一个门被启用,另一个门将被禁用。如果上门处于禁用状态,它会将触发器驱动到SET状态,稍后当下门启用时,它将驱动触发器到RESET状态,从而会导致输出切换。这将导致JK触发器中出现竞态条件(Race Around Condition)。

如何避免竞态条件

可以通过将时钟开启时间设置为小于触发器的传播延迟来避免竞态条件,其实这可以通过边沿触发来实现。

通过使触发器在一个时钟周期内进行切换。这个概念是在主从JK触发器中引入的。

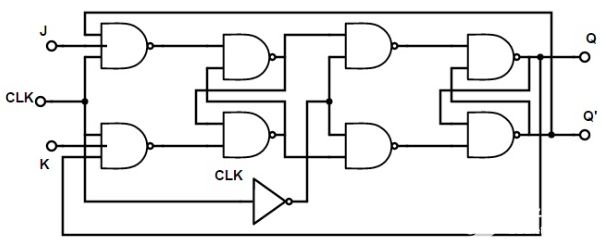

主从JK触发器

主从JK触发器是一种“同步”器件,它允许数据随时钟信号的时序传递。主从触发器由两个串联的时钟触发器组成,它们将输入与输出隔离,因此称为“主从”。主从JK触发器除了消除普通JK触发器的竞态问题外,还可以模仿SR触发器、时钟触发器、D触发器和Toggle触发器的功能。因为它从触发器的Q 和 Q' 输出反馈到主触发器,而主触发器的输出作为输入之一连接到从触发器。

当时钟输入为高电平时,主触发器处于活动状态,从触发器处于非活动状态。根据输入,主触发器的输出被置位或复位,而从触发器的输出不变,因此它保持在先前的状态。随着从触发器在低时钟输入下激活,从触发器的输出发生变化。当时钟为高电平时,主触发器的输出被搁置,因为在此期间从器件处于非活动状态。当时钟为低电平时,主触发器的输出被从触发器看到并将它们传递给输出。从触发器的输出是主从触发器的最终输出。最终输出在时钟脉冲结束时可用。

主从JK触发器是两个SR触发器的级联组合,其反馈从从器件的输出到主器件的输入,其电路如下图所示:

正时钟脉冲被施加到主触发器,它们在施加到从触发器之前被反转,即主触发器在正转换期间有效,而从触发器在负转换期间有效。在时钟的上升沿期间,来自输入J和K的数据被传递到主触发器并保持在那里直到时钟出现下降沿。然后将数据或信息传递给从触发器,在这里收集输出。

带有两个JK触发器的主从JK触发器的符号表示如下所示。

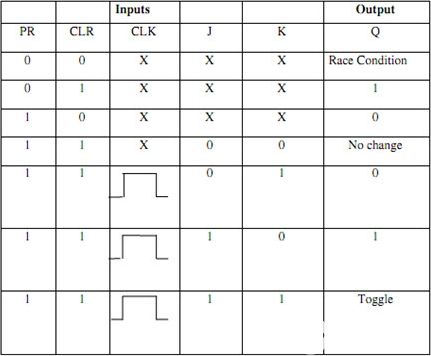

主从JK触发器的真值表以及预设和清除输入如下所示:

当时钟输入为低电平时,主触发器的两个输入即J和K输入对主从触发器的输出没有影响。

当时钟输入为高时:

如果 J 低且 K 低:状态没有变化。

如果 J 为低且 K 为高:主从触发器将处于复位状态。

如果 J 为高且 K 为低:主从触发器将处于置位状态。

如果 J 高且 K 高:切换状态。

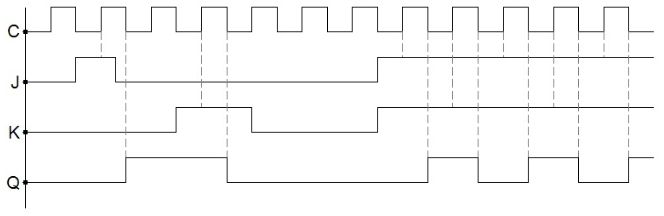

时序图如下所示:

输入脉冲的宽度可以小于或大于触发器的传播延迟,它不影响输出状态。但是如果不违反建立和保持时间,时钟上升沿时刻的J和K输入值会影响主从触发器的输出状态。

主要应用

JK触发器是数字电子产品中使用最广泛的触发器之一,这是因为它们的通用可编程特性,其一些主要应用包括:

移位寄存器

分频器

开关应用

并行数据传输

串行数据传输

二进制计数器

序列检测器

总结

JK触发器是数字电路触发器中的一种典型的电路单元,具有置0、置1、保持和翻转功能。在各类集成触发器电路中,JK触发器的功能最为齐全。而在实际应用中,它不仅有很强的通用性,而且能灵活地转换其它类型的触发器,因此其应用是非常的广泛。

-

怎么用jk触发器变成t触发器2024-08-28 6468

-

jk触发器上升沿和下降沿怎么判断2024-07-23 6725

-

t触发器和jk触发器的区别和联系2024-02-06 8162

-

jk触发器是上升沿还是下降沿触发2024-01-11 12318

-

JK触发器逻辑符号_jk触发器的特性方程2019-11-08 97494

-

主从jk触发器工作原理2019-08-05 44020

-

jk边沿触发器工作原理2018-01-30 38735

-

jk触发器是什么原理_jk触发器特性表和状态转换图2017-12-25 192882

-

JK触发器,JK触发器是什么意思2010-03-08 7617

-

CMOS触发器的结构与工作原理2009-10-17 8032

-

主从jk触发器电路及工作原理2008-01-21 18599

全部0条评论

快来发表一下你的评论吧 !