使用输入晶体管设计的或非门

描述

或非门(NOR Gate)是逻辑门,也是通用门之一,用于构造类似于AND Gate的基本门。通过组合非门和或门,可以构造或非门。或非门的输出是或门的反转。通常情况下,或非门有2个输入,比如X和Y,以及一个输出Z。

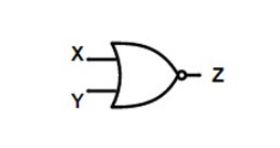

或非门逻辑符号如下图所示:

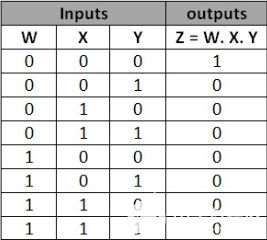

或非门运算的逻辑数学表达式为 Z =(X+Y) ̅。其中, ̅表示反向运算。

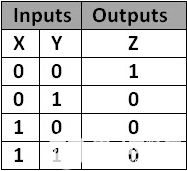

另外,或非门的真值表如下图所示,它表明如果两个输入都处于低逻辑电平,则或非门输出逻辑高值。如果其任何输入处于高逻辑电平,则会产生逻辑低值。

使用输入晶体管设计的或非门

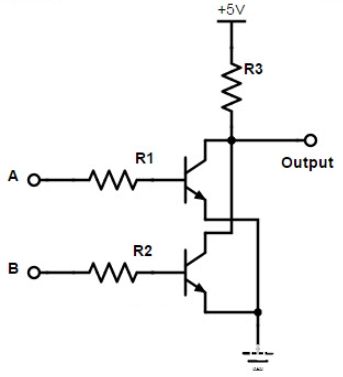

在两个输入或非门中,两个晶体管用于设计一个或非门。+6伏的电路驱动电压连接到第一个晶体管的集电极。相同的电源电压也将并联到第二个晶体管的集电极。连接两个电阻作为或非门的输入(每个10K)。两个晶体管的发射极共同接地。输出在电源电压、电阻和第一个晶体管的集电极节点处收集。

使用两个晶体管设计的2输入或非门逻辑门如下图所示:

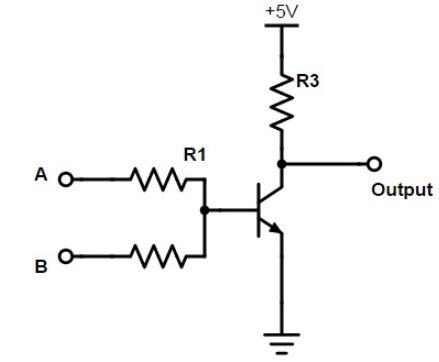

此外,或非门还有另一种设计方法,即单晶体管设计的或非门。在这里,晶体管的基极通过电阻为并联的两个输入供电。发射极接地,集电极连接到+6伏的电路驱动电压(电源电压)。输出在晶体管的集电极端收集,如下图所示:

上图是实现NOR逻辑门的另一种方法。

或非门的脉冲操作

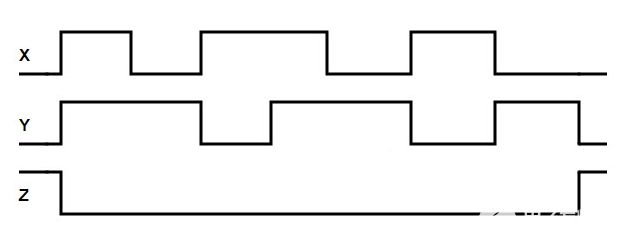

如果应用2个不同的时钟信号作为或非门X和Y的输入,那么或非门的输出将如下图所示(X、Y为输入,Z为输出):

观察上述时钟信号,可以发现,当两个输入都为高电平时,或非门的输出为低电平,并且每个输入逻辑低电平都保持低电平输出状态。在时钟脉冲结束时,输出变为高电平,因为或非门的两个输入端都为低电平。

通用或非门

或非逻辑门被称为“通用逻辑门”,只需在其输入端进行一些更改,该门就可以用作任何基本逻辑门。但大多数情况下,我们更喜欢NAND门而不是NOR门来设计其它基本逻辑门。接下来看看如何使用或非门设计其他门。

1、仅使用或非门的基本逻辑门

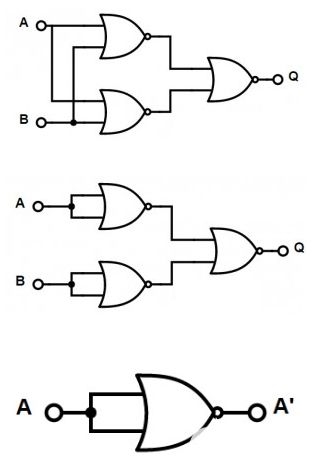

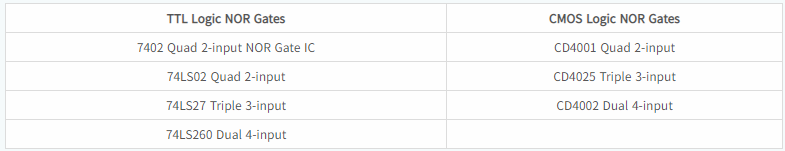

其实或非门可以设计基本的逻辑门,例如AND、OR、NOT门。或非门执行所有3种类型的基本逻辑门如下图所示:

2、3-输入或非门

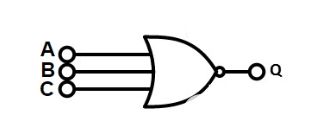

多输入或非门可以通过在其输入侧连接其他逻辑门来设计。下面来看看3输入或非门的逻辑符号和真值表,其中布尔表达式没有随着输入数量的变化而变化,或非门的输出是或非门输入加法的倒数。

3-输入或非门符号:

3-输入或非门的布尔表达式为Q = (A+B+C) ̅。

3-输入或非门的真值表如下:

当所有3个输入为高电平时,3个输入或非门的输出为低电平,而对于所有其他输入组合,它将为高电平。

3、4-输入或非门

与3输入或非门类似,也可以设计4输入或非门,其符号如下图所示:

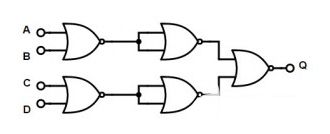

4输入或非门的布尔表达式是:

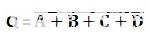

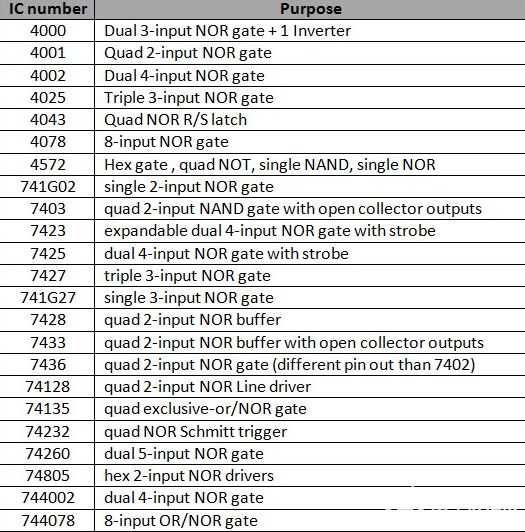

常用的TTL和CMOS逻辑或非门IC

下面给出了所有TTL和CMOS逻辑NOR门的IC列表:

一些最常用的或非门IC是:

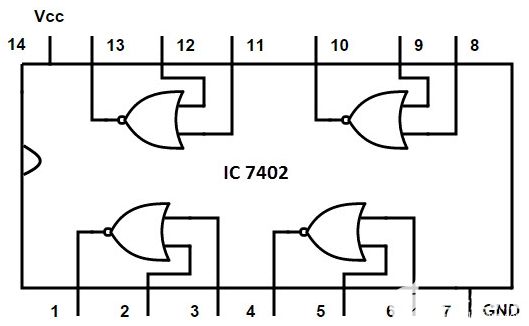

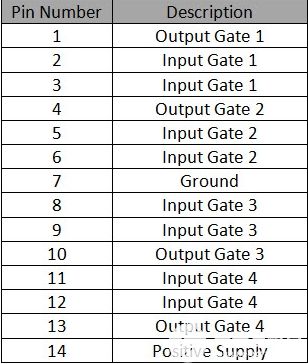

Pin引脚配置图如下所示:

引脚说明如下图所示:

主要应用

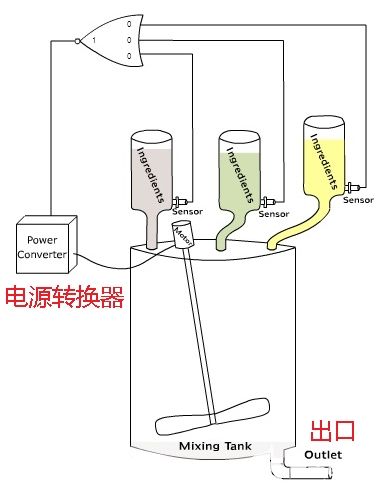

逻辑或非门可用于构建异或门和其他一些实时应用,它的实时应用之一是“混合搅拌罐(Mixer tank)”,下面简单介绍下。

观察下图,可以使用3输入NOR门来控制搅拌罐的成分流动。不同种类的成分储存在单独的圆柱形桶中,电容式接近开关布置在每个圆柱体的底部,位于其底部,这是为了检测成分的数量或水平。

当配料下降到传感器水平时,气缸产生高电平逻辑输出。高于传感器的成分电平将被视为低逻辑电平(0)。当所有成分下降到传感器电平时,或非门的所有输入都将变为高电平。

当所有成分下降到传感器电平时,或非门的输出将变为高电平。其中输出连接到电源转换器,电源转换器连接到Motot(混合成分)。NOR逻辑门的高输出激活电源转换器并激活电机,使电机运转并混合所有成分。

总结

不看看出,或非门是数字逻辑电路中的基本元件,实现逻辑或非功能。有多个输入端,1个输出端,多输入或非门可由2输入或非门和反相器构成。只有当两个输入A和B为低电平(逻辑0)时输出为高电平(逻辑1)。

需要注意的是,在实际使用过程中,由于或非门作为开关的打开速度相对较慢,所以人们更愿意用与非门(AND Gate)。

-

手把手教你用晶体管搭建逻辑门电路2023-05-30 26938

-

如何用晶体管搭建常见的逻辑门电路2023-04-26 15161

-

双4输入或非门-HEF4002B2023-03-03 626

-

四路2输入或非门-74LV022023-02-27 829

-

四路2输入或非门-74ALVC022023-02-15 599

-

2输入或非门-XC7SH022023-02-10 543

-

【数字电路】关于逻辑或非门系统特性分析教程2021-01-22 4968

-

用晶体管搭建常见的逻辑门电路2020-11-01 17545

-

用二极管继电器组成的4输入或非门2018-03-29 6981

-

或非门芯片2011-11-09 49140

-

二极管.晶体管或非门电路图2010-03-29 4773

-

或非门,或非门是什么意思2010-03-08 10396

全部0条评论

快来发表一下你的评论吧 !