数字IC与数字IC前端设计

电子说

1.4w人已加入

描述

数字IC是传递、加工、处理数字信号的集成电路(Integrated Circuit, IC), 一般将其分为通用数字IC和专用数字IC。

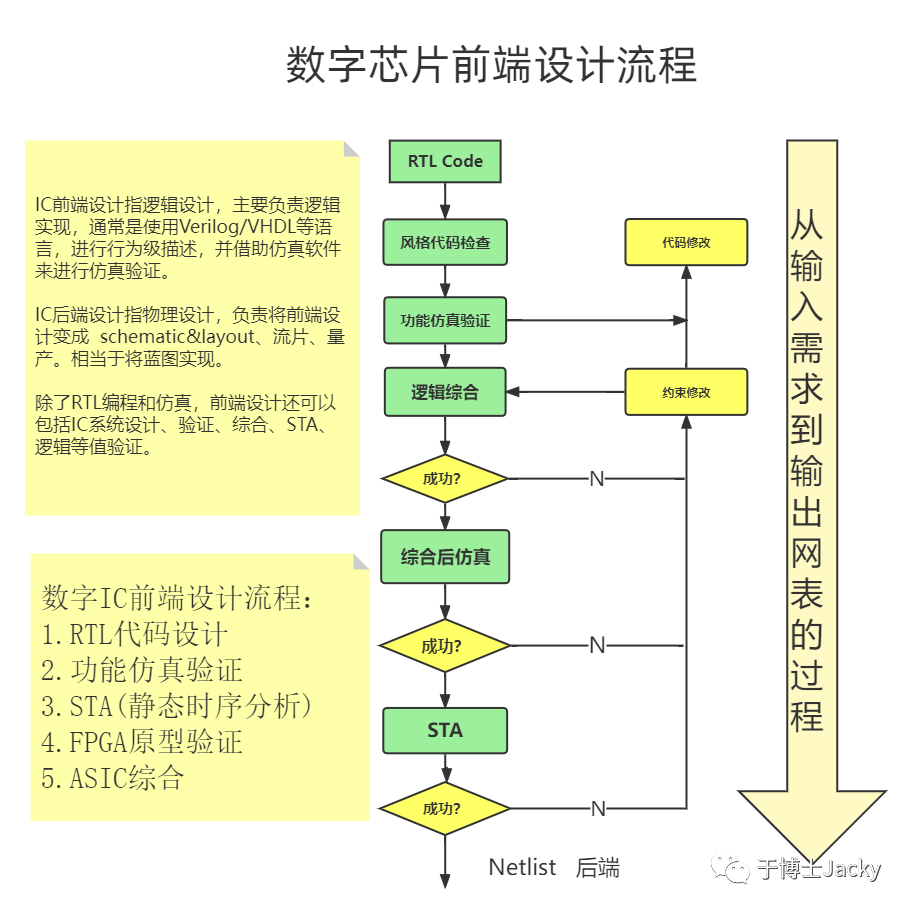

数字IC前端设计,以架构设计为起点,以生成可布局布线的网表级为终点。该过程主要包括:TRL编程、仿真验证、逻辑综合(Design Compiler)、静态时序分析(STA)、形式验证(Formality)。

1.RTL代码设计

使用硬件描述语言(HDL )将功能以代码的形式描述实现,形成RTL代码。

2.功能仿真验证

检验RTL级的代码设计的正确性。

常用工具:Mentor公司的Modelsim、Synopsys的VCS、Cadence的NC-Verilog等。

3.STA(静态时序分析)

静态时序分析属于验证范畴,指的是在时序上对电路进行验证,检查电路是否存在建立时间(setup time)和保持时间(hold time)的违例(violation)。

常用工具:Synopsys的Prime Time。

4.逻辑综合

将HDL代码翻译成门级网表Netlist。

常用工具:Synopsys的Design Compiler。

5.形式验证(Formality)

为保证在逻辑综合过程中不改变原先HDL描述的电路功能,在功能上对综合后的网表进行的验证,就是形式验证。

常用方法:等价性检查方法。即以功能验证后的HDL设计为参考,对比综合后的网表功能,验证它们是否在功能上存在等价性。

常用工具:Synopsys的Formality。

审核编辑:刘清

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

【「数字IC设计入门」阅读体验】+ 数字IC设计流程2024-09-25 1288

-

数字IC前端后端的区别,数字IC设计流程与设计工具2021-11-06 2477

-

数字IC的设计流程有哪些2021-10-20 2621

-

数字IC前端和后端有何区别2021-07-28 5817

-

数字IC设计流程2020-12-09 8335

-

数字IC设计与数字IC验证哪个好?2020-12-04 2996

-

模拟IC与数字IC到底有什么差别2019-05-12 88871

-

数字IC设计流程及工具介绍2018-03-23 35694

-

模拟IC与数字IC异同2016-12-26 4570

-

杭州招聘:数字和模拟IC设计2016-11-16 2541

-

关于数字IC方向的问题2015-11-08 2988

-

模拟IC与数字IC对比2012-03-29 3854

-

IC数字前端设计实战案例系列pdf2011-12-14 11376

-

模拟IC与数字IC对比分析2009-11-27 1657

全部0条评论

快来发表一下你的评论吧 !