cocotb的安装、python tb文件的写法

电子说

描述

本文介绍了cocotb的安装、python tb文件的写法、用xrun仿真cocotb的脚本等,我们来看看体验如何。

一、准备

-

centos7

-

python3.6+

-

yum install python3-devel

-

pip3 install --upgrade cocotb

二、写RTL

top.svmodule top(input wire clk,input wire rst_n,input wire [7:0] din,output reg [7:0] dout);initial begin$fsdbDumpfile("top.fsdb");top);endclk, negedge rst_n)if(!rst_n)dout <= 'd0;elsedout <= din;endmodule // top

三、写tb

# tb.pyimport cocotbfrom cocotb.triggers import Timer, FallingEdgeasync def gen_clk(dut):for cycle in range(100):dut.clk.value = 0await Timer(10, units="ns")dut.clk.value = 1await Timer(10, units="ns")async def gen_rst(dut):dut.rst_n.value = 0await Timer(22, units="ns")dut.rst_n.value = 1print("Reset Done")async def tb(dut):await cocotb.start(gen_clk(dut))await cocotb.start(gen_rst(dut))test_data_list = range(0,50, 5)for test_data in test_data_list:await FallingEdge(dut.clk)dut.din.value = test_dataawait Timer(100, units="ns")

6~11行:定义了一个时钟,50MHz,100个周期。

13~17行:定义了一个复位信号,低电平有效。复位拉高打印“Reset Done”,方便看log。

19行:用@cocotb.test()装饰器指定了tb的顶层主函数。

22行:异步启动gen_clk

23行:异步启动gen_rst

25~28行:产生了一些测试数据,在时钟下降沿后驱动dut的din。

30行:等待100ns结束仿真

四、写仿真脚本Makefile

SIM ?= xceliumTOPLEVEL_LANG ?= verilogVERILOG_SOURCES += ./top.svTOPLEVEL = topMODULE = tbinclude $(shell cocotb-config --makefiles)/Makefile.sim

设置默认仿真器为cadence xcellium,RTL语言选verilog,指定RTL顶层模块名字(就是dut的名字),testbench的名字为tb,最后include一个cocotb共用的makefile。

五、仿真和看波形

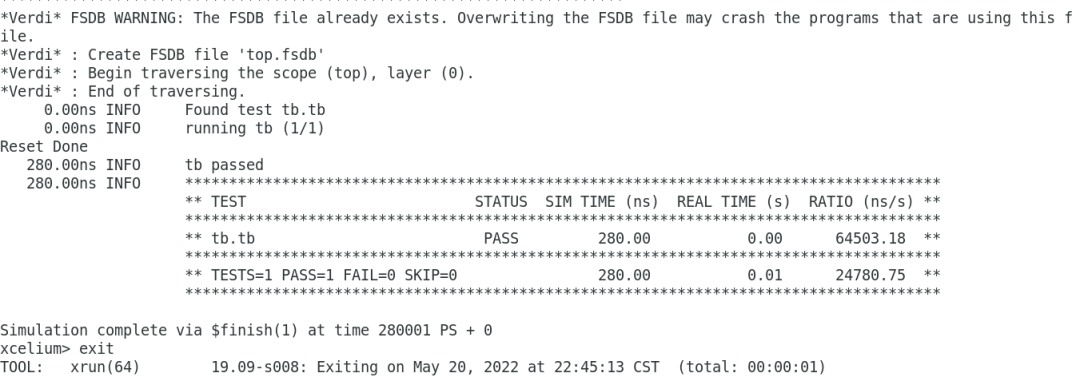

把top.sv、tb.py、Makefile放同一个目录下,敲linux命令:make。不出意外的话,仿真可以正确编译和仿真,如下图:

由于我们在RTL顶层加入了dump fsdb波形的代码,所以在log里可以看到有波形产生。280ns仿真结束,并显示“tb passed”,并打印出汇总信息。可见log还是很友好的。

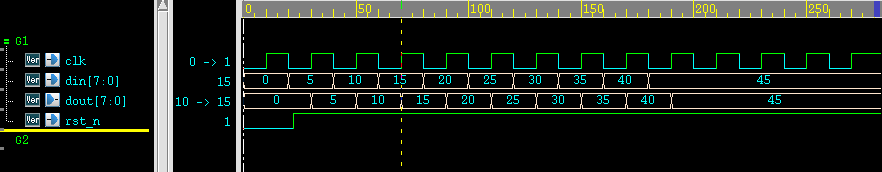

用verdi打开fsdb,与预期一致:

审核编辑 :李倩

-

用python写验证环境cocotb2024-07-24 1894

-

查看python安装路径的方法2023-11-29 14219

-

如何使用Python读取写入Word文件2023-09-27 3195

-

60个python日常高频写法2023-04-16 1677

-

如何安装Python解释器2023-04-14 6349

-

cocotb中的基础语法2022-07-21 3787

-

快速安装 Python 解释器2022-02-15 3144

-

Python 中常见的配置文件写法有哪些2021-10-20 2987

-

基于python的用于构建仿真及测试用例的lib库cocotb2021-10-13 8540

-

在windows下安装python 在linux下安装python 在masOS下安装python2021-06-11 3349

-

python接口文件使用说明2019-05-18 2598

-

Python库的安装与卸载详细步骤2018-10-20 1936

-

windows7下怎样安装whl文件(python)2018-01-23 1857

-

python学习--文件操作2017-12-25 2592

全部0条评论

快来发表一下你的评论吧 !