FPGA入门-查找表结构和乘积项结构

可编程逻辑

描述

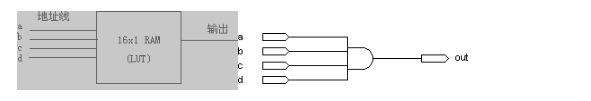

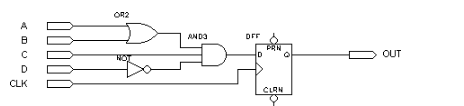

查找表(Look-Up-Table)简称为LUT,LUT本质上就是一个RAM。目前FPGA中多使用4输入的LUT,所以每一个LUT可以看成一个有4位地址线的16x1的RAM。当用户通过原理图或HDL语言描述了一个逻辑电路以后,PLD/FPGA开发软件会自动计算逻辑电路的所有可能的结果,并把结果事先写入RAM,这样,每输入一个信号进行逻辑运算就等于输入一个地址进行查表,找出地址对应的内容,然后输出即可。 下面是一个4输入与门的例子,

实际逻辑电路 LUT的实现方式 a,b,c,d 输入 逻辑输出 地址 RAM中存储的内容 0000 0 0000 0 0001 0 0001 0 .... 0 ... 0 1111 1 1111 1 二.PLDFPGA基于查找表(LUT)的FPGA的结构 我们看一看xilinx Spartan-II的内部结构,如下图:

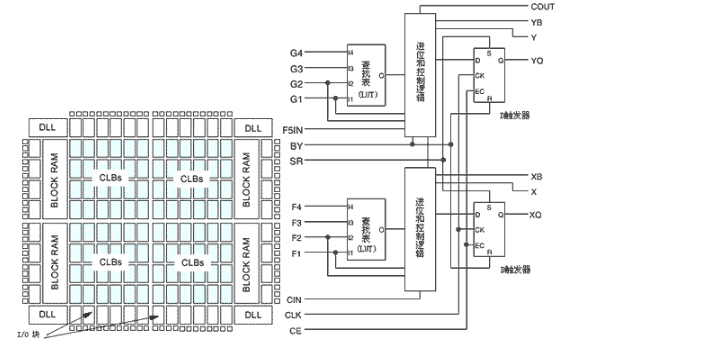

xilinx Spartan-II 芯片内部结构 Slices结构 Spartan-II主要包括CLBs,I/O块,RAM块和可编程连线(未表示出)。在spartan-II中,一个CLB包括2个Slices,每个slices包括两个LUT,两个触发器和相关逻辑。Slices可以看成是SpartanII实现逻辑的最基本结构 (xilinx其他系列,如SpartanXL,Virtex的结构与此稍有不同,具体请参阅数据手册) altera的FLEX/ACEX等芯片的结构如下图:

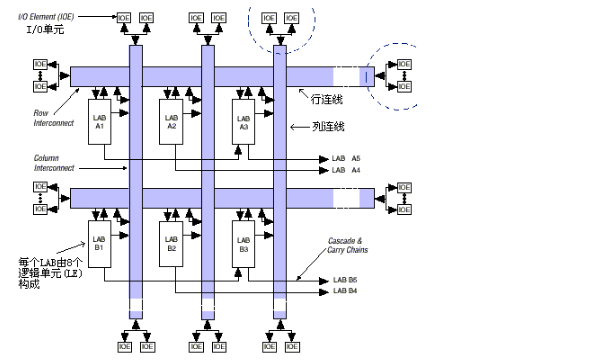

altera FLEX/ACEX 芯片的内部结构

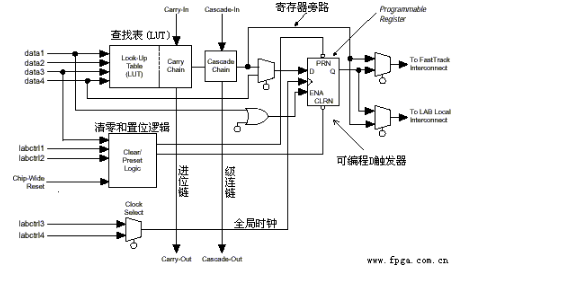

逻辑单元(LE)内部结构 FLEX/ACEX的结构主要包括LAB,I/O块,RAM块(未表示出)和可编程行/列连线。在FLEX/ACEX中,一个LAB包括8个逻辑单元(LE),每个LE包括一个LUT,一个触发器和相关的相关逻辑。LE是FLEX/ACEX芯片实现逻辑的最基本结构(altera其他系列,如APEX的结构与此基本相同,具体请参阅数据手册) 二.PLDFPGA 查找表结构的FPGA逻辑实现原理 我们还是以这个电路的为例:

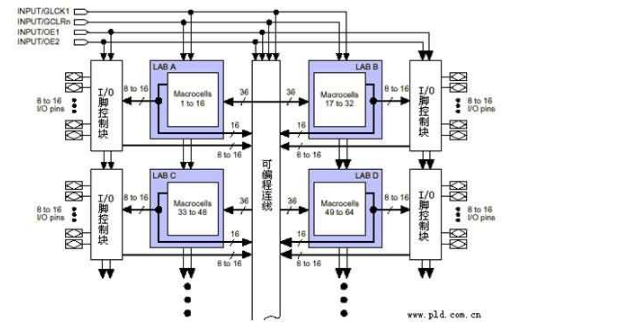

A,B,C,D由FPGA芯片的管脚输入后进入可编程连线,然后作为地址线连到到LUT,LUT中已经事先写入了所有可能的逻辑结果,通过地址查找到相应的数据然后输出,这样组合逻辑就实现了。该电路中D触发器是直接利用LUT后面D触发器来实现。时钟信号CLK由I/O脚输入后进入芯片内部的时钟专用通道,直接连接到触发器的时钟端。触发器的输出与I/O脚相连,把结果输出到芯片管脚。这样PLD就完成了图3所示电路的功能。(以上这些步骤都是由软件自动完成的,不需要人为干预) 这个电路是一个很简单的例子,只需要一个LUT加上一个触发器就可以完成。对于一个LUT无法完成的的电路,就需要通过进位逻辑将多个单元相连,这样FPGA就可以实现复杂的逻辑。 由于LUT主要适合SRAM工艺生产,所以目前大部分FPGA都是基于SRAM工艺的,而SRAM工艺的芯片在掉电后信息就会丢失,一定需要外加一片专用配置芯片,在上电的时候,由这个专用配置芯片把数据加载到FPGA中,然后FPGA就可以正常工作,由于配置时间很短,不会影响系统正常工作。也有少数FPGA采用反熔丝或Flash工艺,对这种FPGA,就不需要外加专用的配置芯片。 三.PLDFPGA 其他类型的FPGA和PLD 随着技术的发展,在2004年以后,一些厂家推出了一些新的PLD和FPGA,这些产品模糊了PLD和FPGA的区别。例如Altera最新的MAXII系列PLD,这是一种基于FPGA(LUT)结构,集成配置芯片的PLD,在本质上它就是一种在内部集成了配置芯片的FPGA,但由于配置时间极短,上电就可以工作,所以对用户来说,感觉不到配置过程,可以传统的PLD一样使用,加上容量和传统PLD类似,所以altera把它归作PLD。还有像Lattice的XP系列FPGA,也是使用了同样的原理,将外部配置芯片集成到内部,在使用方法上和PLD类似,但是因为容量大,性能和传统FPGA相同,也是LUT架构,所以Lattice仍把它归为FPGA。 四.PLDFPGA基于乘积项(Product-Term)结构CPLD CPLD多是基于乘积项(Product-Term)的结构。采用这种结构的CPLD芯片有:Altera的MAX7000,MAX3000系列(EEPROM工艺),Xilinx的XC9500系列(Flash工艺)和Lattice,Cypress的大部分产品(EEPROM工艺) 我们先看一下这种CPLD的总体结构(以MAX7000为例,其他型号的结构与此都非常相似):

图1 基于乘积项的CPLD内部结构 这种CPLD可分为三块结构:宏单元(Marocell),可编程连线(PIA)和I/O控制块。宏单元是CPLD的基本结构,由它来实现基本的逻辑功能。图1中兰色部分是多个宏单元的集合(因为宏单元较多,没有一一画出)。可编程连线负责信号传递,连接所有的宏单元。I/O控制块负责输入输出的电气特性控制,比如可以设定集电极开路输出,摆率控制,三态输出等。图1 左上的INPUT/GCLK1,INPUT/GCLRn,INPUT/OE1,INPUT/OE2 是全局时钟,清零和输出使能信号,这几个信号有专用连线与PLD中每个宏单元相连,信号到每个宏单元的延时相同并且延时最短。 宏单元的具体结构见下图:

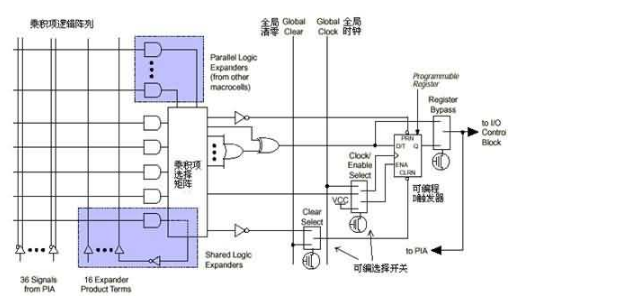

图2 宏单元结构 左侧是乘积项阵列,实际就是一个与或阵列,每一个交叉点都是一个可编程熔丝,如果导通就是实现“与”逻辑。后面的乘积项选择矩阵是一个“或”阵列。两者一起完成组合逻辑。图右侧是一个可编程D触发器,它的时钟,清零输入都可以编程选择,可以使用专用的全局清零和全局时钟,也可以使用内部逻辑(乘积项阵列)产生的时钟和清零。如果不需要触发器,也可以将此触发器旁路,信号直接输给PIA或输出到I/O脚。

审核编辑 :李倩

-

深入理解 FPGA 的基础结构2024-04-03 3185

-

FPGA | 查找表(Look-Up-Table)的原理与结构(Xilinx Spartan-II)2023-11-03 1910

-

FPGA的基本结构、数据存储及配置方式2022-11-29 5898

-

FPGA查找表LUT和编程方式的基础知识说明2020-12-29 1741

-

根据结构特点和工作原理来辨别FPGA与CPLD的区别2020-03-24 6285

-

FPGA 是如何分类的?FPGA的使用方法2018-09-06 5850

-

FPGA主要有哪些知名供应商?FPGA供应商大全2018-09-05 7141

-

FPGA的基本结构2016-07-16 3849

-

FPGA入门:内里本质探索——器件结构2015-01-27 5156

-

FPGA查找表2012-04-28 8790

-

基于查找表的结构模块2009-03-18 1024

全部0条评论

快来发表一下你的评论吧 !