IC设计知识点:一种简单超时机制

电子说

描述

1、超时判断机制

在设计中,为了增加异常处理能力,保证设备的正常运行,常常需要进行超时判断。

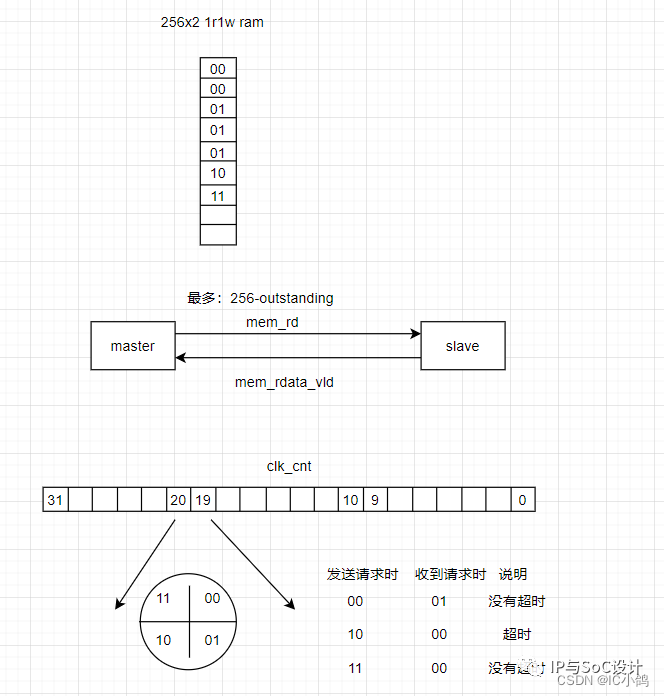

如下图,当master发起mem读请求后,收到读返回数据时,进行超时判断,如果超时,则数据丢弃,如果没有超时,则数据正常接收。

2、一种简单的超时机制

如果在数据发送过程中,发送者向接收者发送数据,通常需要接收者通知发送者自身是否可以接收数据

采用一个公共的32bit clk_cnt作为时间基准,根据不同的超时精度,采用32bit中的连续2bit,1GHz时钟,每个周期1n,例如采用clk_cnt[20:19],可以记录2^21ns级别的精度,即2ms级别的时间精度。

本文中master能够发起256个outstanding请求,req_id[7:0]从0到255,且工作时钟clk为1Ghz,发起的mem读请求,且在1us后都没有收到数据,则认为超时。

步骤1:master发起mem_rd请求时,以req_id作为地址,将clk_cnt[20:19]作为data,写入256x2 1r1w_ram中。

步骤2:当master收到读返回数据时,以req_id作为地址从ram中读取data,记作clk_cnt_record

步骤3:提取当前时刻clk_cnt[20:19],记录为clk_cnt_now,如果clk_cnt_now-clk_cnt_record 的绝对值大于1,则表示超时。

案例:

clk_cnt_record 为 10,clk_cnt_now为00,则表示超时。

clk_cnt_record 为 10,clk_cnt_now为11,则认为不超时。

3、特点说明

优点:此类设计比较简单,所需的逻辑资源较少,并且可以调节超时时间精度。

缺点:

1.如果超时时间过长,已经从clk_cnt_record翻转了一圈再返回时,则无法判断是否为超时。即clk_cnt_record(10)-->11-->00-->01-->10-->11(clk_cnt_now),实际已超时,但是判断为没有超时。

2.没有读返回数据时,无法判断是否超时。

verilog语法:几种可综合的for循环语句

1、采用int实现不同信号赋值的循环

在同一个.v文件中,在不同的场景中,我们想例化不同的ram,如果不使用宏定义,那么该怎么实现呢?

直接采用for(int*)类型格式,可以在一个else分支中使用,不需要使用generate,使用更加灵活,使用范围更广。

input [1024-1:0] func_mode_in;reg [512-1:0] func_id_vld;always@(posedge clk)if(~rst_n) beginfunc_id_vld <= 512'b0 ;end else beginfor(int i=0; i<512;i=i+1) begin : func_id_vld_genfunc_id_vld[i] <= (func_mode_in[2*i+:2]==2'b01) ;endend

2、采用int实现同一个信号赋值的循环

下图所示,采用for(int*)类型格式实现了一个16mux1的循环赋值语句,实现不同条件一下,对debug_test_16mux1的赋值操作,即16mux1的逻辑。

input [128*16-1:0] debug_test_in;input [4-1:0] cfg_16mux1_mode;reg [128-1:0] debug_test_16mux1;begindebug_test_16mux1 = 128'd0;i=0; i<16;i=i+1) begin : debug_test_16mux1_gen==i) begindebug_test_16mux1 = debug_test_in[128*i+:128] ;break ;endendend

如上for循环语句实现了如下的case语句效果

begincase(cfg_16mux1_mode)0 : debug_test_16mux1 = debug_test_in[127 :0 ];1 : debug_test_16mux1 = debug_test_in[255 :128 ];2 : debug_test_16mux1 = debug_test_in[383 :256 ];3 : debug_test_16mux1 = debug_test_in[511 :384 ];4 : debug_test_16mux1 = debug_test_in[639 :512 ];5 : debug_test_16mux1 = debug_test_in[767 :640 ];6 : debug_test_16mux1 = debug_test_in[895 :768 ];7 : debug_test_16mux1 = debug_test_in[1023 :896 ];8 : debug_test_16mux1 = debug_test_in[1151 :1024 ];9 : debug_test_16mux1 = debug_test_in[1279 :1152 ];10: debug_test_16mux1 = debug_test_in[1407 :1280 ];11: debug_test_16mux1 = debug_test_in[1535 :1408 ];12: debug_test_16mux1 = debug_test_in[1663 :1536 ];13: debug_test_16mux1 = debug_test_in[1791 :1664 ];14: debug_test_16mux1 = debug_test_in[1919 :1792 ];15: debug_test_16mux1 = debug_test_in ;endcaseend

NOTE:在for(int*)语句中,debug_test_16mux1 = debug_test_in[128*i+127:128*i] ; 会报语法错误,语法错误,只识别debug_test_in[128*i+:128]而无法识别debug_test_in[128*i+127:128*i] ,否则VCS会报语法错误。

审核编辑 :李倩

-

espconn_gethostbyname接口DNS解析超时机制要自己做吗?2024-07-12 1403

-

IC设计:一种简单超时机制2023-10-19 1058

-

STM32 RTOS知识点2023-08-01 782

-

数字电路知识点总结2023-05-30 7147

-

详解射频微波基础知识点2023-01-29 3546

-

鸿蒙的数据库知识点学习2021-09-06 4273

-

嵌入式知识点总结2021-07-30 1974

-

电机与电气控制基础的知识点2021-01-22 1606

-

Linux串口通信的超时机制2019-07-05 3893

-

基于公平心跳超时容错机制2018-01-02 733

-

PWM知识点详解2017-03-16 1921

-

关于红外通信的一些问题知识点2016-05-05 1074

-

高一数学知识点总结2016-02-23 1528

-

计算机组成原理考研知识点归纳2010-04-13 2034

全部0条评论

快来发表一下你的评论吧 !