J-Link中的JTAG接口使用注意事项

接口/总线/驱动

描述

Q A &

问:J-Link 接口 -JTAG 接口说明

在进行嵌入式系统开发时,我们经常会用到J-Link仿真器。J-Link可支持多个目标接口,比如:

JTAG

SWD/SWO/SWV

cJTAG

FINE

SPD

ICSP

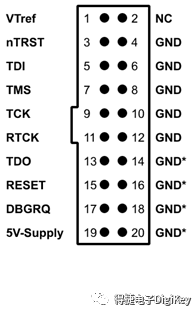

其中,最常见的接口就要算是JTAG了。J-Link有一个JTAG连接器,这是一个20针的连接系统,如下所示。

在较新版本的J-Link产品(如J-Link ULTRA+)上,都保留了这些引脚,用于固件扩展。在正常的调试环境中,它们可以保持打开或连接到GND。一般来说,它们不是JTAG/SWD所必需的。

具体来讲,JTAG连接器是一个20路IDC插头(2.54mm 公插头),与安装在带状电缆上的IDC插座匹配。为了能够进行正确的连接,在应用之前有必要仔细检查JTAG引脚。

下表显示了J-Link的JTAG接口各个引脚的功能定义:

| 1 | VTref | 输入 | 目标参考电压 | 用于检查目标是否通电,为输入比较器创建逻辑电平参考,并控制目标的输出逻辑电平。它通常由目标板的Vdd供电,不得有串联电阻器。 |

| 2 | 无连接 | NC | 不链接到J-Link | 为了与其他设备兼容而保留的。连接到Vdd或在目标系统中保持打开状态。 |

| 3 | nTRST | 输出 | JTAG 复位 | 从J-Link输出到目标JTAG端口的复位信号。通常连接到目标CPU的nTRST。该引脚通常在目标上拉到高电位,以避免在没有连接时意外复位。 |

| 5 | TDI | 输出 | JTAG 目标CPU数据输入 | 建议将该引脚拉至目标板上的定义状态。通常连接到目标CPU的TDI。 |

| 7 | TMS | 输出 | JTAG 模式设置,目标CPU输入 | 这个引脚应该上拉到目标板子上有定义的状态。通常连接到目标CPU的TMS。 |

| 9 | TCK | 输出 | JTAG 时钟信号到目标CPU | 建议将该引脚上拉至目标板子上有定义的状态。通常连接到目标CPU的TCK。 |

| 11 | RTCK | 输入 | 从目标返回测试时钟信号 | 一些目标板子必须将JTAG输入与内部时钟同步。为了帮助满足这一要求,可以使用返回的、重定时的TCK来动态控制TCK速率。J-Link支持自适应时钟,即在进行进一步更改之前,等待TCK更改得到正确响应。连接到RTCK(如果可用),否则连接到GND。 |

| 13 | TDO | 输入 | 来自于目标CPU的JTAG数据输出 | 通常连接到目标CPU的TDO。. |

| 15 | nRESET | I/O | 目标CPU复位 | 通常连接到目标CPU的复位引脚,通常称为“nRST”、“nRESET”或“RESET”。该信号为低电平有效。 |

| 17 | DBGRQ | NC | 不链接到J-Link | 它保留用于与其他设备兼容,用作目标系统的调试请求信号。如果可用,通常连接到DBGRQ,否则保持打开状态。 |

| 19 | 5V-Supply | 输出 | Supply Voltage | 该引脚可用于为目标硬件供电。 |

| 引脚 | 信号 | 类型 | 定义描述 | 功能 |

以下是一些需要注意的事项:

所有标记为NC的针脚均未连接在J-Link内部。这里可以应用任何信号;J-Link将忽略这种信号。引脚4、6、8、10、12、14、16、18、20是连接到J-Link中GND的GND引脚。它们还应连接到目标系统中的GND。

引脚2未连接在J-Link内部。许多目标的针脚1和针脚2已连接。一些目标使用引脚2而不是引脚1来提供VCC。除非引脚1和引脚2连接在目标的JTAG连接器上,否则这些目标将无法与J-Link一起工作。

引脚3(TRST)应连接到目标CPU TRST引脚(有时称为NTRST)。如果未连接此引脚,J-Link也可以工作,但调试时可能会遇到一些限制。TRST应与CPU复位(引脚15)分离

引脚11(RTCK)应连接到RTCK(如果可用),否则连接到GND。

连接器的引脚19(5V目标电源)可用于向目标硬件供电。电源电压为5V,最大电流为300mA。监测输出电流,防止过载和短路。

-

J-Link无法连接芯片的常见解决办法2021-02-19 6986

-

J-Link的高级使用2021-08-06 2130

-

MCUXpresso IDE下使用J-Link下载算法在Flash调试注意事项2021-11-04 1342

-

J-LINK与JTAG的相关资料推荐2022-01-27 793

-

解析J-Link、J-Trace、Open JTAG原理以及其区别2018-01-30 20618

-

J-Link和J-Trace用户指南免费下载2021-03-03 1714

-

J-Link script的组成2021-03-09 3048

-

教你轻松J-Link不能连接目标MCU的问题2021-06-30 7533

-

痞子衡嵌入式:MCUXpresso IDE下使用J-Link下载算法在Flash调试注意事项(i.MXRT500为例)...2021-10-29 871

-

基于J-Link Remote Server软件的远程调试方法2022-06-14 3795

-

J-Link script的组成与使用方法2022-08-01 3837

-

J-Link中的JTAG接口的正确使用注意事项2022-09-23 5007

-

SEGGER J-Link调试仿真器支持新型可编程SOC(片上系统)系列2023-04-14 3178

-

J-Link 中的JTAG 接口:正确使用需要了解的注意事项,在这里!2023-12-01 3639

-

如何通过J-Link向目标系统供电2024-12-21 2393

全部0条评论

快来发表一下你的评论吧 !