CPU流水线的问题

描述

为什么有些CPU的主频更低,但运算效率却更高呢?

比如:51单片机30M主频,STM32单片机20M主频,执行相同一段代码可能主频更低的STM32所花的时间更短。

这里就牵涉到CPU流水线的问题,本文围绕CPU流水线描述相关内容。

一、早期CPU流水线

1.流水线来源

流水线的概念来源于工业制造领域,以汽车装配为例来解释流水线的工作方式,假设装配一辆汽车需要四个步骤:

1.冲压:制作车身外壳和底盘等部件;

2.焊接:将冲压成形后的各部件焊接成车身;

3.涂装:将车身等主要部件清洗、化学处理、打磨、喷漆和烘干;

4.总装:将各部件(包括发动机和向外采购的零部件)组装成车;

汽车装配需要冲压、焊接、涂装和总装四个工人,最简单的方法是一辆汽车依次经过上述四个步骤装配完成之后,下一辆汽车才开始进行装配,最早期的工业制造就是采用的这种原始的方式,即同一时刻只有一辆汽车在装配。

不久之后人们发现,某个时段中一辆汽车在进行装配时,其它三个工人都处于闲置状态,显然这是对资源的极大浪费,于是思考出能有效利用资源的新方法,即在第一辆汽车经过冲压进入焊接工序的时候,立刻开始进行第二辆汽车的冲压,而不是等到第一辆汽车经过全部四个工序后才开始,这样在后续生产中就能够保证四个工人一直处于运行状态,不会造成人员的闲置。这样的生产方式就好似流水川流不息,因此被称为流水线。

2.CPU流水线

1989 年推出的 i486 处理器引入了五级流水线。这时,在 CPU 中不再仅运行一条指令,每一级流水线在同一时刻都运行着不同的指令。这个设计使得 i486 比同频率的 386 处理器性能提升了不止一倍。

五级流水线中的取指阶段将指令从指令缓存中取出(i486 中的指令缓存为 8KB);

第二级为译码阶段,将取出的指令翻译为具体的功能操作;

第三级为转址阶段,用来将内存地址和偏移进行转换;

第四级为执行阶段,指令在该阶段真正执行运算;

第五级为退出阶段,运算的结果被写回寄存器或者内存。

由于处理器同时运行了多条指令,大大提升了程序运行的性能。

二、CPU流水线技术

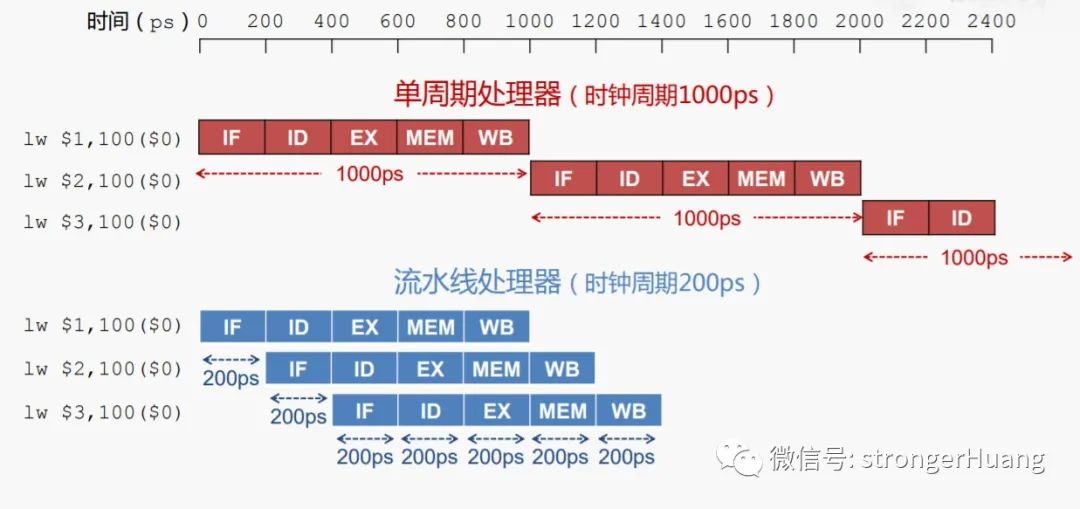

CPU流水线技术是一种将指令分解为多步,并让不同指令的各步操作重叠,从而实现几条指令并行处理,以加速程序运行过程的技术。

指令的每步有各自独立的电路来处理,每完成一步,就进到下一步,而前一步则处理后续指令。

采用流水线技术后,并没有加速单条指令的执行,每条指令的操作步骤一个也不能少,只是多条指令的不同操作步骤同时执行,因而从总体上看加快了指令流速度,缩短了程序执行时间。

流水线技术是通过增加计算机硬件来实现的。它要求各功能段能互相独立地工作,这就要增加硬件,相应地也加大了控制的复杂性。如果没有互相独立的操作部件,很可能会发生各种冲突。例如要能预取指令,就需增加指令的硬件电路,并把取来的指令存放到指令队列缓冲器中,使微处理器能同时进行取指令和分析、执行指令的操作。

---来自百度百科

三、流水线与代码执行效果

为什么说同主频的51单片机相比STM32执行效率低呢?

除了大家认为的8位和32位宽度区别之外,还有一个就是51单片机不支持流水线(也可以理解为单流水线),而STM32支持流水线。

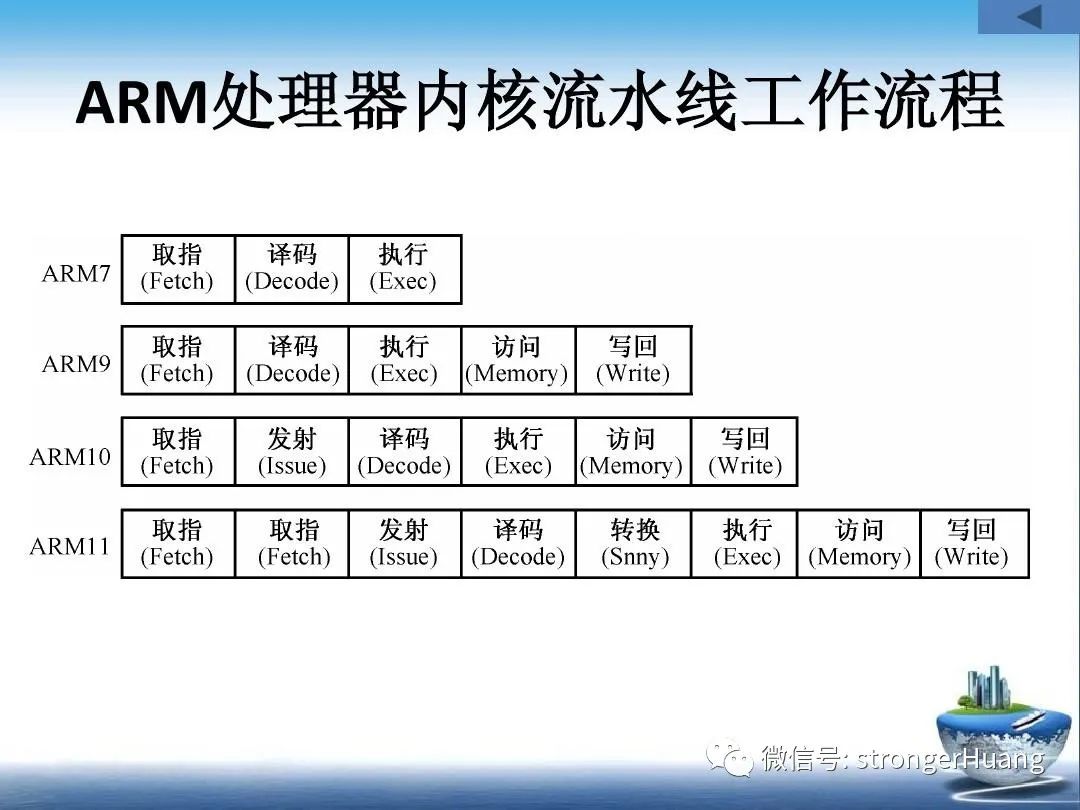

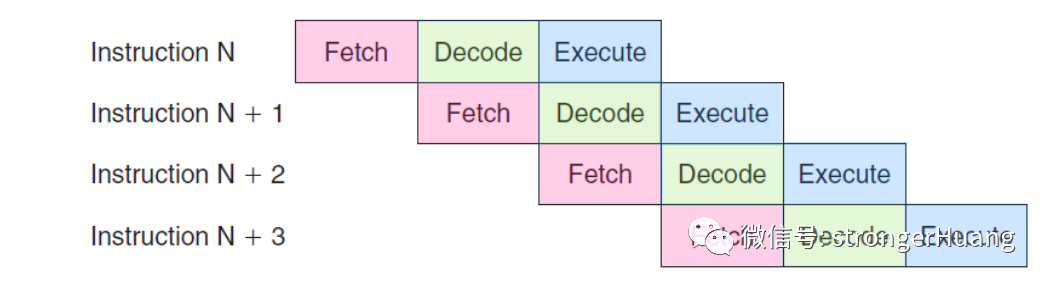

Cortex‐M3处理器使用一个 3 级流水线。流水线的 3 级分别是:取指、解码和执行, 如图:

通过下面一张图来对比单流水线和多级流水线,你就更能明白为什么51单片机执行效率低了。

四、多级流水线优缺点

并非在所有情况下流水线技术都起作用。可能有一些缺点。如果一条指令流水线能够在每一个时脉周期接纳一条新的指令,被称为完整流水线(fully pipelined)。因流水线中的指令需要延迟处理而要等待数个时脉周期,被称为非完整流水线。

当一名程序员(或者组合者/编译者)编写组合代码(或者汇编码)时,他们会假定每个指令是循序运行的。而这个假设会使流水线无效。当此现象发生后程序会表现的不正常,而此现象就是危害。不过当前有提供几种技术来解决这些危害像是转发与延迟等。

1.优点

减少了处理器执行指令所需要的时脉周期,在通常情况下增加了指令的输入频率(issue-rate)。

一些集成电路,例如加法器或者乘法器,通过添加更多的环路使其工作得更快,如果以流水线替代,能相对地减少环路。

2.缺点

流水线处理器设计复杂度更高、生产成本更高;

流水线的处理器必须在数据路径中添加额外触发器。

非流水线处理器有固定指令位宽,流水线处理器的性能更难以预测,并且不同的程序之间的变化可能更大。

审核编辑 :李倩

-

【「算力芯片 | 高性能 CPU/GPU/NPU 微架构分析」阅读体验】--了解算力芯片CPU2024-10-20 1873

-

基于FPGA的带Cache的嵌入式CPU该怎么设计?2019-10-12 2938

-

如何设计带Cache的嵌入式CPU?2019-11-05 1298

-

FPGA中的流水线设计2020-10-26 3164

-

科普下CPU流水线的工作原理2021-12-15 2340

-

CPU流水线的定义2011-12-14 5110

-

探秘X86架构CPU流水线2017-01-14 1410

-

处理器功能单元组成与CPU的流水线的详细解析2017-12-23 13553

-

处理器系列之CPU流水线科普2018-01-26 5033

-

CPU主频的定义2020-05-12 3229

-

为什么有些CPU的主频更低,但运算效率却更高?2021-01-21 4947

-

CPU流水线优缺点2022-10-24 5607

-

单周期cpu和多周期cpu的区别 多周期cpu和流水线的区别2023-10-19 16538

-

如何帮助提高CPU分支跳转的正确率2023-12-13 1392

全部0条评论

快来发表一下你的评论吧 !