简单介绍导出导入Orcad网表的整个过程

电子说

描述

作为layout工程师,首先的输入条件就是原理图,也就是常说的(原理图导出网表文件)网表文件,有硬件工程师会直接把网表发给我们,有的直接给我们dsn文件,要求我们自己导出导入网表,下面简单介绍导出导入网表的整个过程:

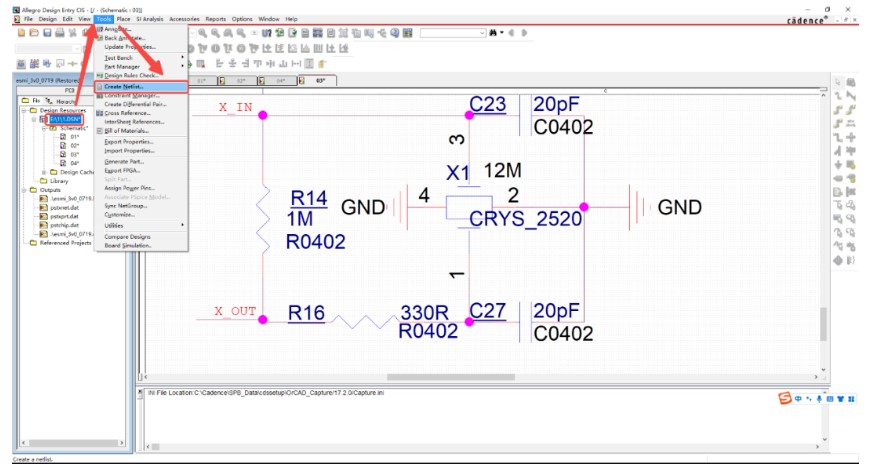

第一步:首先确定原理图设计OK,包括PCB封装、位号等规则检查等,先是点击工程名,然后在OrCAD的菜单栏下选择Tools,点击Create Netlist(产生网表),操作如下图:

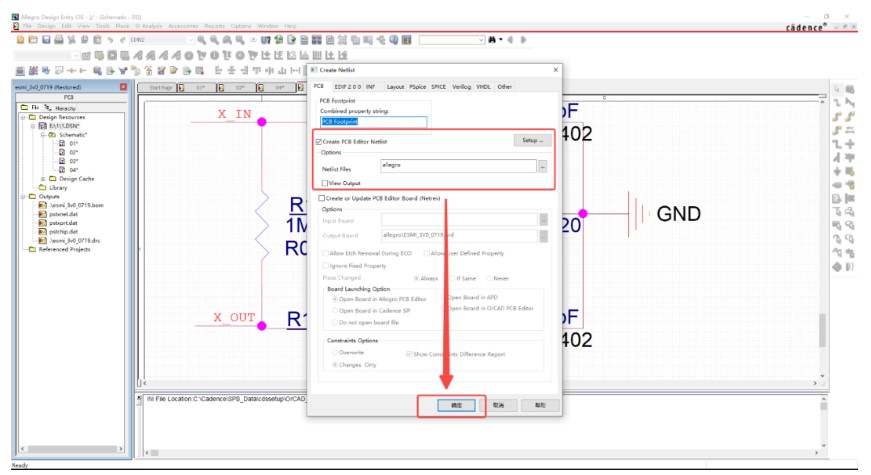

第二步:完成上一步之后,会弹出如下对话框,保持默认即可,其中的Create PCB Editor Netlist 要勾选上,这样产生的网表文件,就会保存在原理图的更目录下的Allegro文件夹里,操作如下图:

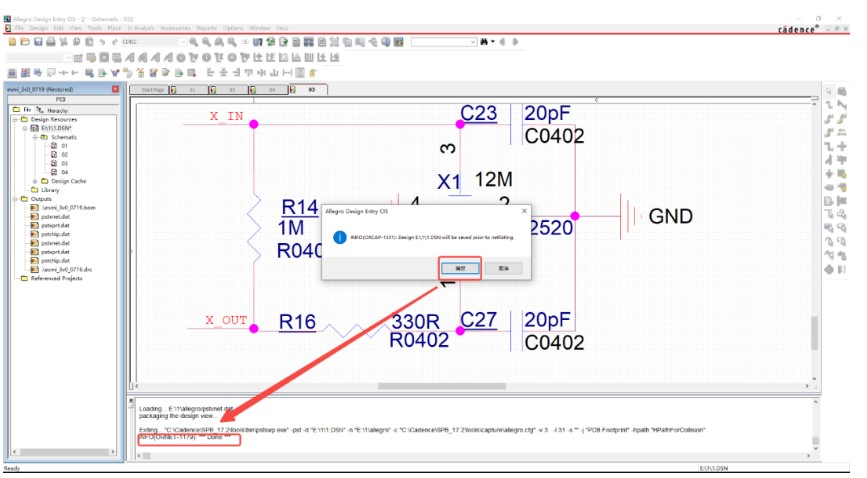

确定之后,会弹出保存网表的文件路径,保持默认点击确定,如果原理图没有问题,会在信息框弹出Done,代表网表导出成功,操作如下图:

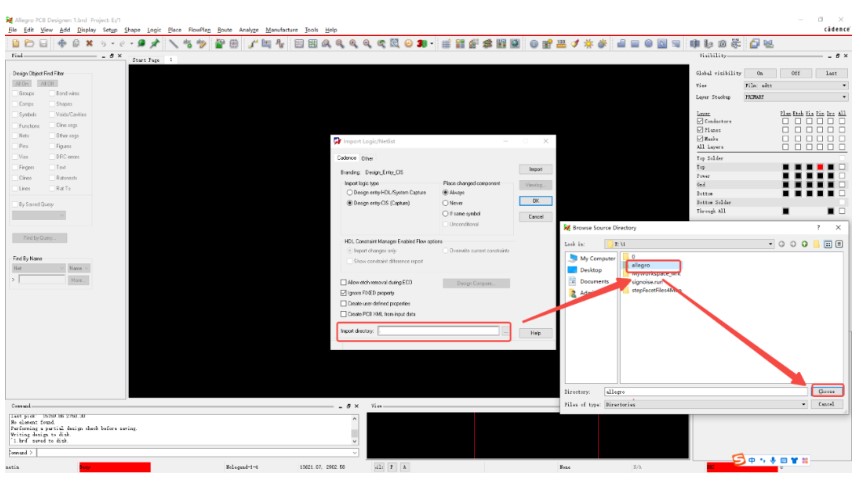

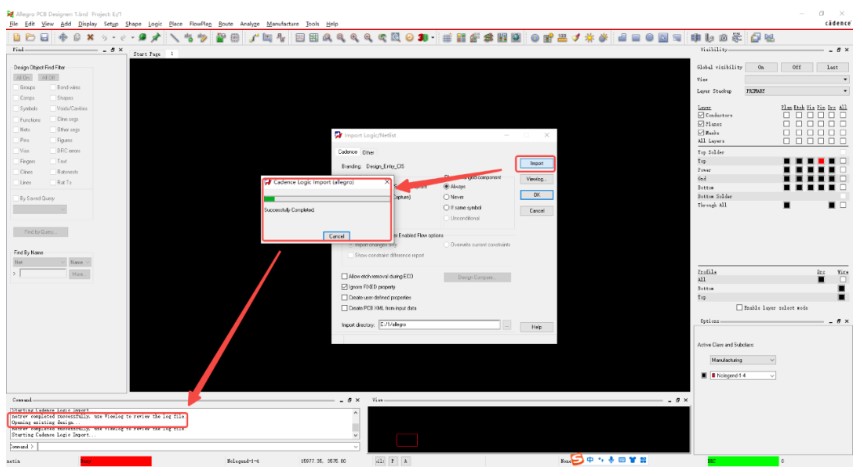

第三步:打开Allegro如件,在Allegro的PCB Editor的菜单下选择File命令,选择Import Logic/Netlist命令,会弹出如下对话框,操作如下图:

完成上一步之后,选择网表目录点击之后,选择我们刚才导网表生成的allegro文件,操作如下图:

目录选择完成之后,几点import,就会显示网表导入情况,完成之后会显示netrev completed successfully,操作如下图:

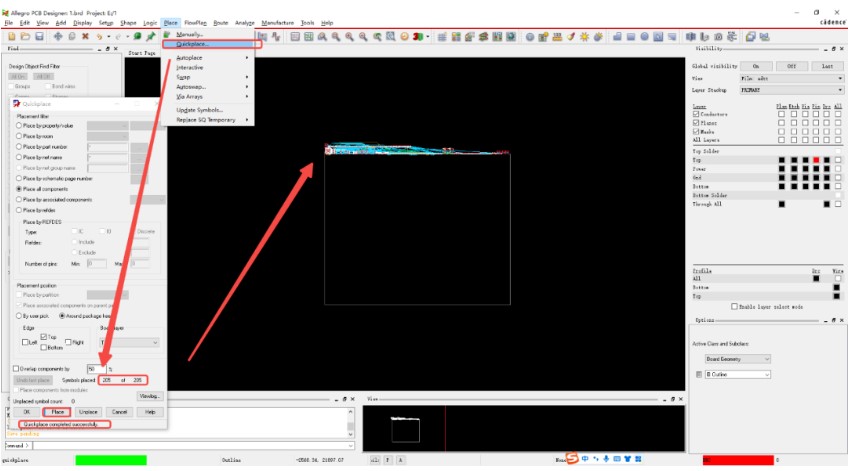

第四步:网表导入成功之后,需要把器件放入到设计界面中,在Allegro的PCB Editor的菜单下选择Place命令,点击Quickplace 快速放入命令,会弹出如下对话框,会显示有多少个器件没有按照,然后点击place命令,器件会自动沿着outline摆放,当所有的器件放入成功之后,会显示Quickplace Place Successfully操作如下图:

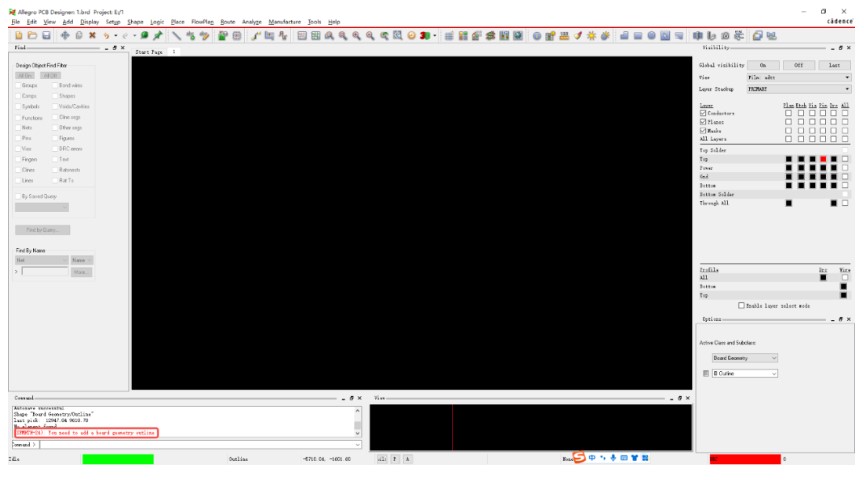

在放入器件之前,我们Allegro设计中必须要有一个Outline,因为器件是沿着Outline摆放,如果没有Outline,点击Place时会报错,显示如下:

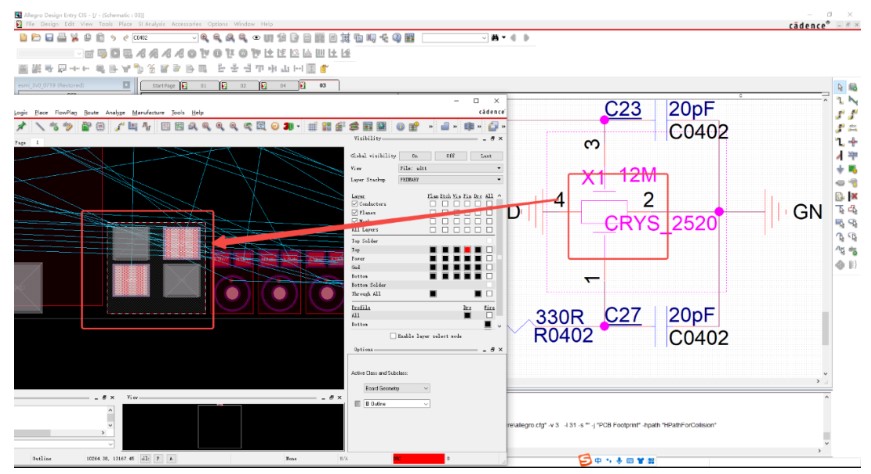

第五步:器件放入成功之后,就该布局设计了。如果以上步骤都是OK的,并且要交互的原理图是Allegro导入网表的原理图,那此时点击原理图中的symbol,在Allegro中的器件就会高亮。此时就可以进行布局交互,用于模块或者电源布局等,显示如下:

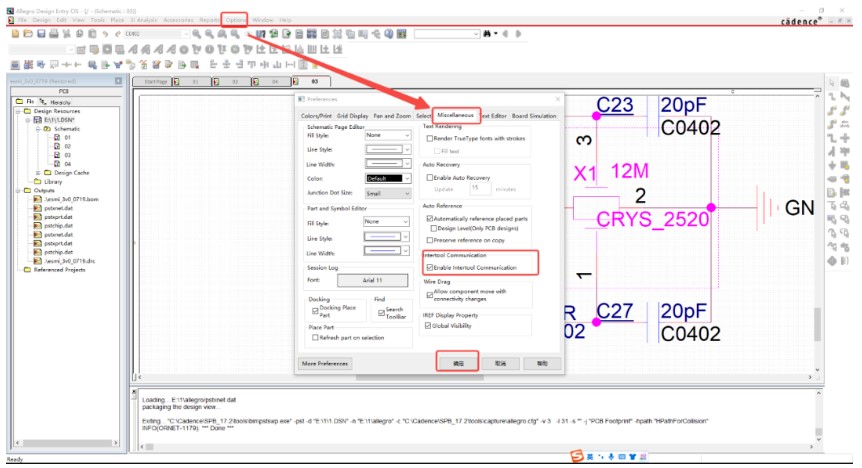

如果以上点击原理图中的symbol,在Allegro中的器件就不会高亮,没有反应,那可以检查一下preference中的miscellaneous里面的设置,其中有一个是使能Allegro和OrCAD的选项,需要勾选,操作如下图:

以上操作流程主要是自己在工作中的使用,大家可能会有不同的方法。

审核编辑:刘清

-

从Orcad到PADS2007网表重新导入问题2011-01-14 7464

-

请问如何在allegro中导入orcad 生成的网表?2011-09-29 8046

-

power pcb2007 导入orcad网表2012-04-18 3074

-

AD网表导入allgero问题2015-09-07 9662

-

Orcad导入Pads过程.pdf2015-09-14 9031

-

AD不同格式设计数据的导入和导出2015-12-28 24122

-

ad网表导入allegro2016-12-19 3669

-

PCB设计软件蓝牙音箱实操│网表导出导入和封装路径设置2018-07-31 3409

-

allegro 16.6 100讲中EXAMPLE2.DSN可以导出网表,Hi3519V101DMEB.DSN为什么不可以导出网表?2019-03-04 2834

-

Orcad软件怎么生成导出allegro网表、ad网表、pads网表2019-08-26 7169

-

如何导出网表2022-02-15 4944

-

PADS PCB如何导入ORCAD绘制的原理图呢?2023-04-28 3317

-

PCB设计:如何导入导出设计规则2018-06-05 10442

-

关于Cadence导出网表2021-12-16 2141

-

如何导入导出SCL源文件?2023-01-16 3543

全部0条评论

快来发表一下你的评论吧 !