ISO 26262:IC Die失效率的三种计算方法

制造/封装

描述

本文依据IEC TR 62380中集成电路的可靠性预测数学模型,对ISO 26262-11:2018中的案例进行推算,方便读者对这一预测模型的了解;本文为IEC TR 62380介绍的上半部分,着重介绍IC Die失效率的三种计算方法,希望为功能安全硬件开发人员提供一定的帮助。

IEC TR 62380《电子组件、PCBs和设备的可靠性预计通用模型》是涵盖电路、半导体分立器件、光电组件、电阻器、电容器、压电组件、显示器、开关等等电子元器件的可靠性预计模型,模型中包含了环境系数以及材料、工艺和结构等因素相关的系数。并将mission profile 温度变化的影响放入模型中予以考虑。

ISO 26262-11:2018在进行失效率分析也推荐使用这一标准,本文将通过ISO 26262中的例子来介绍这一预测模型。

1.IEC TR 62380中可靠性预测的计算

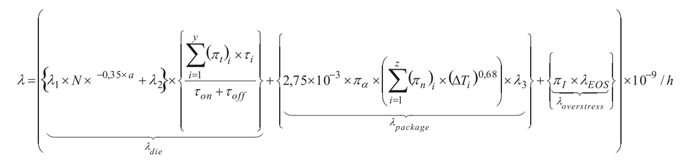

图1 IEC TR 62380的可靠性预测数学模型

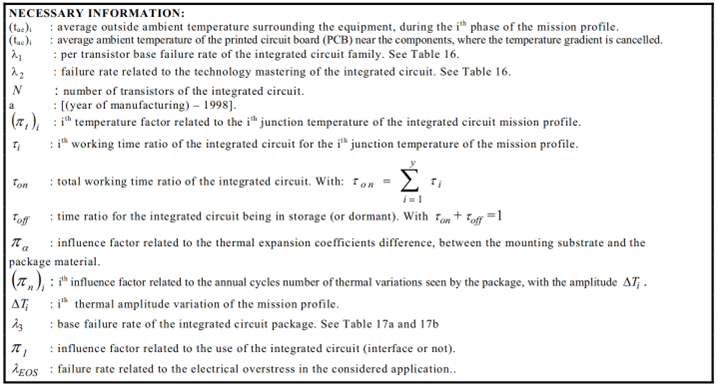

图2 参数介绍

表1 参数介绍

以上为IEC TR 62380里的内容介绍,感兴趣的同学可以去读一下标准第七章:‘Integrated circuits’,标准里有一个例子,可以推算一下,验证一下预测模型。

观察IEC TR 62380的可靠性预测数学模型可以发现:整个数学模型由如下3部分组成:

λdie组件失效率

λpackage封装失效率

λoverstress电过应力失效率

下面将对组件Die失效率计算的三种方法予以介绍。

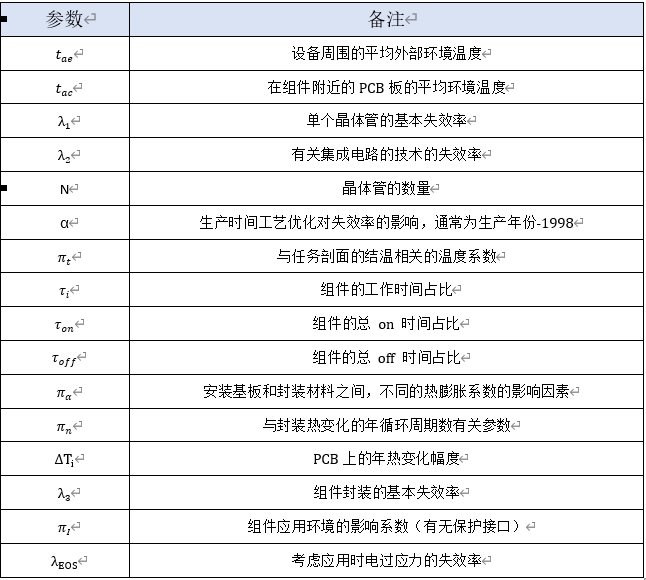

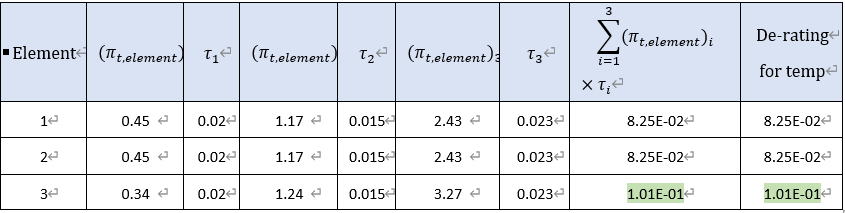

2.ISO 26262中的λdie计算

IEC TR 62380中的计算例子针对的是单一类型电路的计算,对芯片来说是远远不够的,如何考虑包含2种及以上的电路类型的情况呢?

λ1表示的每个晶体管的失效率,只有电路类型有关;而λ2的值不受晶体管数量的影响,是使用的工艺相关的参数,一般在较大规模的芯片芯片产品可靠性计算时,λ2只参与一次计算,每种电路都有专门的λ2,在计算包含多种类型电路的芯片λ2,base时面临如何正确处理λ2的问题;因此在ISO 26262-11中基于IEC TR 62380提出了3个包含多种电路类型的情况的λdie计算方法。

加权平均法

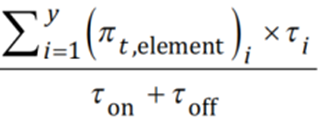

加权平均法:指的是根据每种电路的等效晶体管数量,通过加权平均的方式来计算对应的base失效率,计算模型参考ISO 26262-11:Equation (1):主要分成2部分,公式的左边是不同的电路类型的基础失效,后边为集成电路在任务剖面(Mission profile)下的影响系数(受工作温度及对应的时间占比影响)。

图3 加权平均法的计算模型

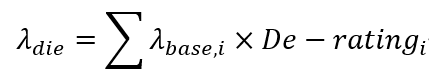

已知一个CMOS的MCU、冷却方式为自然对流、温度剖面为“motor control”、结温温升26.27 C、PQFP 144引脚封装、包含50k CPU和16kB SRAM;参考ISO 26262-11及相关内容描述。

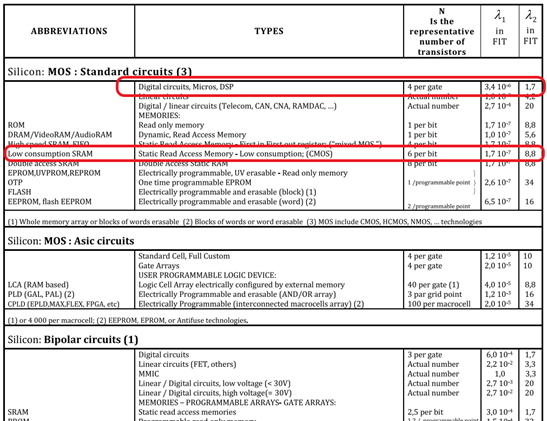

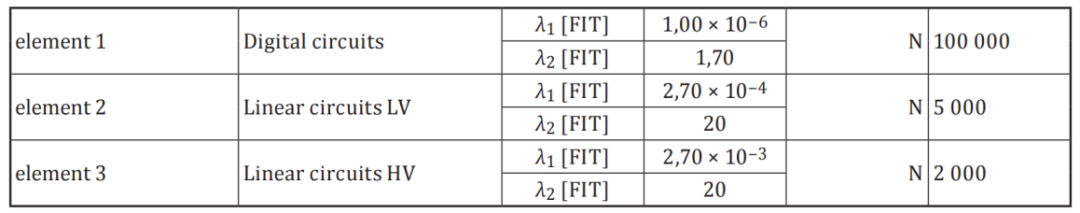

λ1和λ2的选取

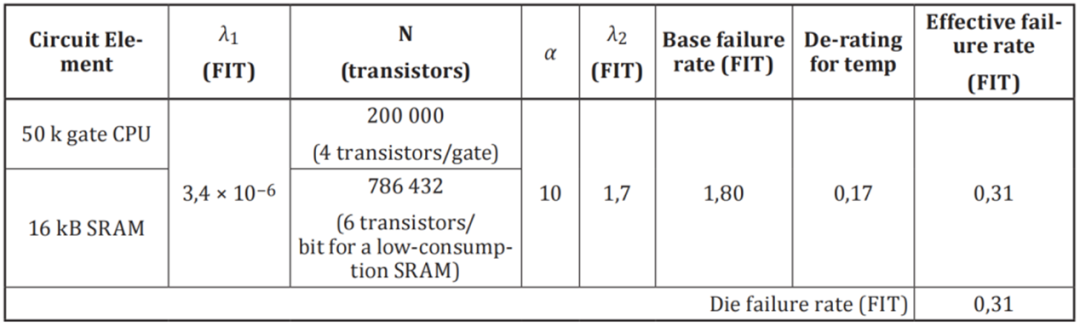

根据输入的CPU、SRAM电路类型,查询ISO 26262-11:Figure 10;即下图,相应的参数选择已标注:

图4 λ1/2的参数选择

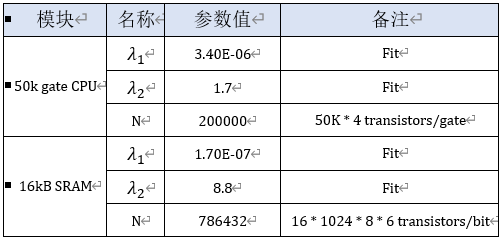

表2 λ1/2的选值和晶体管的数量

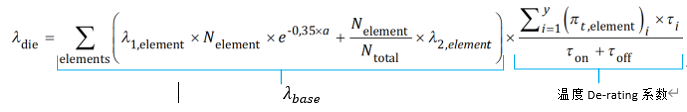

λbase失效率的计算

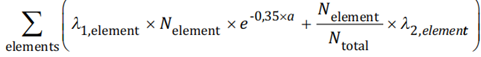

λbase的数学模型如下:

图5 λbase的数学模型

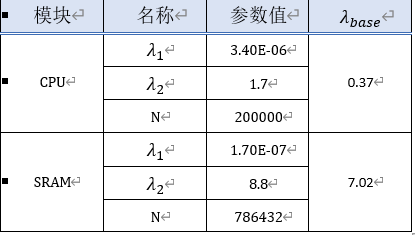

代入CPUSARM的的选值和晶体管的数量,得:

表3

温度De-rating系数的计算

温度De-rating系数用来评估工作环境温度对组件Die失效率的影响大小,在这里由于篇幅问题,就不做详细计算,直接引用Per calendar hour计算结果0.17,计算过程见之后的文章:《Mission profile的使用》。

λdie的计算

将基础失效率和温度De-rating系数代入:

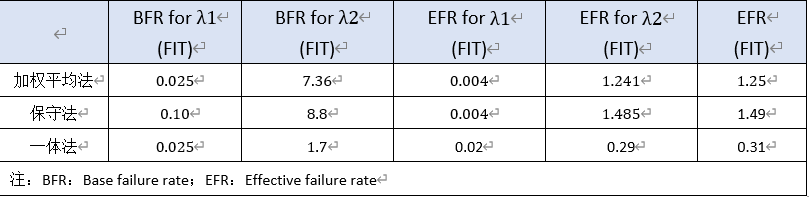

表4

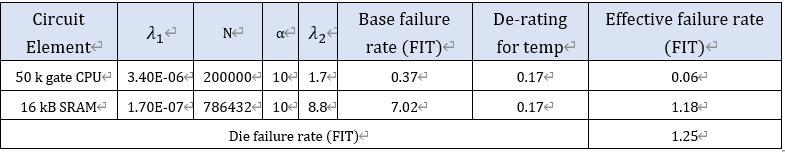

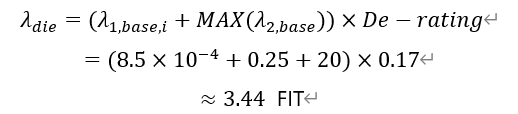

保守法

保守法:指的是选取电路类型中最大的值以及最大温度De-rating系数计算λ2对应的base失效率,计算模型参考ISO 26262-11:Equation (2):

图6 保守法的计算模型

例1

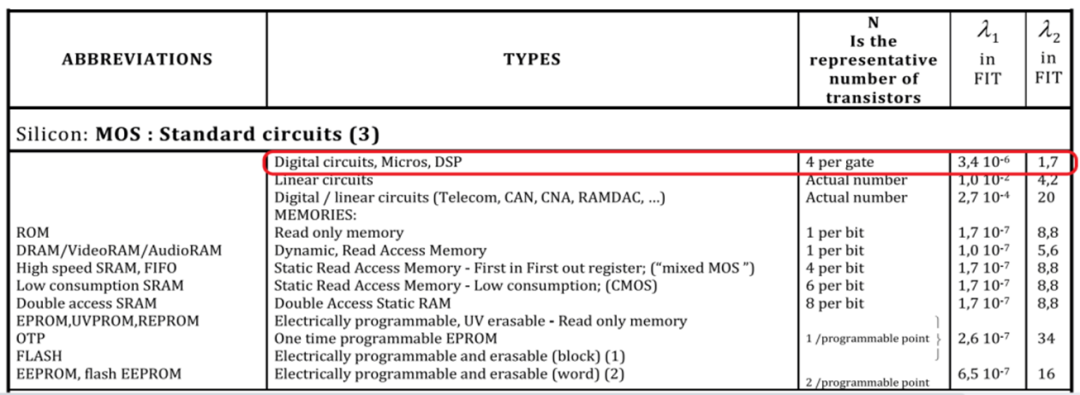

参考ISO 26262-11:Table 3,这个例子没有进行详细的分步计算,表格中已经列出了各个阶段的结果值,供读者理解保守法的计算模型:

图7 ISO 26262 Part11:Table 3

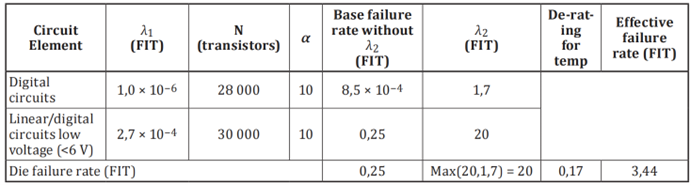

计算过程如下:

经过上面的计算我们知道Base失效率要乘以温度De-rating系数才能得到最终的实际有效结果,在例1中选取了最大的λ2和温度De-rating系数0.17进行计算;但是如果电路的温度De-rating系数不相同呢?ISO 26262-11:Table 4及计算过程给出了答案。

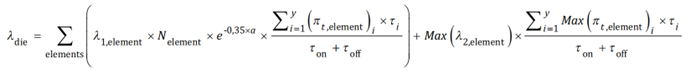

例2

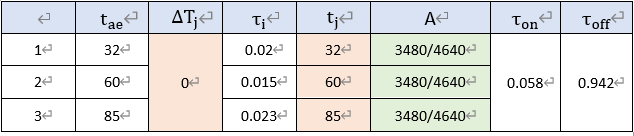

参考ISO 26262-11:Table 4;输入条件如下:

Mission profile仍然是“Motor Control”;

生产年份是2018年,因此 α 的值为20;

Step 1: λ1和λ2的选取

ISO 26262-11:Table 4中直接列出了3种element对应的和,因此不需要查表。

图8 ISO 26262 Part11:Table 4

Step 2:温度De-rating系数的计算

罗列计算温度De-rating系数所需的参数,Mission profile:“Motor Control”

表5

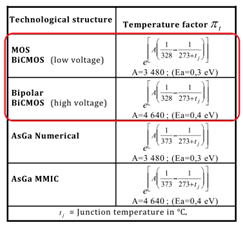

这里需要注意的是:由于element 3是的类型是linear circuits HV,包含2种技术结构,所以这个例子使用的πt计算模型有2个。

图9 πt的计算模型选择

将上表中的参数、计算模型代入温度De-rating系数的计算公式中去,得:

表6

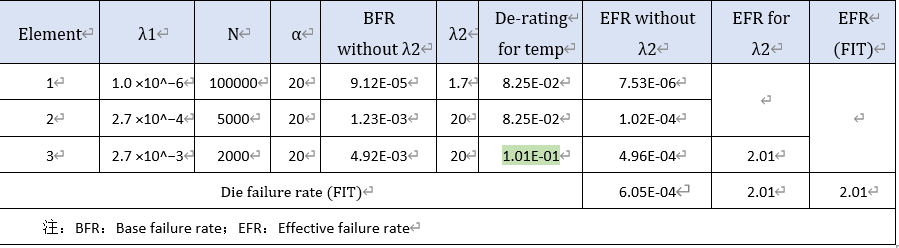

Step 3:失效率的计算

将step 1、2中的参数代入到下面的计算公式中,得:

表7

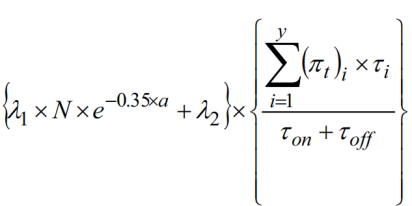

一体法

一体法是将芯片作为一个整体去考虑、不在区分内部电路类型,不用根据电路类型选取参数、也不用考虑不同电路晶体管数量和使用的技术的影响;由于只有一种类型电路,计算模型可以直接参考IEC TR 62380介绍的标准模型。

图10 一体的计算模型

输入参数(参考ISO 26262-11:Table 5)

图11 参考ISO 26262-11:Table 5

输入参数和参数的选择与加权平均法的例子基本保持一致,后续的计算过程也不在进行详细介绍;其中主要区别在于将CPU和SRAM当作整体考虑时电路类型选择的是”Micros”,相应的λ1和λ2的选取如下:

图12

据说Infineon的TC系列MCU所使用就是将MCU作为一个整体来选取参数,希望有专家能提供一下一些参数,可以尝试推算一下其FMEDA里的参数。

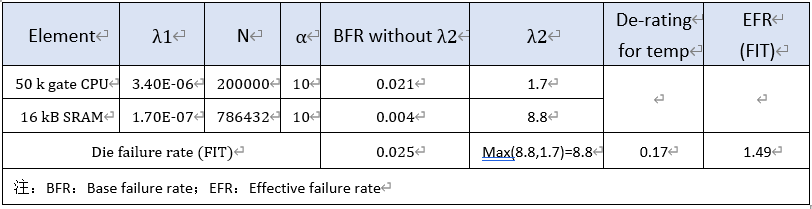

3.三种方法的结果对比

ISO 26262-11: 4.6.2.1.1.1介绍了三种方法来计算包含2种以上电路类型时的集成电路裸片失效,这三种方法计算的结果会有多大差异?

以(50k gate CPU、16kB SRAM)为例来对比,加权平均法和一体法都使用了这一例子,直接代入计算结果,计算过程可以见2.2.1和2.2.3章节;针对保守法计算结果如下:

表8

将3种方法的结果列入表中进行对比:

表9

λdie三种计算方法的总结:

在晶体管数量较小的情况下,λ2的值对最终结果影响较大;

一体法是最乐观的,可以理解为:选择了较小的λ2;但是λ1的值会使λ1的base失效率有所偏大(存储相关的λ1时DSP的1/20,粗略计算一下存储比DSP等效晶体管数量多728万个时,λ1的base失效率的影响将超过λ2)。

加权平均法处于保守法与一体法之间,即考虑了不同电路类型的技术、又兼顾到不同电路所包含的晶体管数量的占比问题;个人推荐。

来源 | sasetech

参考文章:

[1] ISO 26262:2018, Road vehicles — Functional safety —Part 11:Guidelines on application of ISO 26262 to semiconductors

[2] IEC/TR 62380:2004, Reliability data handbook — Universal model for reliability prediction of electronics components, PCBs and equipment

编辑:黄飞

-

李慧敏

2024-11-11

0 回复 举报请问《mission profile的使用》这个文章预备什么时候发 收起回复

李慧敏

2024-11-11

0 回复 举报请问《mission profile的使用》这个文章预备什么时候发 收起回复

-

拥有ISO26262认证的软件工具清单2017-02-07 6405

-

请问LM2596S-ADJ失效率是多少?2019-04-01 3289

-

ISO 26262功能安全标准体系解读2019-07-22 5048

-

STM32定时器时钟的计算方法是什么2021-11-23 1437

-

降低Cache失效率的方法[1]2010-04-13 4537

-

MEMS加速计的三种高压灭菌器失效机理2013-01-24 1886

-

甲类单端的简易计算方法2016-01-19 1084

-

计算汽车功率MOSFET电压开关时间的三种方法2017-09-07 1977

-

一种基于WordNet的混合式语义相似度计算方法2017-11-21 652

-

介绍基于ISO26262安全计算平台解决方案2018-07-11 4962

-

ISO26262的汽车功能安全硬件设计案例资料免费下载2020-09-15 1888

-

ISO 26262中关于失效的概念2020-09-22 8752

-

三种驱动H桥的效率计算方法解析2021-04-09 5551

-

EMC计算方法和EMC仿真(5)2023-02-14 2662

-

EMC计算方法和EMC仿真(1) ——计算方法简介2023-12-05 2876

全部0条评论

快来发表一下你的评论吧 !