MCU时钟相关功能引脚操作

MCU时钟相关功能引脚操作

描述

时钟系统介绍:

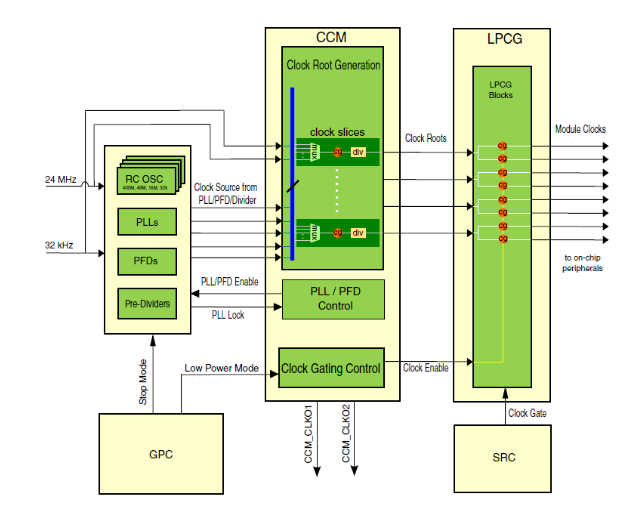

目前 i.MXRT1xxx 系列主要分为 i.MXRT10xx 和 i.MXRT11xx 两大分支。这两个分支的时钟系统设计是有一些差异的,不过总体来说,架构差别不大,我们以如下 i.MXRT1170 的时钟架构为例来具体介绍。

在时钟系统架构图里我们能看到有五大组件:OSC_PLL、CCM、LPCG、GPC、SRC,其中最核心的功能在前两个,OSC_PLL 主要负责产生时钟,CCM 主要用于分配时钟。

时钟源头:

首先,说一下芯片内部的 RC OSC。在芯片设计时,为了保证在没有外部时钟/晶振输入的情况下,芯片也能工作,所以内部集成了一些振荡器/振荡电路(RC Oscillator),32KHz 和 24MHz(48MHz) 是标配,部分型号上还有 16MHz、400MHz,不过这些内部振荡器精度有限(有可能误差20%),适用芯片低速运行场合。

如果是芯片高速运行的场合(或者对精度要求高的场合),那一定需要外接高精度振荡器,包含从 XTALI/XTALO 引脚进来的 24MHz OSC,以及从 RTC_XTALI/RTC_XTALO 引脚进来的 32.768KHz OSC,这两个外部时钟源是由 OSC_PLL 大模块内部的 XTALOSC 小模块负责管理的,XTALOSC 模块优先检测外部是否有 32.768KHz / 24MHz OSC 存在,如果存在则用外部源,如果不存在则启用内部 32KHz / 24MHz RC OSC 源。

24MHz OSC(内部或者外部源)是 OSC_PLL 内部 PLL 的主要时钟源,有了基准的 24MHz 时钟,PLL 就能将其倍频得到想要的高频时钟,芯片内部 PLL 有很多个,大部分 PLL 都只是输出固定原始频率时钟,少部分含 PFD 功能的 PLL(一般是 System PLL)可以调节原始频率输出。除了 24MHz OSC 外,PLL 也可以接受来自 CLK1_P/CLK1_N 引脚输入的源。

时钟输出:

32KHz / 24MHz OSC 是比较重要的时钟源头,它的精度对系统性能有很大影响,因此我们需要有一种方法实测这两个时钟的精度,芯片设计时特意在一些 I/O 引脚复用功能里做了 REF_CLK_24M / REF_CLK_32K 选项,当 I/O 配置为该功能时,便可用示波器量得具体时钟频率。

我们知道 CCM 模块负责 OSC_PLL 输出的时钟资源的分配,芯片里所有外设的具体时钟源指定以及分频系数、开关控制均由 CCM 来完成。如果你想观测某 PLL 最终输出或者常用外设时钟源最终配置,也可以通过指定 I/O 输出观测,即下面的 CCM_CLKO1 / CCM_CLKO2 复用功能选项。当然 CCM_CLKOx 不仅仅用于观测频率,也可以用于给外部芯片提供时钟源。

审核编辑:汤梓红

-

TI的ADS129x器件SPI 时钟极性CPOL和时钟相位 CPHA的正确设置模式2025-06-18 1358

-

ADS1298的时钟相位和极性是什么?2025-02-08 424

-

SPI时钟极性和时钟相位2023-07-21 8235

-

i.MX RT10xx系列外部晶振相关引脚的作用2022-10-13 2432

-

介绍i.MXRT1xxx系列MCU时钟相关功能引脚作用2022-07-07 1234

-

32单片机时钟相关知识2021-12-06 1318

-

RTC实时时钟相关知识点汇总,不看肯定后悔2021-11-23 2350

-

时钟相噪对ADC性能的影响是什么?2021-04-07 1603

-

STM32F030_RTC实时时钟相关的知识资料下载2021-04-04 1256

-

FPGA中的时钟相关概念2021-01-15 5884

-

与时钟相关的PCB的设计考虑主要分为两部分2018-11-25 1941

-

一种基于FPGA的时钟相移时间数字转换器_王巍2017-01-07 1089

-

MSP430G2231单片机,求助其时钟相关问题,在线等!!!2013-07-25 2187

全部0条评论

快来发表一下你的评论吧 !