IC设计的特殊信号打拍方式及RR轮询调度

EDA/IC设计

描述

IC设计:特殊信号打拍方式

1、AXI信号如何打拍

通常block的input和output信号存在时序问题时,我们通常采用寄存器打拍的方式,在两个block直接插入reg,从而解决时序问题。

但是很多信号比较特殊不能随意打拍,例如。AXI信号,握手信号等。此类信号有更高的要求。比如AXI总线中的slave_axi_awready表示写地址通道已经准备好,能够接受master写地址了。此类信号具有很高的时序要求,不能随意使用寄存器打拍,否则就会出现在slave端口已经将slave_axi_awready拉低,而在master端口存在延时认为awready为高而导致继续发waddr,从而导致waddr数据丢失。

Axi总线打拍模块通常会采用特殊设计的IP模块,将所有axi总线信号互联到axi打拍ip上,起到一个桥接的作用,能够解决时序问题。

2、mdio信号不允许打拍

还有一类信号是不允许打拍的,例如mdio信号。

Mdio协议是一种简单的低速接口协议,规定了master和slave共同驱动一根信号线,因此存在如下情况:在T0周期由master驱动,在下一个周期,即T1周期由slave驱动。因此mdio信号不允许打拍,设计上只能将相关的逻辑放置在管脚附件,从而减少走线延时。因为mdio是低速接口协议,时钟通常比较低,一般在100MHz以内,因此时序违例的情况也很少见。

调度设计:RR调度原理

1、RR轮询调度?

RR轮询调度指的是在一次轮询响应请求中,每个请求信号都会获得响应。

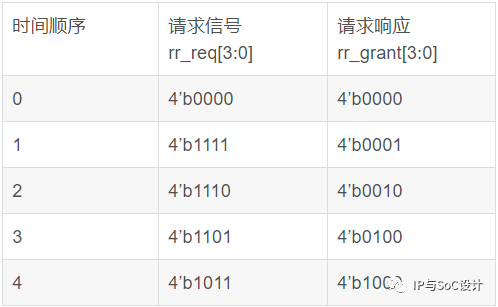

如下所示:输入rr_req[3:0]为4个请求信号,输出rr_grant[3:0]为4请求信号对应的4个响应信号:1表示有请求or响应,信号为0表示无请求or响应。如表所示,第1次,所有请求均有效,首先响应低bit的请求,所以rr_grant[0]=1。第3次请求,请求rr_req[1]有效,但是在第2次中被响应(rr_grant[1]=1),因此此次不再响应,而是响应rr_req[2],所以rr_grant[2]=1.

2、Verilog是如何实现RR轮询调度的?

在verilog实现中,仅仅采用简单的组合逻辑和寄存器就可以实现rr轮询调度,不需要状态机等设计。

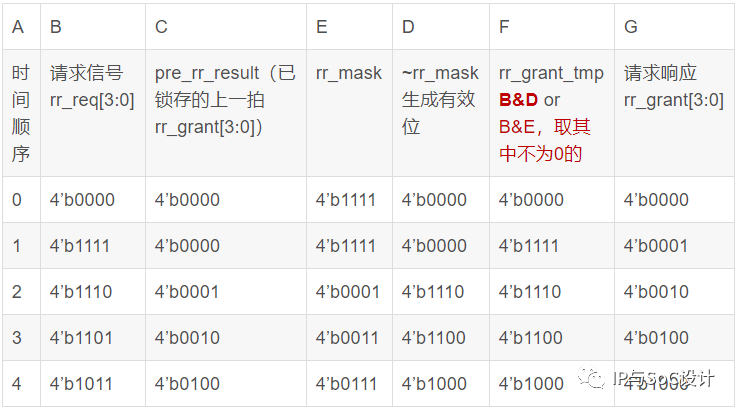

基本原理是锁存上一次输出请求响应rr_grant[3:0],并且生成相应的有效位rr_mask[3:0],从(rr_valid[3:0]&rr_mask[3:0]) 和 rr_valid[3:0]&(~rr_mask[3:0]) 选取不为0的作为获得rr_grant_tmp,rr_grant_tmp再经过组合逻辑并且取最低有效位。此处mask中1表示请求有效。

B列为请求信号rr_req[3:0]

C列pre_rr_result 为模块内部锁存的上一拍rr_grant[3:0]。

D列rr_mask为pre_rr_result经过组合逻辑得到的掩码,rr_mask= {pre_rr_result[2:0],pre_rr_result[3]}-1’b1

E列 ~rr_mask为pre_rr_result经过组合逻辑得到的掩码,rr_mask=~( {pre_rr_result[2:0],pre_rr_result[3]}-1’b1)

F列:rr_grant_tmp为B&D or B&E,取其中不为0的

G列:rr_grant_tmp经过组合逻辑输出最低有效位:(~rr_grant_tmp+1’b1)&rr_grant_tmp

编辑:黄飞

-

IC设计:Verilog是如何实现RR轮询调度的?2023-12-13 3374

-

时序优化之接收端打拍策略探讨2023-12-04 1405

-

RR轮询调度?Verilog是如何实现RR轮询调度的?2023-09-28 5913

-

Proteus教程:按键的三种控制方式(轮询、矩阵、中断)2023-06-14 7003

-

STM32CUBEMX(9)--ADC通过轮询方式读取,USART打印2022-11-14 2519

-

如何利用system verilog的fork join_none实现信号打拍操作呢2022-04-02 10483

-

SDIO轮询方式相关资料分享2022-02-14 670

-

什么是轮询模式?轮询模式有何功能2021-12-22 3561

-

基于PIC16F877A开发板的固定时间片轮询调度汇编程序干了啥2021-08-02 1169

-

Microchip单片机固定时间片轮询调度汇编代码 精选资料推荐2021-07-13 1220

-

基于动态分组的M2M上行优先级调度算法综述2021-06-11 836

-

基于FPGA的轮询合路的设计和实现2010-08-09 543

-

基于SDH芯片的S19202的轮询合路的设计2010-07-31 1187

全部0条评论

快来发表一下你的评论吧 !