EMC知识:时钟信号导致的干扰及解决办法

EMC/EMI设计

描述

回顾一下今年几个项目的EMC反反复复还是花了不少时间。结合自己的经历,把相关的经验分享给大家。欢迎指正和补充。

1.时间就是金钱

整套EMC测试环境搭建可能要花几百万,特别是像暗室这种辐射测试环境,一般的企业都是没有这个条件的。所以一般都会去认证机构或者大型企业进行EMC测试。

测试都是按小时计算收费的,每个地方的收费标准不一样。像我们这边一般都是1000元/小时,老客户的话,可以讲讲价。

计时是按照开始和结束来算的,中间整改时间也包括在内。所以当测试不通过时,一定要及时想出整改对策。建议每次测试最多2-3小时,否则时间长了,思路到后面越来越晕,越来越乱。

如果问题没解决,回去一定要马上记录实验过程,做了哪些整改措施,下一次的整改方案有哪些。因为时间长了有些细节可能真的会忘。

2.工具一定要准备齐全

认证机构不是什么东西都有的,不是把样机直接带去测试就可以了。很多东西需要自己准备。这些东西建议大家最好带上:

镊子,胶带,铜箔,电阻本,电容本,各种X电容、Y电容和共模线圈,还有相关的测试工装。

反正能想到的,都尽量带上,否则可能会因为忘记拿一个小工具付出昂贵的代价。

3.连接线尽量短,且从板子边沿走线。

一般来说,频率较低的干扰,是通过传导来传播,频率较高的干扰,则通过空间无线发射传播出去。

排线相当于天线,机箱内其他电路的辐射电磁能量感应到排线上,产生电压和电流,导致排线产生辐射。

干扰信号的频率越高,连接的排线越长,发射干扰效率越高,对外干扰越大。当连接线长度是干扰信号对应波长的1/4或者1/4的奇数倍时,干扰发射效率最高。(λ=v/f)

像wifi天线,4G天线一般都在板子的边沿,因为天线会像外发射信号,就是这个道理。所以,连接排线一般也都在板子边沿,且尽量短,尽量用扎带固定。

如果排线干扰,选用屏蔽线,效果可能会好一些。或者在线上套磁环,但这样的缺点是不方便生产。

4.时钟信号导致的干扰及解决办法

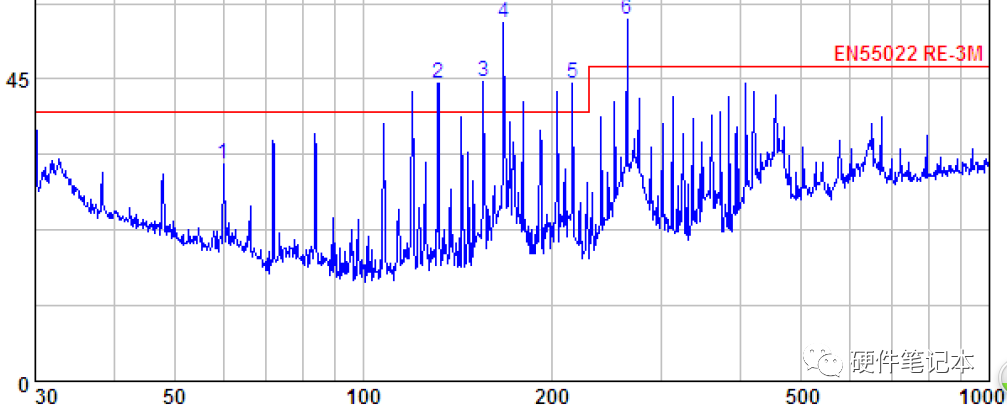

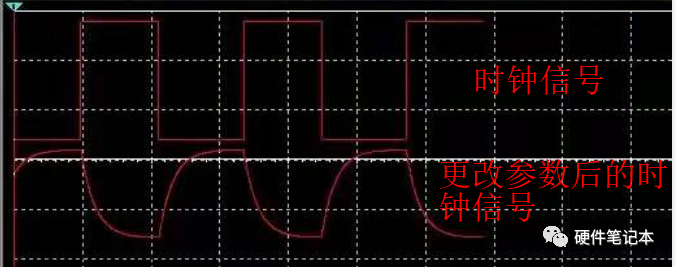

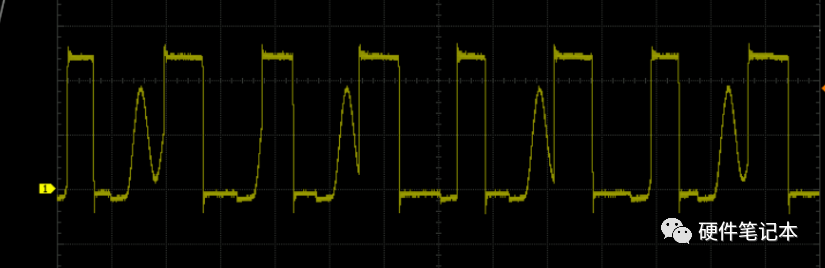

时钟信号为周期信号,一般频率比较高,而且是方波,上升沿时间比较陡,能量比较强,会产生很大的辐射。通常其倍频点辐射超标会更严重。

在今年的项目中,遇到过一次时钟频率超标,但是解决的周期比较长。 ①怀疑过走线敷铜包地的问题,改过一次板; ②怀疑买到假芯片,本身质量问题,换过两次芯片厂家; ③尝试用铜箔屏蔽,效果不理想。

最后,我们在时钟信号上尝试用磁珠+电容或电阻+电容匹配的方式。目的是改变信号质量,让波形变缓,匹配后信号会有很大的改善,辐射也会降很多。但是有一个问题,缓到什么程度呢?首先必须得保证设备正常工作,然后还需要经过多次测试和验证。

之前有朋友推荐过展频晶振,它的原理是通过对尖峰时钟进行调制处理,使其从一个窄带时钟变为一个具有边带的频谱,将尖峰能量分散到展频区域的多个频率段,从而达到降低尖峰能量,抑制EMI的效果。

听起来还不错的样子。由于项目的时间节点和晶振的价格,当时没有用这种方案,如果有用过的朋友可以告知一下。

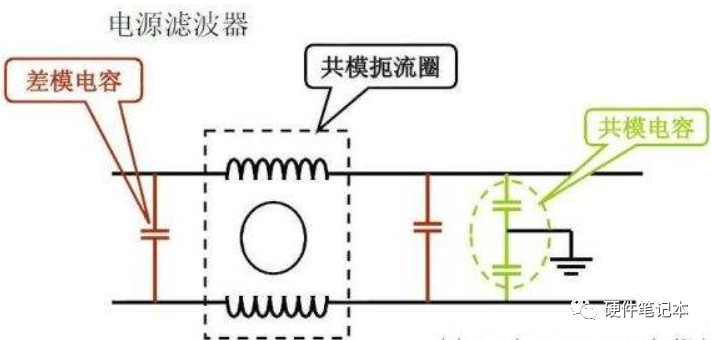

5.差模干扰的产生及解决办法

差模干扰存在于L-N线之间,电流从L进入,流过整流二极管正极,再流经负载,再回到N。在这条通路上,有高速开关的大功率器件,有反向恢复时间极短的二极管,这些器件产生的高频干扰,都会从整条回路流过,从而被接收机检测到,导致传导超标。

差模干扰的整改有以下方法:

1.在火线L和零线N之间套磁环

2. 增大X电容容值

3. 增大共模电感感量,利用其漏感,抑制差模噪声

6.共模干扰的产生及解决办法

共模干扰存在于电源输入线与大地之间的寄生电容,干扰噪声通过该电容流向大地,在LISN-电源线-寄生电容-地之间形成共模干扰电流,从而被接收机检测到,导致传导超标。

共模干扰的整改有以下方法:

1.在地线上套磁环。

2.加大共模电感的感量。

3.主板尽可能接地,减小对地阻抗,从而减小线缆与大地的寄生电容。

7.BUCK电源引起的传导干扰的解决办法

在电路中,我们常用BUCK芯片,将输入的+12V转化为+5V或+3.3V给其他芯片供电。BUCK芯片是一个开关电源,其开关频率会影响传导辐射导致不通过,这是很常见的问题。

除了严格参考芯片手册进行布板,在画PCB时更要注意覆铜和包地,特别要注意保持地回路的良好性。

编辑:黄飞

-

信号带宽为1.485G导致LMH0041恢复不了时钟,怎么解决?2024-12-17 474

-

存储示波器的触发问题及解决办法2025-04-09 1030

-

开关电源问题的解决办法及实例分析2016-01-06 8339

-

开关电源问题分析及解决办法点滴2017-08-10 3384

-

测量系统干扰严重,请教解决办法2018-03-29 4301

-

开关电源问题分析及解决办法详解2018-10-16 1846

-

EMC知识:时钟信号导致的干扰及解决方式2022-10-22 34373

-

双绞线传输器横纹干扰模拟测试实验和解决办法2010-02-26 1717

-

误码特性,误码产生的机理及解决办法2010-03-19 2661

-

开发中常遇电磁兼容EMC问题及解决办法2010-04-17 873

-

卫星干扰起因及改善的解决办法解析2017-12-13 4004

-

路由器光信号闪红灯的解决办法2022-09-27 3438

-

变频器对PLC模拟量干扰及用信号隔离模块克服此类干扰的解决办法2024-06-16 4032

-

常见MCU故障及解决办法2024-11-01 11902

-

常见垫圈故障及解决办法 防漏垫圈的设计与应用2024-12-12 2008

全部0条评论

快来发表一下你的评论吧 !