高速串行数字电路设计工具:眼图医生的功能与应用

电子说

描述

眼图医生(Eye Doctor)是力科于2006年推出的用于高速串行数字电路设计的强大工具,包括了虚拟探测(virtual probing)与接收端均衡(receiver equalization)两部分,主要用于通讯背板设计、高速串行信号一致性测试、高速SERDES芯片均衡器的优化与设计等等。在2009年2月,力科发布了新一代的眼图医生II,提供了更强大的分析能力与良好人机界面,可以大大加快当前流行的高速数字电路的开发速度,缩短测试与验证时间。接下来逐一介绍最新的眼图医生的功能与应用。

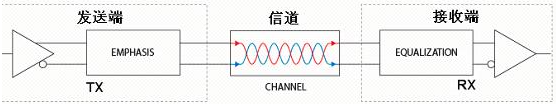

串行数字电路可以分为发送端(TX)、信道(CHANNEL)、接收端(RX)三部分,如下图一所示。眼图医生可以对串行数字链路中三个部分进行分析:

1. 发送端的预加重/去加重分析:针对某一信道计算出最佳的预加重/去加重参数。

2. 信道仿真:直接测试TX输出的波形,输入信道的S参数模型后,准确计算出RX端的波形。

3. 接收端的均衡器设计:对于高于5Gbps的信号,通常在RX端测试时,眼图已闭合,眼图医生可以仿真均衡器,计算出均衡后的信号波形与眼图。

图一:高速串行链路示意图

什么是信道?

在通信理论中通常用“信道”来描述连接TX与RX的物理媒质,在某些SI(信号完整性)文献中,又称为互连。信道包括了我们常见的:印刷电路板(PCB)上的微带线、带状线、过孔、连接器、集成电路的封装、光纤、电缆等等。如下图二所示为背板的示意图。通常,信道有一个共同的特点:随着频率的升高,损耗越来越大;信道的物理传输距离越长,损耗越大。

图二:背板的互连示意图

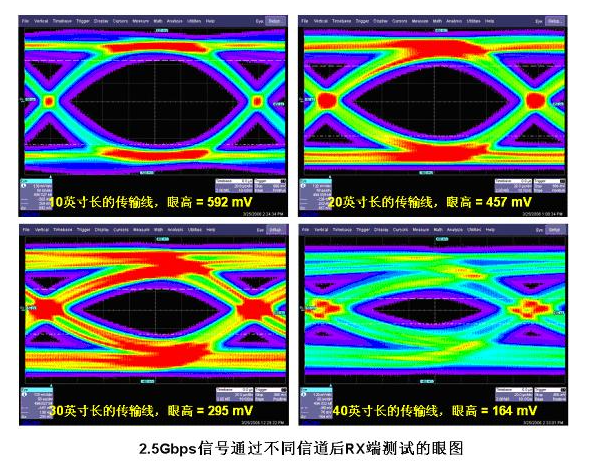

接下来为某背板的测试案例。其TX为某2.5Gbps的高速芯片,信道由两块线卡与背板组成,其PCB上传输线的有10英寸长、20英寸长、30英寸长、40英寸长四组,在接收端测量眼图(如图三所示),使用游标测量眼高(眼图的张开程度),分别为592mV、457mV、295mV、164mV。可见,随着PCB上传输线的长度的增加,信道的损耗越来越大,RX端测量到的眼图的眼高越来越小。

图三:不同背板走线长度的接收端眼图测试结果对比

什么是信道仿真?

信道仿真是用力科示波器测量TX发送的波形,然后在眼图医生中导入信道的S参数模型文件,计算出通过信道后RX端的信号波形、眼图与抖动。力科信道仿真的处理速度非常快、精度足够高。

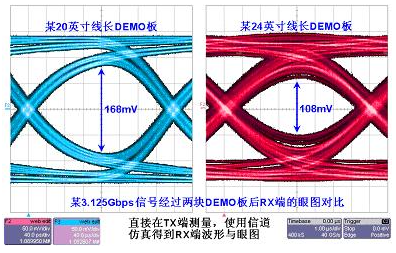

下图中TX为某3.125Gbps信号,通过同轴电缆连接到示波器的两个通道,即示波器直接在TX端测量,然后使用某20GHz带宽的矢量网络分析仪(Vector Network Analyzer,简称VNA)测量两块走线长度不一样的DEMO板的S参数,在力科的眼图医生中调用S参数来仿真该信道。计算出RX端的波形与眼图,眼图如下图四所示,左边是某厂商的20英寸长DEMO板接收端的眼图,右边为另一厂商的24英寸线长DEMO板计算出的RX的眼图。两者的眼高分别为168mV与108mV。

使用信道仿真,无须连接TX、信道、RX后在RX端实测,只要拥有信道的S参数模型,示波器直接在TX端测量,就可以仿真出通过不同信道后RX端的波形、眼图与抖动。这样,就可以快速验证某高速SERDES芯片驱动不同长度传输线时接收端的性能,在高速背板的预研与设计中非常有用。

图四:某3.125Gbps信号的接收端眼图测试结果对比

怎样得到信道的S参数文件?

在信道仿真中,信道的S参数模型的精确性决定了RX端计算结果的精确性,所以获得足够精确的信道的S参数模型非常重要。在信号完整性(简称SI)领域,通常有两种方法获取信道的S参数模型。

1. 使用VNA或者TDR直接测量信道的S参数;

2. 使用HFSS、SIwave、Sigrity等EDA建模软件提取信道的S参数;

前者基于实际信道的测量,精度高,不过信道上的端口必需留有SMA射频头,VNA或TDR通过SMA接头的同轴电缆连接到待测试信道;后者通常基于连接器的三维结构、PCB的压板结构(stackup)、介质特性、传输线的几何特性,使用计算电磁学的一些算法提取出信道的S参数模型。

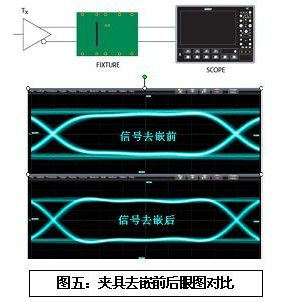

图五:夹具去嵌前后眼图对比

力科的信道仿真可以调入扩展名为*.sNp(N为端口数)的S参数文件,通常*.sNp文件称为touchstone文件,测试仪器和EDA软件都可以输出这个格式的S参数文件。关于S参数的相关理论,可参考一些射频理论书籍。

什么是夹具去嵌?

在测量当前流行的很多串行信号(比如PCIe、SATA、SAS、FBDIMM)时,通常需要专门的测试夹具,夹具上把PCB的传输线转换为SMA射频连接头,待测试信号连接到夹具上,夹具通过同轴电缆连接到示波器,如下图五所示,示波器作为接收端进行测量。由于夹具上的连接器、金手指、过孔、微带线、带状线等会使信号发生衰减、色散或者反射,导致示波器测量到的信号有所恶化。使用夹具去嵌功能,只需输入夹具的S参数模型文件,即可计算出没有夹具时测量到的信号的波形与眼图。如图五所示,上半部分是信号去嵌前测量到的眼图,下半部分是信号去嵌后测量到的眼图,相比前者,后者的上升下降沿更陡峭,眼轮廓清晰,眼张得更开。从这个比较图中可以看到力科的去嵌技术可以消除夹具的负面作用。

信道仿真的常见问题

问题1:力科的信道仿真与EDA软件仿真有什么区别?

和力科的眼图医生一样,EDA软件同样可以做信道仿真、均衡器仿真。两种最主要的区别在于:

1. 力科的信道仿真和均衡器仿真速度非常快,在几秒钟内就可以计算出几百微秒长的波形,几乎可以做到实时测量,实时计算出结果;而EDA软件的计算速度较慢,计算几百纳秒长的波形通常需要几十分钟。两种方法的速度有天壤之别。

2. 力科的信道仿真基于实测,电路板上很多随机因素都考虑进去了,而EDA软件仿真通常基于理想的工作状况,忽略了一些随机因素。

问题2:信道仿真的精度?

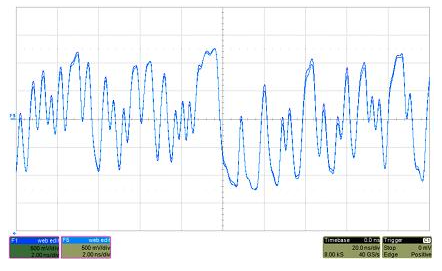

信道仿真的精度取决于信道的S参数模型是否足够精确。在下图为某IC厂商验证其SAS2芯片驱动背板的测试结果。其中一个波形是用力科示波器在TX端测试,用信道仿真计算出的RX端的波形,另一个波形是示波器直接在RX端测量到的波形,可见两者非常接近。信道的S参数由某20G带宽VNA测量得到。

图六:某SAS信号在RX实测与TX测试后用信道仿真计算RX端信号波形的对比

什么是预加重/去加重(Pre-emphasis/De-emphasis)?

在图三中我们看到,对于2.5Gbps信号,通过10、20、30、40英寸线长的背板后,接收端的眼图随着长度增加会逐渐闭合。原因在于信道是一个低通滤波器,随着传输线长度的增加,损耗和色散会越来越大,另外,随着频率的增加,损耗与色散效应也越来越明显。而当前的数字电路速度不断提高,通常,在速率高于1GHz的数字电路中,为了把信号能传输更远的距离,通常在发送端使用预加重或去加重的均衡技术。

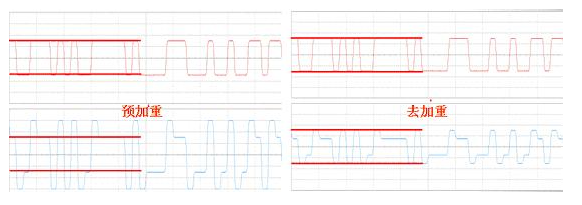

在下图七中左半部分是预加重。预加重保持信号的低频部分不变,提升信号的高频部分;而去加重衰减信号的低频部分,保持高频部分。预加重/去加重的目的都是提升信号中高频部分的能量,以补偿信道对高频部分衰减过大。

图七:预加重 VS 去加重

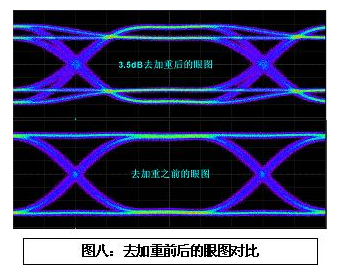

如果在TX端测量经过预加重/去加重的信号的眼图,可以看到如下图八的上半部分所示的“双眼皮”的眼图,而下图八的下半部分是做3.5dB的去加重之前信号的眼图。还有,使用去加重后,TX端信号的抖动会大于未采用加重的信号,在下面的眼图中可以清楚的看到去

加重后眼图

图八:去加重前后的眼图对比

的交叉点比去加重之前的更宽,说明在去加重后测量TX的抖动会更大些。

在当前流行的很多串行数据,比如PCIe、FBDIMM都使用了去加重技术。

高速芯片通常提供了几种预加重/去加重程度和信号幅度可调节,以第二代的PCI Express为例,其比特率为5Gbps,有3.5dB和6.5dB两者去加重模式。

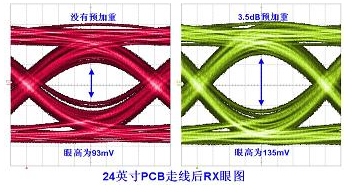

在接下来的案例中,TX为某3.125Gbps信号源,信道为Lattice的带有24英寸传输线的演示板,RX为示波器的两个通道,即两个标准50欧的负载。图九中左边的眼图为TX端没有预加重时RX端测量到的眼图,右边的眼图为TX采用3.5dB预加重后RX端测量到的眼图,前者眼高为93mV,后者眼高为135mV。可见使用3.5dB预加重后,接收端的眼图得到提升。

图九:使用预加重后接收端眼图质量变好

预加重/去加重是广泛应用于高速串行数据芯片的技术。在芯片设计中,芯片厂商通常提供了多种预加重/去加重的程度与信号幅度,在驱动不同信道时可以灵活选择。

对于高速背板设计,我们可以测量不同传输线长度、不同背板连接器的等等情况的信道模型,用力科示波器直接在TX测量该芯片输出的信号,使用信道仿真功能,计算出RX端的信号、眼图与抖动。然后不断调节芯片的预加重/去加重程度,直到获得最佳的RX端的信号质量。

什么是预加重/去加重仿真?

力科的预加重/去加重仿真可以在把未加重信号进行预加重/去加重处理,仿真不同程度的预加重/去加重后的信号。与信道仿真配合,可以实现两个功能:

一,对于IC设计工程师或高速系统设计工程师,可以预先估算芯片的TX端所需的均衡程度

二,对于背板设计工程师,无须修改待测试信号源的预加重或去加重程度,直接测量未作均衡的信号,结合信道仿真功能,计算出多少dB的预加重足以满足该背板设计?或者多少dB的预加重对于某信道可实现最佳的接收端测量结果。

什么是删除“加重”?

力科示波器可以把测量到的带有预加重/去加重的信号消除“加重”,得到没有采用“加重”技术的信号。由于采用去加重后的信号的数据相关性抖动DDj会更大些,所以对删除“加重”后的信号来分析其总体抖动、固有抖动更准确。

图十:力科预加重/去加重仿真的用户界面

什么是均衡器仿真?

力科眼图医生支持目前最流行的CTLE、FFE、DFE三种均衡器。关于这几种均衡器的理论介绍,可参考一些通信理论书籍,在这里仅作简要介绍。

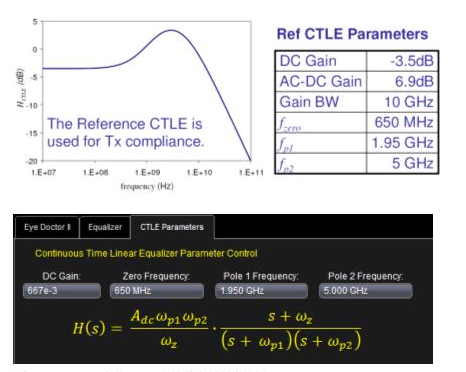

CTLE均衡器

Continuous Time Linear Equalization均衡器(简称CTLE)即连续时间线性均衡器,是一种常见的线性均衡器。在最新的USB3.0中使用了CTLE均衡器。USB3.0的速度高达5Gbps,在不久的将来会在计算机、消费电子类产品上广泛应用。由于USB3.0的速度很高,当USB电缆较长时,RX端眼图很可能已闭合,这时分析眼图与抖动是没有意义的。使用力科眼图医生的CTLE均衡仿真后,对均衡后信号测量眼图与抖动指标,可以精确的验证其性能。结合力科的信道仿真功能,直接测量USB3.0的TX,可以迅速评估不同的信道是否需要均衡?或者均衡后的性能指标。

USB的官方组织规定了USB3.0使用的CTLE均衡器的参数,如下图11左上部分为均衡器的频响,右上方的表格是均衡器的参数,下方是力科示波器中集成了USB3.0的均衡器参数,可方便调用。

CTLE均衡器的优点是功耗低、实现起来很简单、不会增大抖动。

图11:USB3.0的CTLE均衡器参数设置

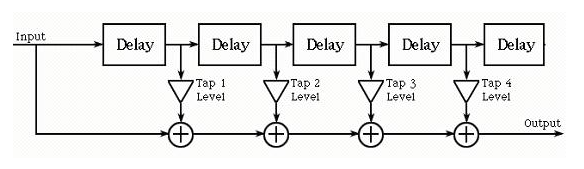

FFE均衡器

Feed Forward Equalization均衡器(简称FFE)是一种常见的模拟均衡器,如下图12所示,由延迟电路(Delay)、乘法器、加法器组成,延迟电路的时间延迟正好是1个比特,Tap系数(tap level)是每一级乘法器(放大器)的增益,输入信号通过每一级处理后相加得到输出波形,即FFE均衡后的波形。

图12:FFE均衡器示意图

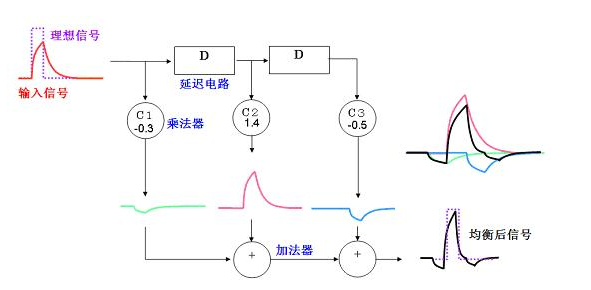

如下图13所示为某3阶FFE均衡器(3个tap)的系统简化示意图,输入信号为左上角的红色信号,淡紫色虚线标识的波形是理想的信号波形,由于信道使到达RX的信号恶化,均衡器的输入信号相比理想波形,其幅度较低、上升时间与下降时间较慢。第一、二、三级乘法器的系数分别为C1=-0.3、C2=1.4、C3=-0.5。第二级乘法器的增益为1.4,可以大大提升信号的幅度,其输出波形如下图13粉红色波形;第一级乘法器的系数C1=-0.3,产生一个负向的脉冲信号,用于补偿信号的上升沿;第三级乘法器的系数C3=-0.5,用于补偿信号的下降沿。三级乘法器的输出相加后的信号为图中的黑色波形,其幅度接近理想信号,上升、下降沿都比均衡器的输入信号更快。FFE的均衡器的响应很像一个高通滤波器。在这个3-tap的FFE均衡器中,第二个乘法器是用于补偿幅度的,由于前面还有一级乘法器,所以称为pre-cursor tap=1的FFE均衡器。在使用力科FFE均衡器参数优化仿真时,需要输入tap的数量和pre-cursor tap的数值,分析软件会自动计算出每个tap的系数。

图13:某3-tap的FFE均衡器的简化示意图

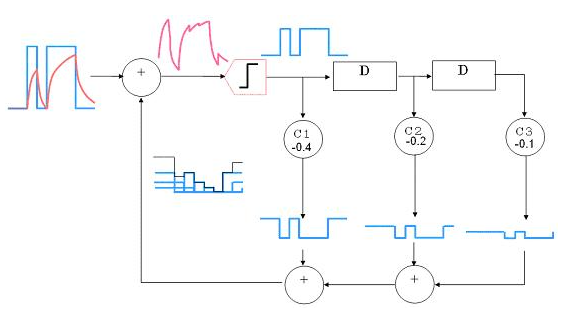

DFE均衡器

Decision Feedback Equalization均衡器(简称DFE)即判决反馈均衡器,是一种广泛使用的非线性均衡器。在眼图医生的高级模式下可以设置DFE均衡器的参数,也可以自动优化出DFE均衡器的参数。如下图14所示为某3-tap的 DFE均衡器的示意图。 DFE均衡器中包括了延时电路、乘法器和加法器,和FFE均衡器有些相似。不过DFE的反馈回的信号是二进制信号,而FFE反馈的是模拟信号。在DFE均衡器仿真时,只需在眼图医生中输入tap的数值,分析软件会自动计算出每个tap的系数。

图14:某3-tap的DFE均衡器的简化示意图

DFE不会放大噪声与串扰,易于实现,在高速收发器芯片中非常流行。比如Altera和Xilinx的某些FPGA的收发器就集成了DFE和CTLE。

均衡器仿真的作用

对于5Gbps以上的串行链路,RX端通常使用了均衡器,如果用示波器在RX端测量,只能得到未均衡的信号,可能其眼图已闭合,无法从物理层的测试手段验证接收端的性能。使用均衡器仿真后,可以计算出均衡后的波形、眼图和抖动,能进一步验证真正的接收端的电气特性。

另外,对于高速收发器芯片厂商,使用力科的均衡器仿真,可以预估某信道最适合的均衡器以及相关参数。大大加快了芯片的设计与验证速度。

图15:某8.5Gbps驱动24英寸传输线的均衡器优化

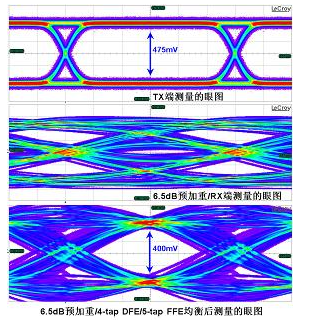

在图15中,最上面的眼图是直接测量某8.5Gbps信号的眼图;中间的眼图是TX端做了6.5dB预加重后,通过24英寸微带线的PCB后在RX端测量的眼图,可见眼图已闭合;在下方的

眼图是接受端使用4-tap的DFE和5-tap的FFE后测量的眼图,可见通过RX端均衡后,眼高达到400mV,信号质量得到很大的改善。

结语

眼图医生提供了高速串行链路的发送端、信道、接收端的全方位的仿真与分析能力,改变了传统的高速串行设计的研发与调试方式。配合力科30GHz带宽的实时示波器SDA830Zi,可以实现当前流行的10G信号的信道仿真、均衡仿真、以及全面的测量与分析。

审核编辑:汤梓红

-

如何使用 Verilog 进行数字电路设计2024-12-17 2210

-

高速数字电路设计资料分享2023-08-17 595

-

高速数字电路设计.zip2022-12-30 798

-

高速数字电路设计教材-华为2022-06-13 1236

-

高速数字电路设计-华为2021-04-21 1158

-

模拟电路原理在高速数字电路设计的应用分析《高速数字电路设计教材》2018-09-10 1784

-

高速数字电路设计大全2017-01-17 1162

-

高速数字电路设计及EMC设计2016-03-29 1133

-

高速数字电路设计(完整版)2016-03-09 1958

-

招聘:数字电路设计师2015-02-27 3564

-

华为《高速数字电路设计教材》2010-11-08 2148

-

数字电路设计2009-08-26 3124

-

高速数字电路设计2007-10-16 3478

全部0条评论

快来发表一下你的评论吧 !