关于DDR4信号质量测试 DDR4-DRAM的工作原理分析

存储技术

描述

导读:

DDR4全称,DDR4-DRAM,与其他DDRDRAM一样,是当前电子系统架构中使用最为广泛的的RAM存储器。 这句话可以分解出3个关键字:存储器、DRAM、DDR4。

存储器: 先说存储器,说到存储,顾名思义,它是个动词,以生活为例,假如有个酸奶,你不想吃的时候,将酸奶存到某冰箱、某层、某个位置,当你想吃的时候,在某冰箱、某层次、某个位置中取出该酸奶。 这个过程,我们称为存储,结合生活,我们可以看到存储要有3个关键动作: 1、酸奶放哪了,你得知道。如果不知道放哪了,酸奶就跟丢了一样。这个过程,映射到电子领域中,称为“寻址”。 2、存储酸奶、取出酸奶。你需要先走到某冰箱跟前,拉开某层抽屉,在具体某个位置,拿出酸奶,这个过程,映射到电子领域中,称为“读/写” 3、酸奶放到那个位置,在需要的时候,得还能吃。这个过程,映射到电子领域中,称为“数据保存”。 所以,概括一下,存储器就是“可以寻址”、“能读写数据”、“能保存数据”的一种电子器件。

DRAM: 我们再说说DRAM。DRAM全称Dynamic Random Access Memory,翻译过来为动态随机读取存储器。所谓随机,指的是“想存哪个位置,就存哪个位置”,听起来很自由,很灵活。所谓动态,指的是保存数据过程中,需要不断的补充电量,听起来很耗电,很费劲,为啥我们还要用DRAM结构?因为在电路结构上,DRAM结构比SRAM简单很多。

DDR: 最后说说DDR。我们聊到DDR,大家都会联想到存储器,但是实际上DDR并不指代存储器,DDR实际是一种技术,全称Double Data Rate,翻译过来为双倍速率,只是这都技术广泛使用在DRAM上,所以人们习惯将DDR代指为存储器,所以在后续的硬件设计过程中,在其他总线上看到DDR,请不要惊慌,因为你看到的DDR可能不一定和存储有关。 那双倍速率指的是什么?我们可以简要说下,初代存储器在读写数据时,每次都在时钟信号从低变高或从高变低时,采样数据,在1个时钟周期,只能采样1个数。后续聪明的人类在时钟从低到高时,采样一个数据,时钟从高到低时,再采样1个数据,一个时钟周期,可以采样2个数据。所以读写速度比以前快了2倍。这种技术手段,就指的是DDR。 所以,概括下:DDR4-DRAM是第四代支持双数据读取,支持随机位置存取的静态存储器。

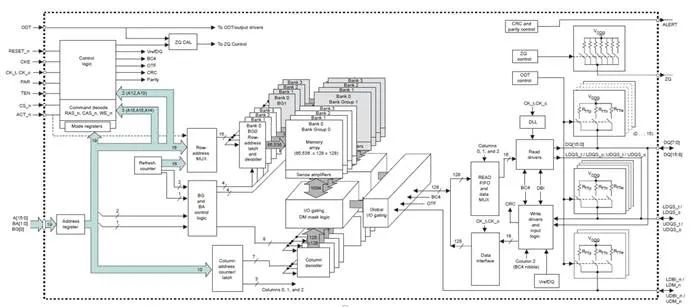

DDR4-DRAM的工作原理: 一颗DDR4芯片的内部功能框图如下

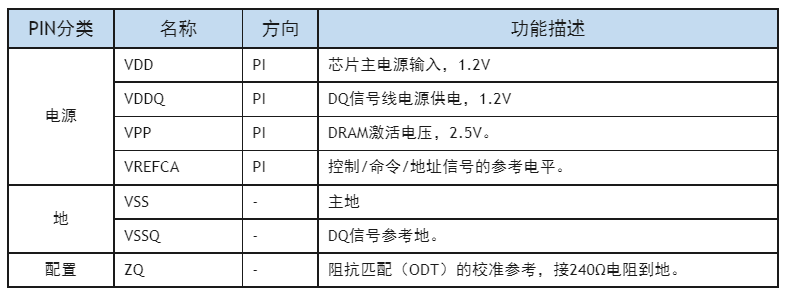

其引脚按照功能可以分为7类:前3类为电源、地、配置。

后4类为:控制信号、时钟信号、地址信号、数据信号

一、DDR4 信号完整性测试新要求

在 DDR4 规范 JESD79‐4 中,对物理层信号测试要求有:DQ 眼图模板测试、抖动分析、电气特性测试,时序测试。相比 DDR3,DDR4 对眼图测试和抖动测试提出了新的要求。

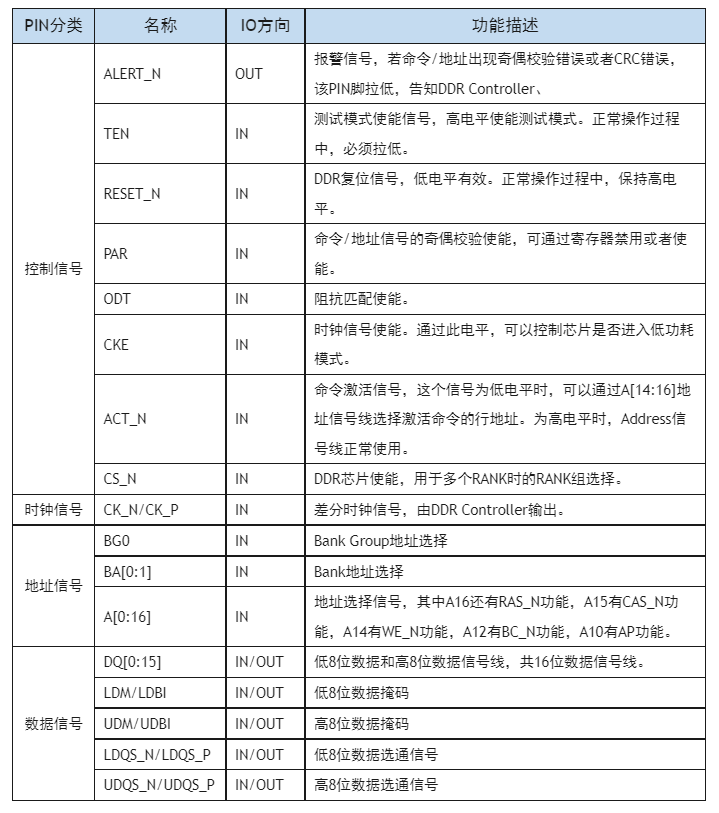

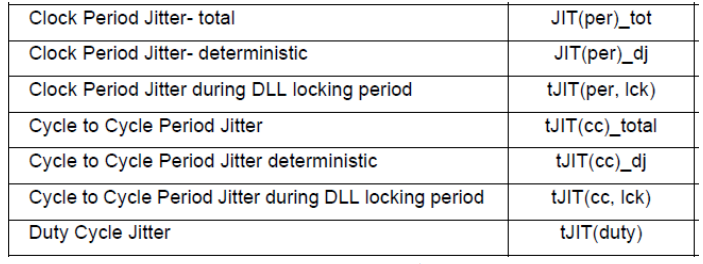

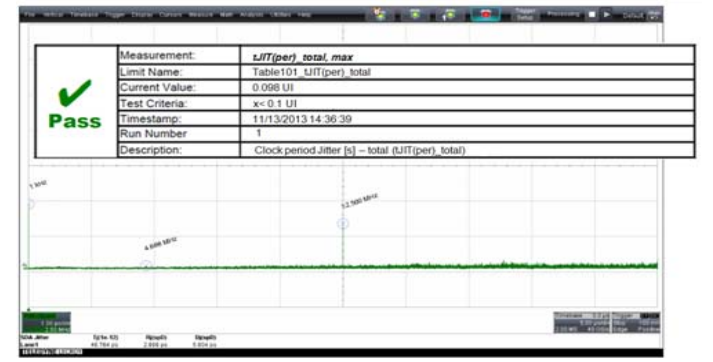

抖动测试

在 DDR3 的测试中,对 Clock 的抖动的测试要求是:Period Jitter、Cycle‐Cycle Jitter、Duty Cycle Jitter。DDR3 的 Spec 中做了这样的推算:如果你的内存满足了规范要求的所有电气特性和时序特性,就可以一直正常的运行。现实状况下,这是没有考虑其他因素的理想情况,像随机抖动等也会影响产品的工作,而 DDR3 都没有对这些进行测试。

DDR3 Clock 抖动测试

在 DDR4 的规范中,采用了更实际的方法来考虑这些因素,测试要求包含了随机抖动 Rj 和确定性抖动 Dj,在规范中,总体抖动 Tj 被定义为在一定误码率下的确定性抖动 Dj 和随机性抖动 Rj 的和,对抖动做了分解。

DDR4 Clock Jitter 要求

Lecroy Qualiphy‐DDR4 Jitter 测试结果

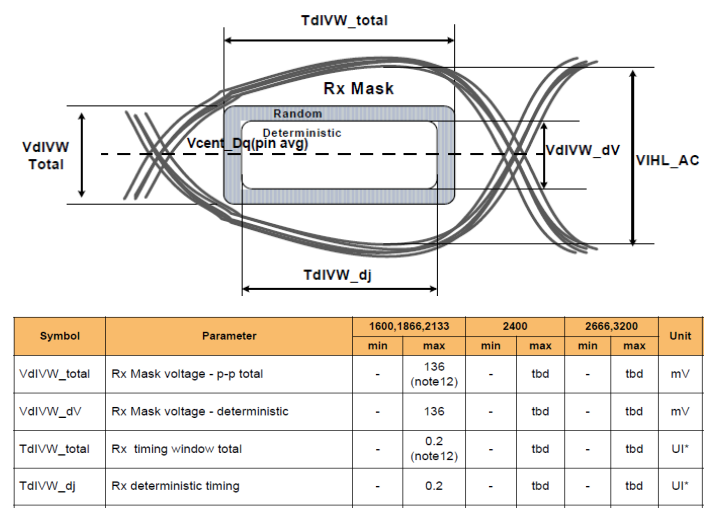

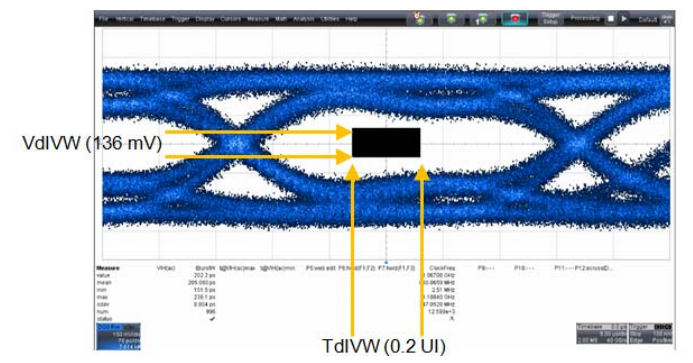

眼图模板测试

在 DDR3 测试中,眼图只是作为一个 Debug 的手段,不是强制要求测试,而且没有模板。但是在 DDR4 中,要求进行 DQ 输入接收端眼图模板测试,下图是眼图模板的定义,在 DDR4‐2133 及以下频率,TdIVW_total 和 TdIVW_dj 相等。VdIVW_total 和 VdIVW_dV 相等,从本质上,现在还没有在模板中定义随机成分。

DDR4 眼图模板定义

DDR4 DQ 眼图

二、DDR4 信号完整性测试挑战

DDR4 的速率提升一倍,同时信号电压降低也接近一倍,这对测试探测技术提出了更高的要求。

DDR4 规范中的所有测试都是定义在 BGA 或者 DIMM 的管脚处,但是,在很多时候,我们很难直接探测到 BGA 管脚处,这样测出来的结果误差会非常大,解决方案是使用 Interposer 夹具或者虚拟探测技术,探测到理想点的波形。

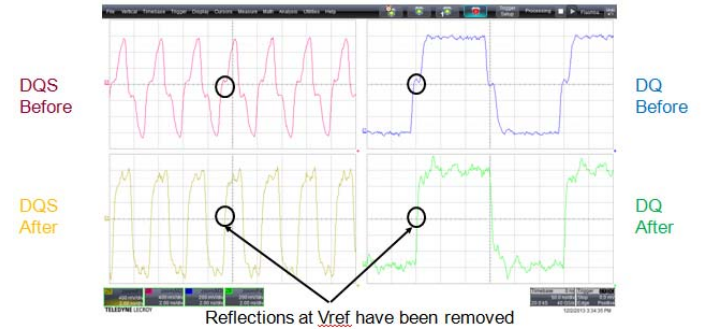

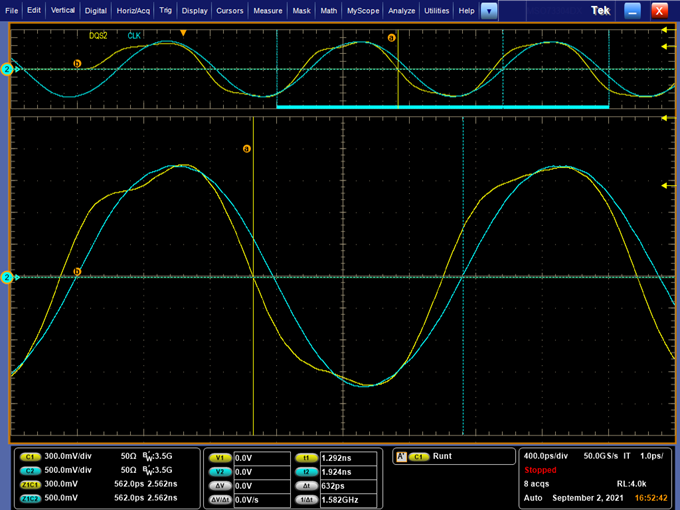

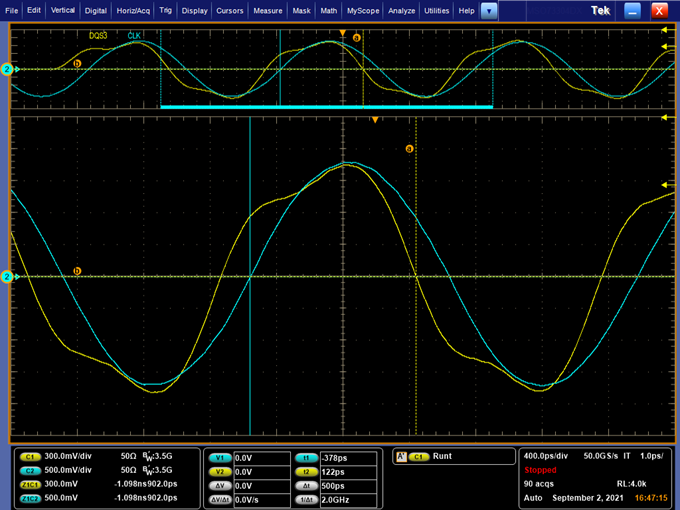

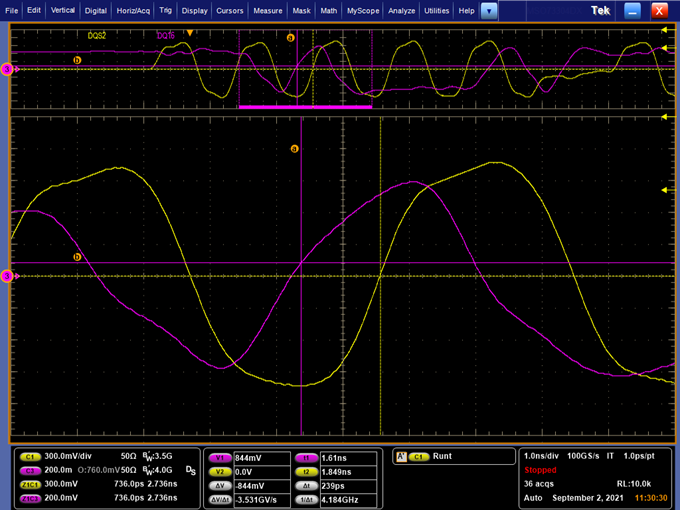

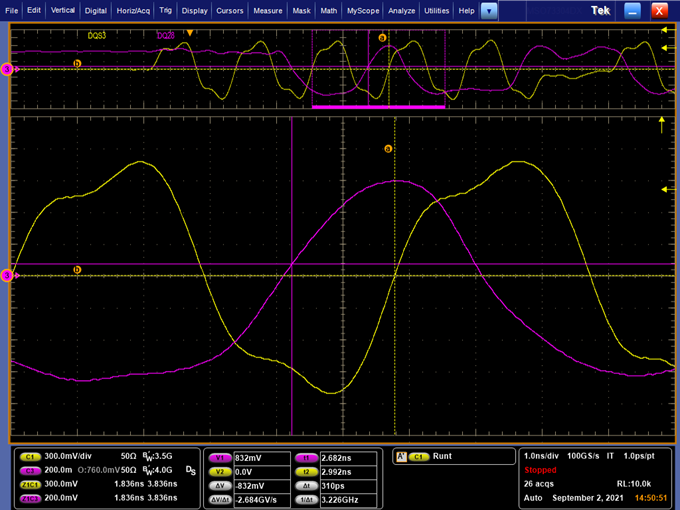

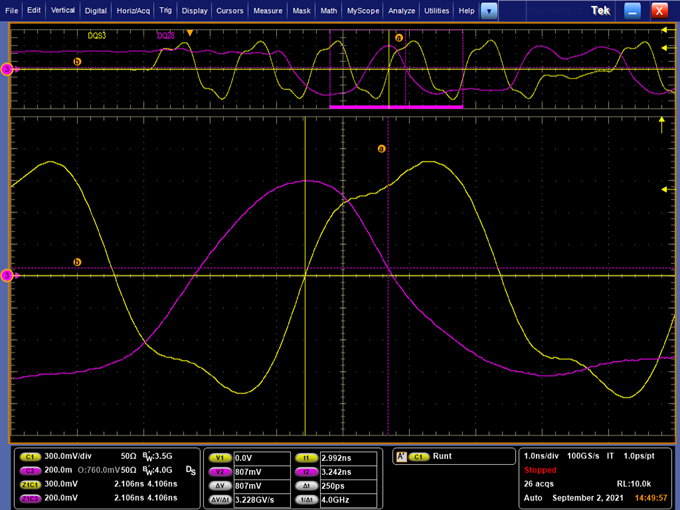

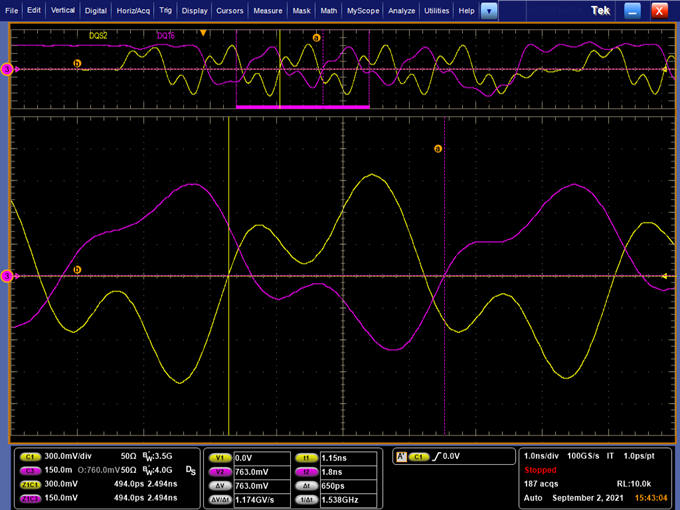

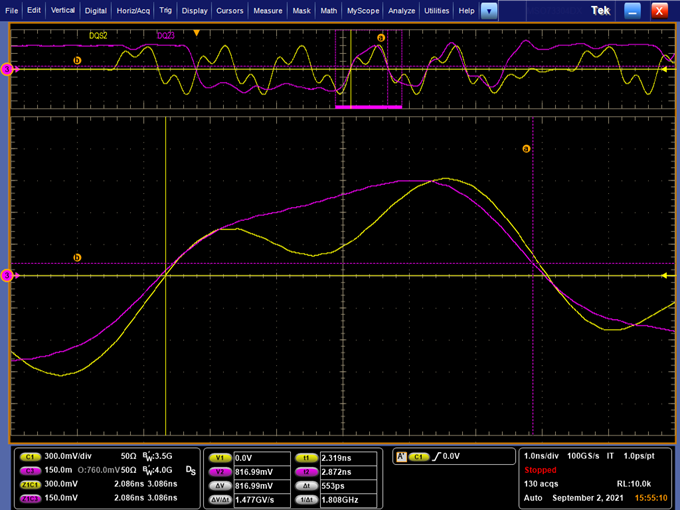

下图是使用 Virtual Probe 测试 DQS 和 DQ,上方是实际测试点的波形,下方是使用Virtual Probe测试到的BGA处的信号波形,可以很明显的看到,反射被去除了,这样测试结果更加准确。

三、DDR4 测试点选取原则

DDR测试点选取的一般原则,即:测读信号尽量靠近CPU,测量写信号尽量靠近RAM。

首先,考虑到走线对信号的衰减,一般在靠近芯片的接收侧对信号进行量测,这样,“看”到的信号和芯片“看”到的信号会更加接近。

其次,这样也会减小反射。

探头的接入或多或少会导致接入点的阻抗产生变化,原本100Ω左右的差分对走线在探头连接处变成其他的值(例如50Ω),这样信号会在这个点产生反射。一般DDR的接收端阻抗的连续性没有发送端好,所以信号在接收端也会产生反射。

如果信号前进过程中两个反射点离得比较远,距离(单位为inch)>信号的上升时间(单位为ns),会对信号产生比较明显的影响,如果量测到的信号在上升沿有回沟或者在信号高低电平中间有凹陷,这些都是多次反射造成的。

建议探头的连接点在DDR信号的接收端,能减少这样多次反射带来的影响。

四、DDR4 信号完整性测试案例

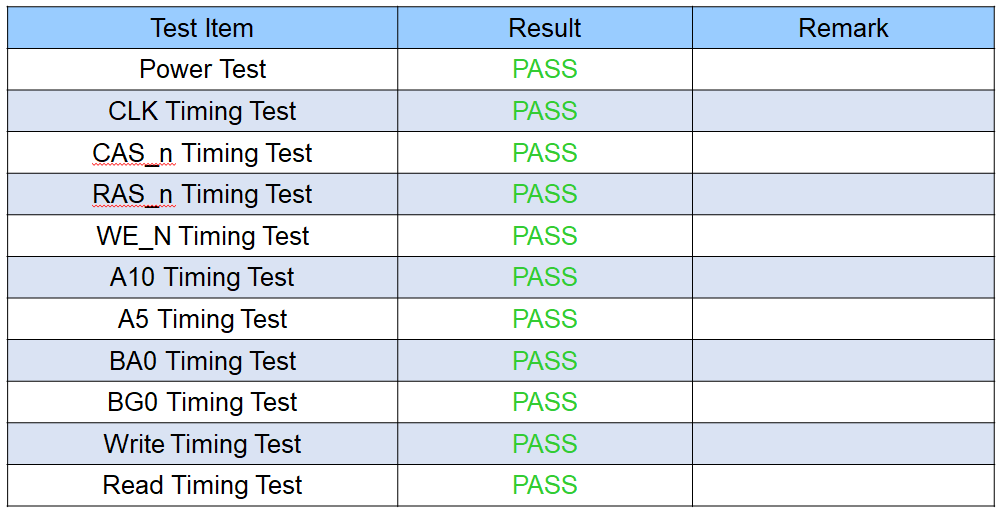

(1) DDR4测试项目及测试结果:

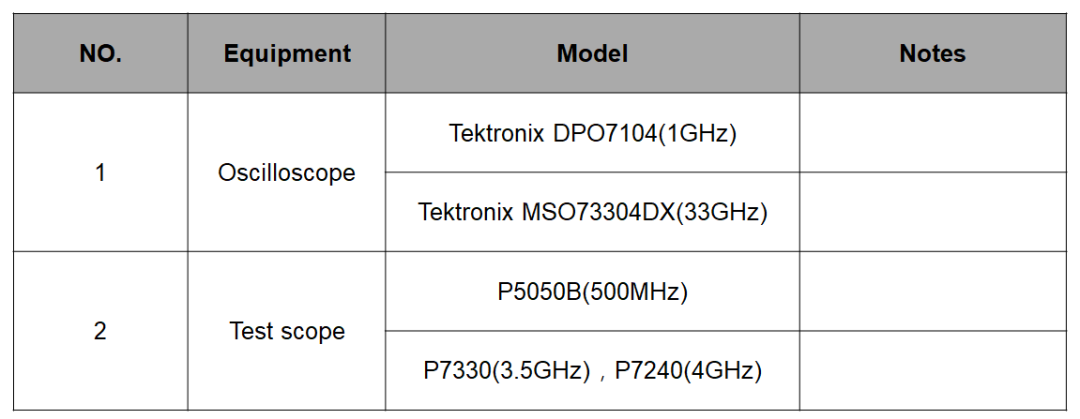

(2) 测试设备及标准:

(3) 测试图片及结果:

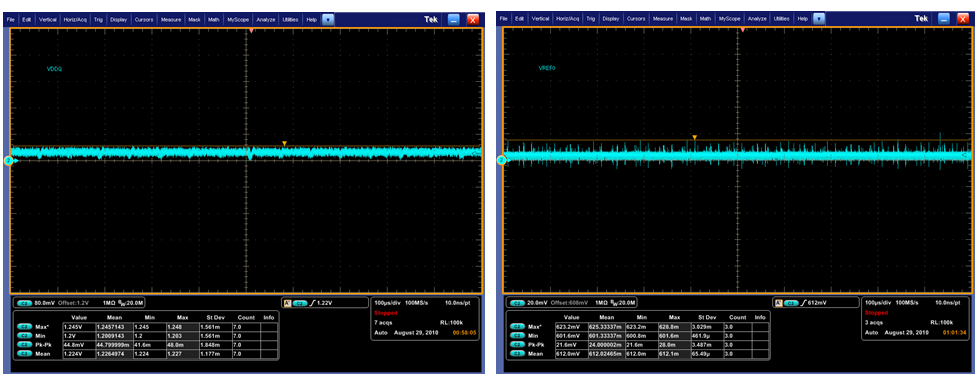

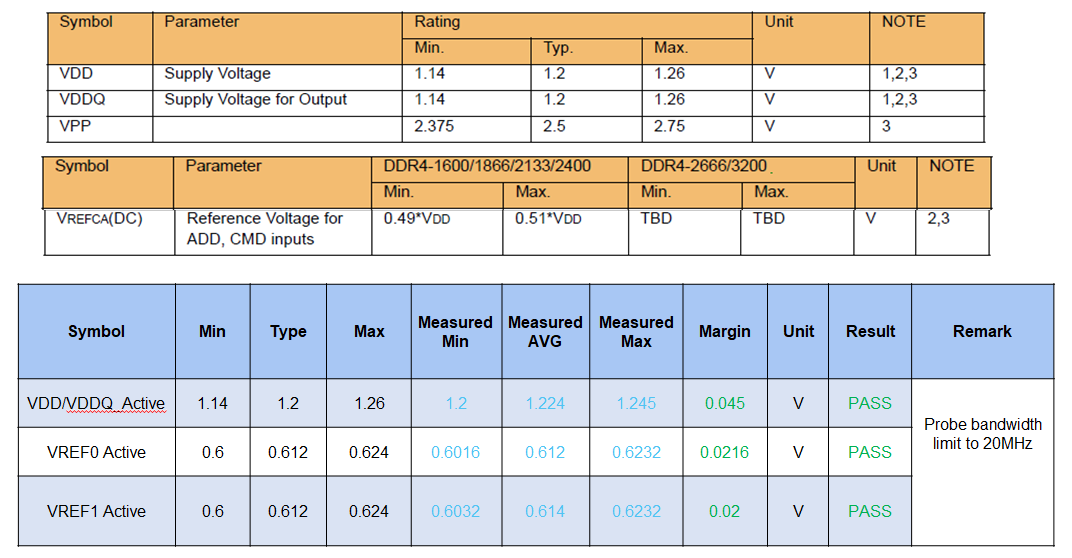

Power Test

Power Test Spec& Result

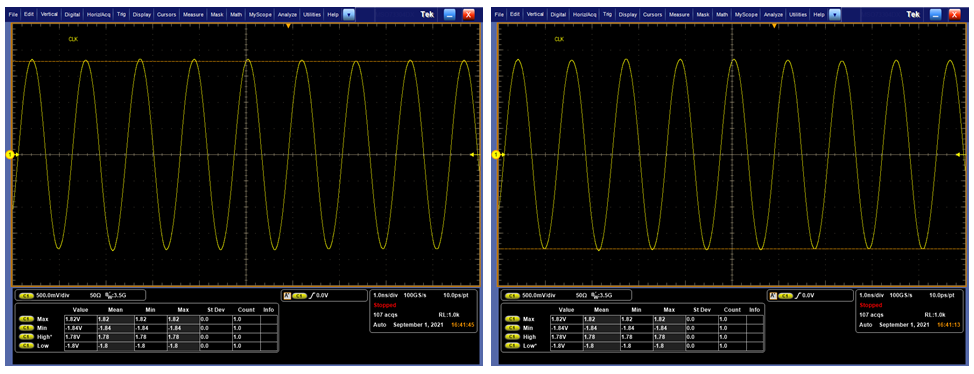

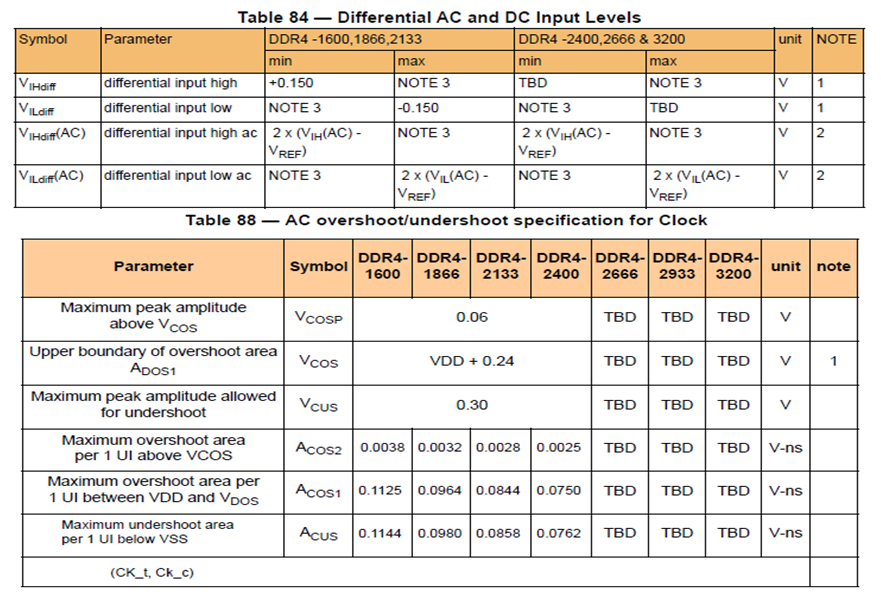

CLK Timing

CLK Timing Test Spec

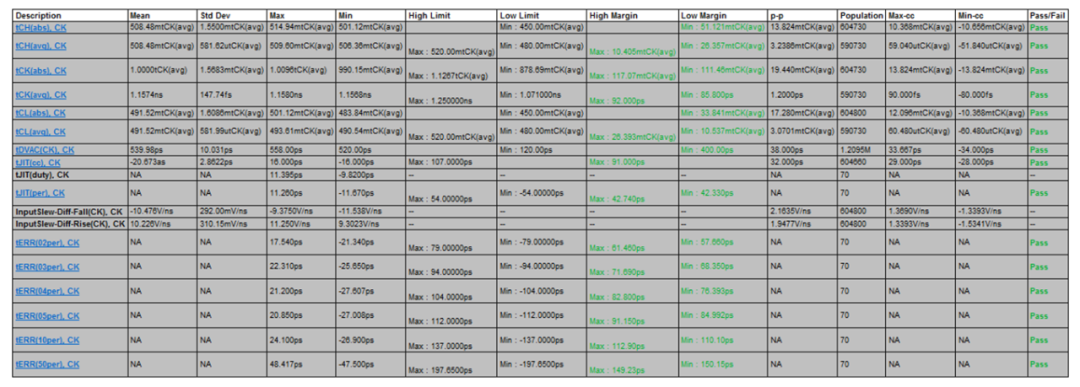

CLK Timing Test Result

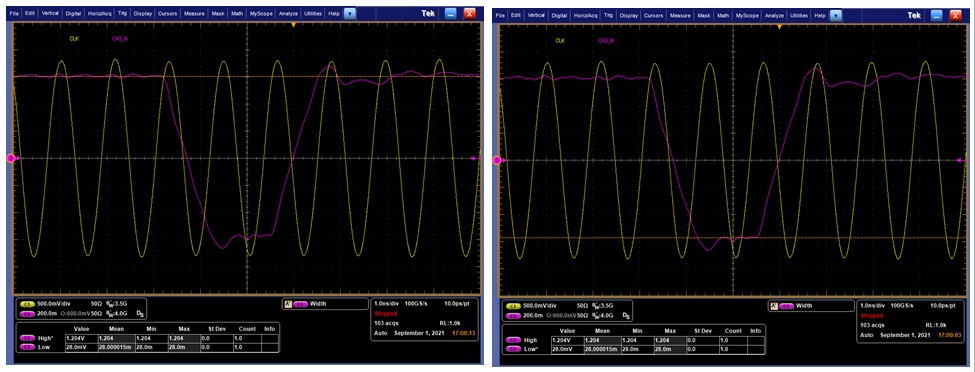

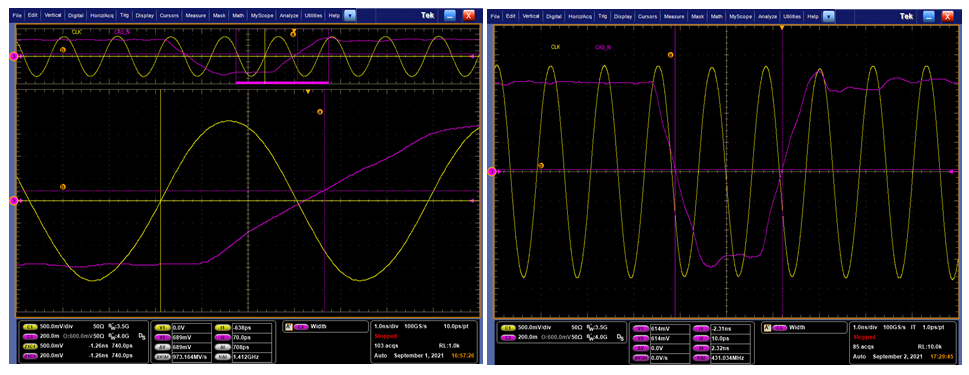

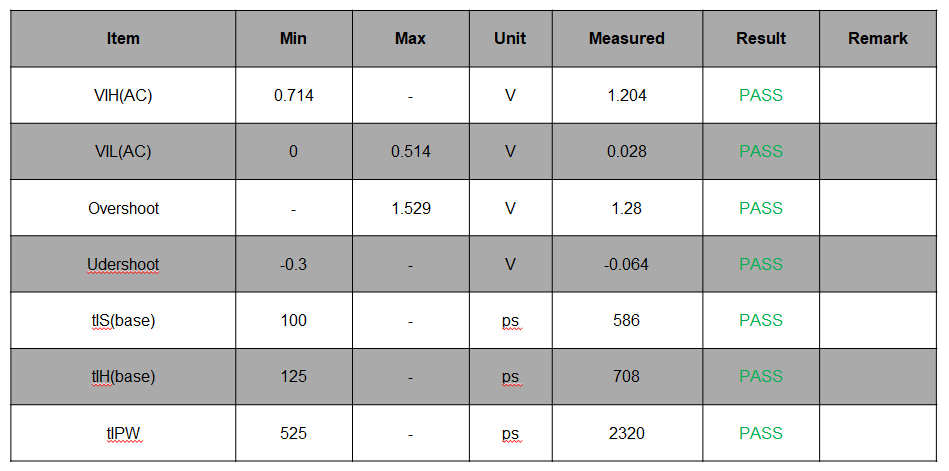

CAS_n Timing Test

CAS_n Timing Test Result

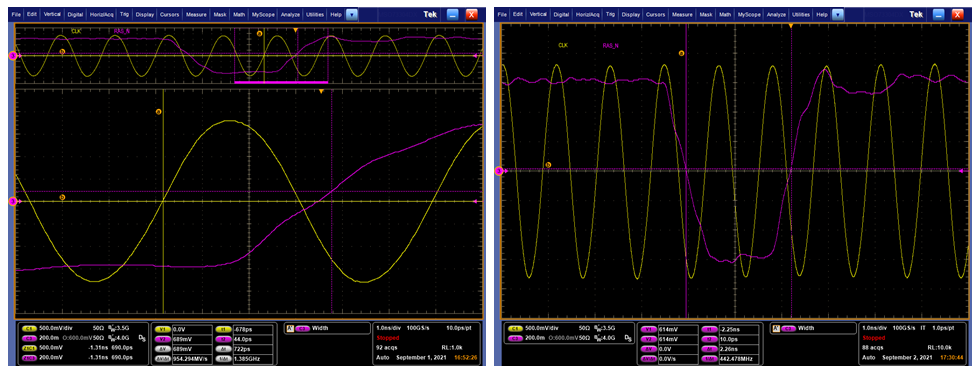

RAS_n Timing Test

RAS_n Timing Test Result

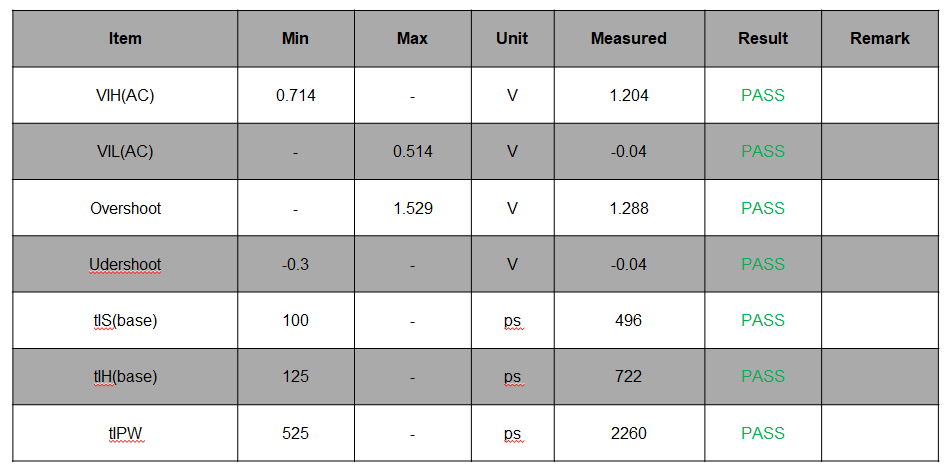

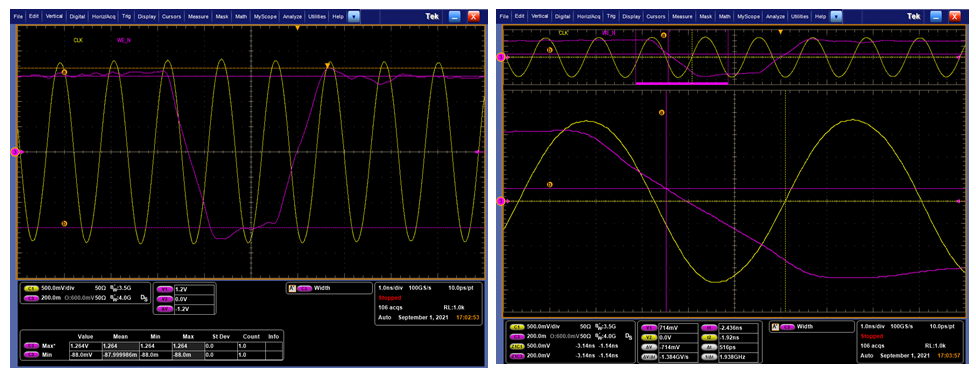

WE_N Timing Test

WE_n Timing Test Result

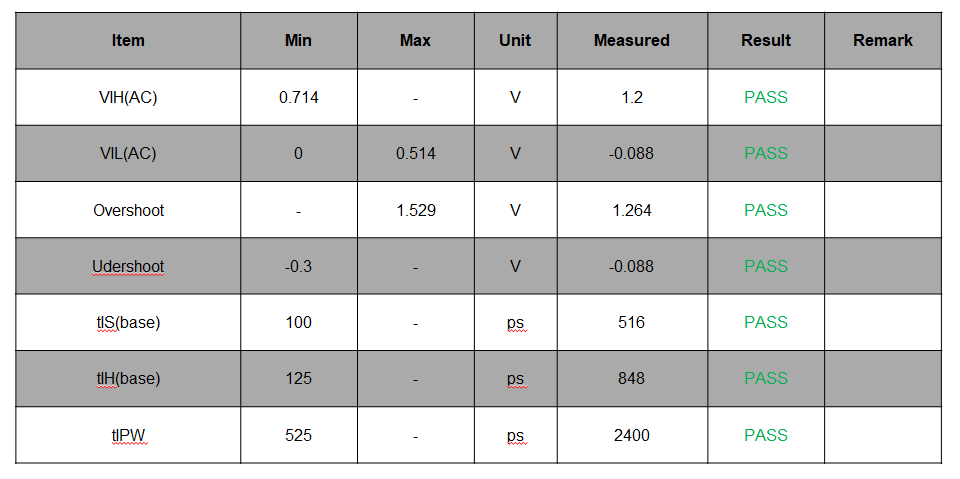

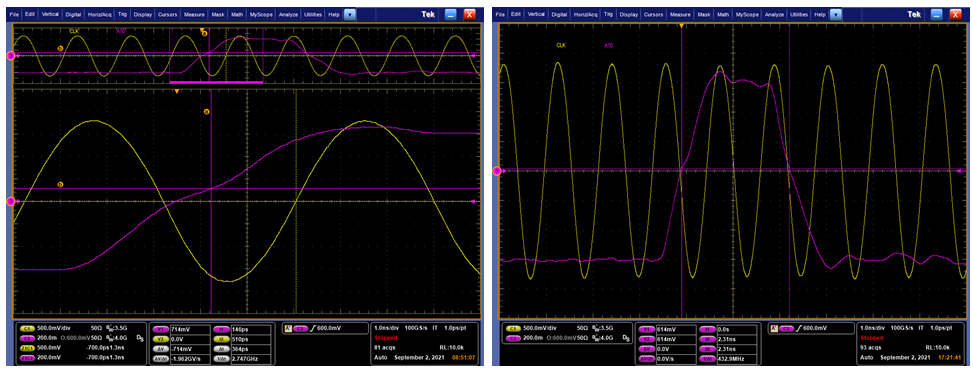

A10 Timing Test

A10 TimingTest Result

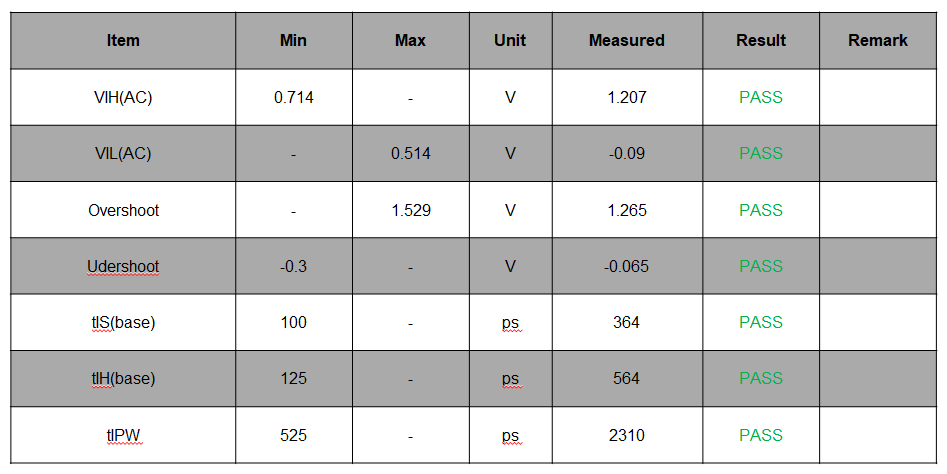

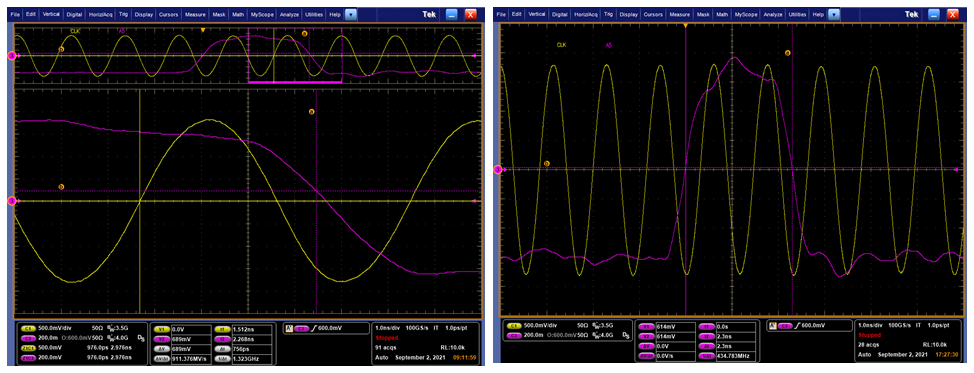

A5 Timing Test

A5 TimingTest Result

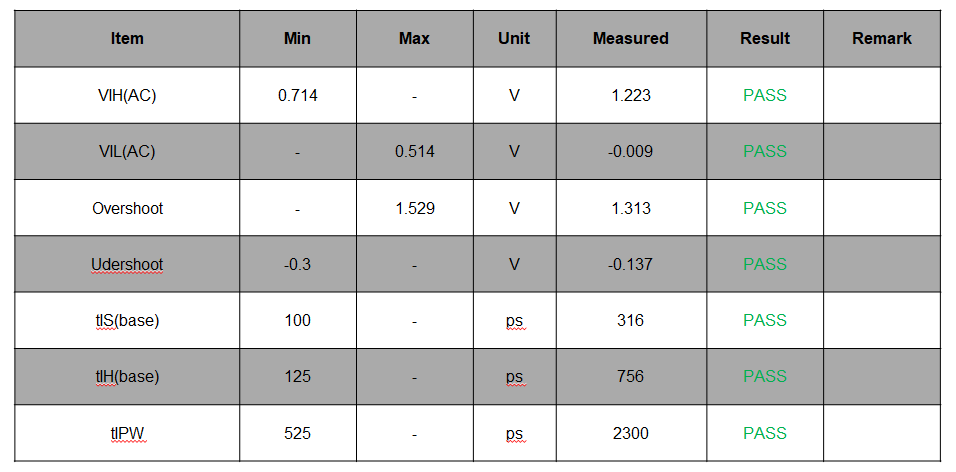

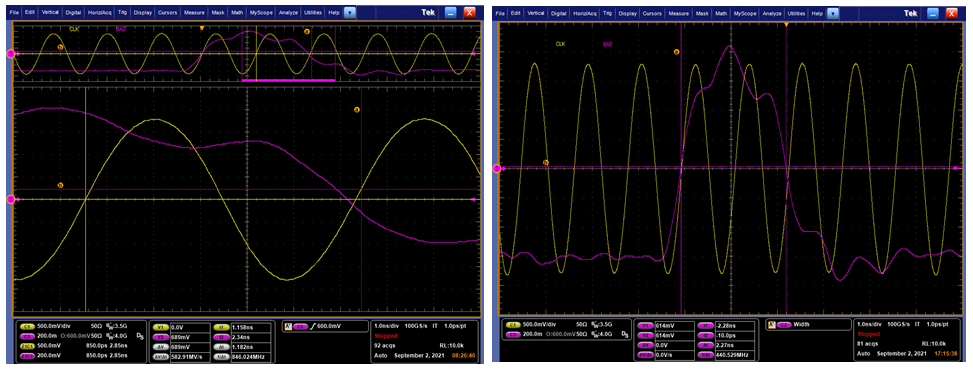

BA0 Timing Test

BA0 TimingTest Result

BG0 Timing Test

BG0 TimingTest Result

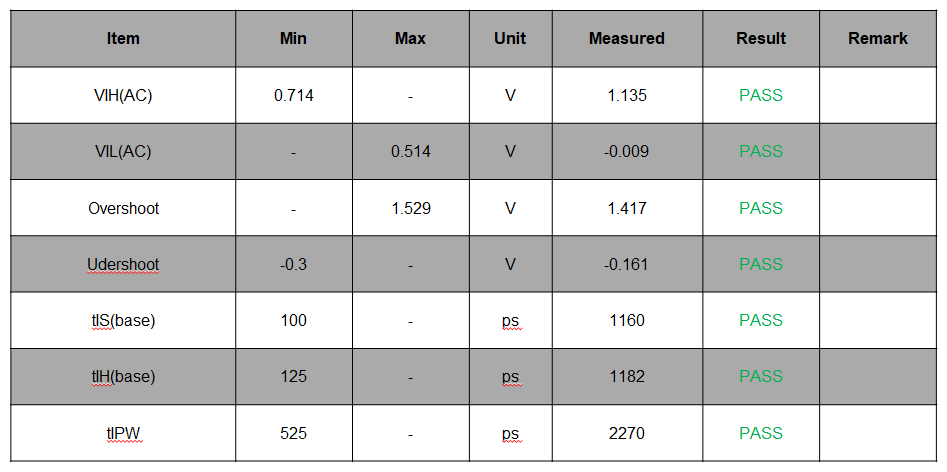

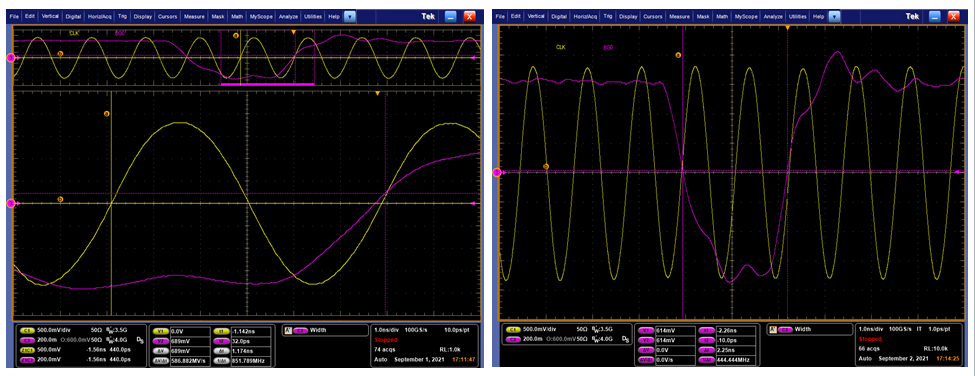

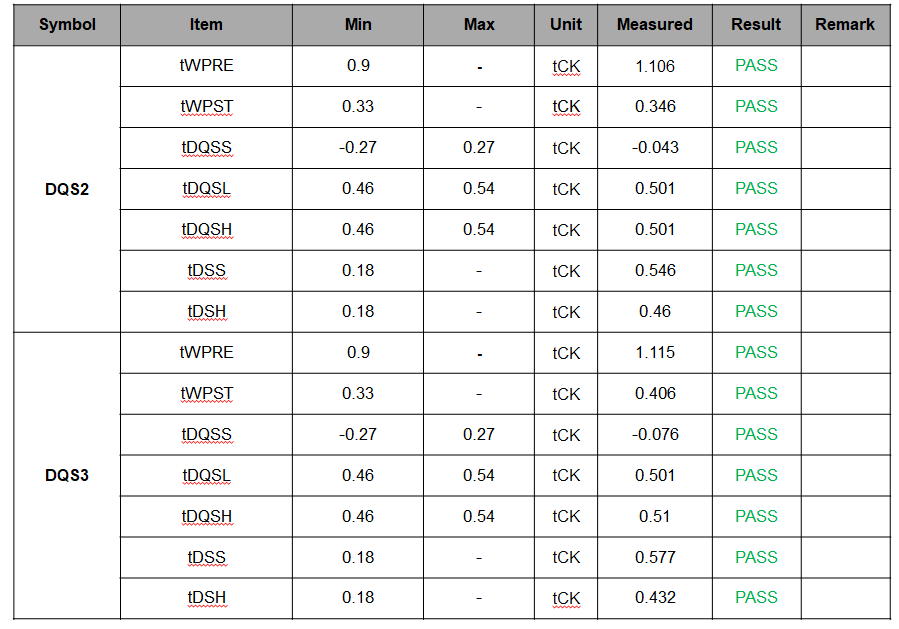

Write Timing Test

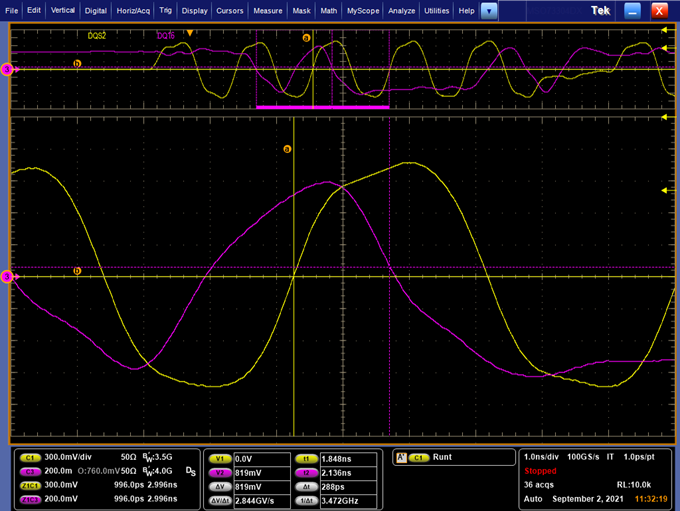

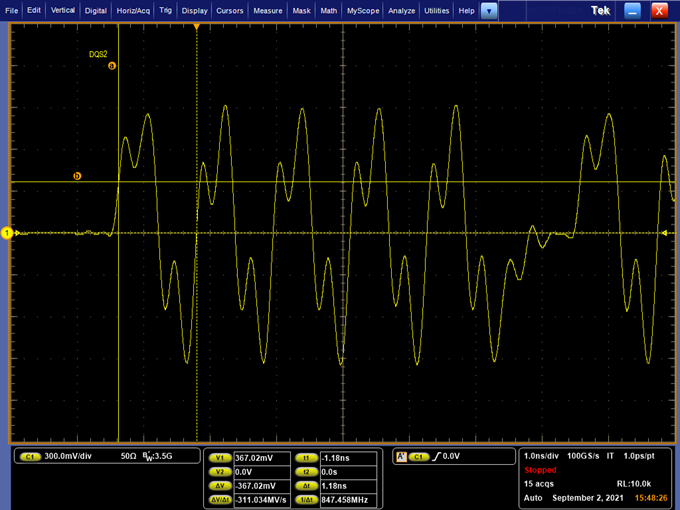

DQS2 Write Preamble tWPRE

DQS2 Falling Setup To From CKRising tDSS

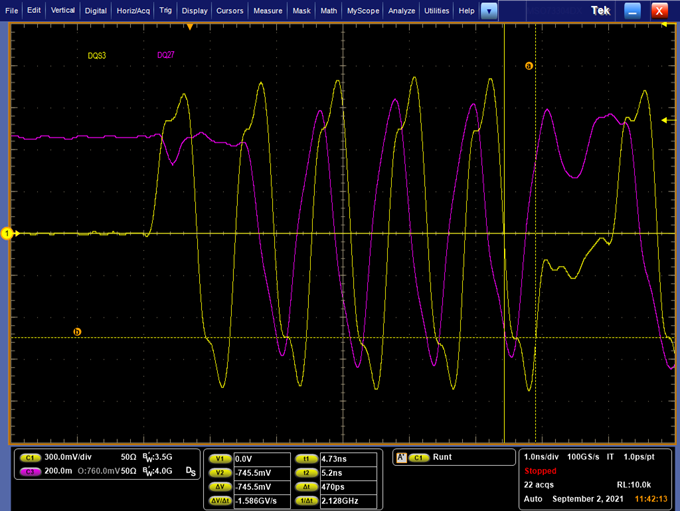

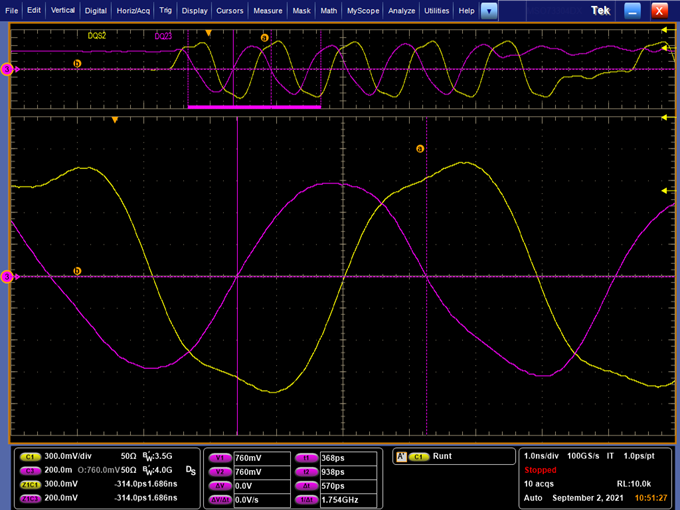

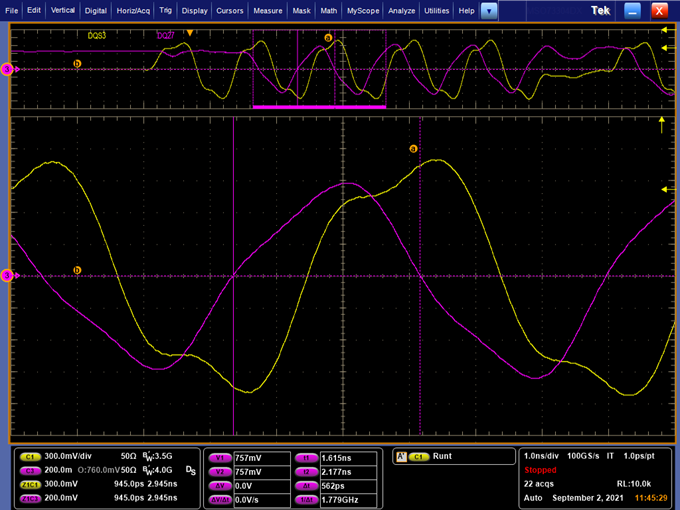

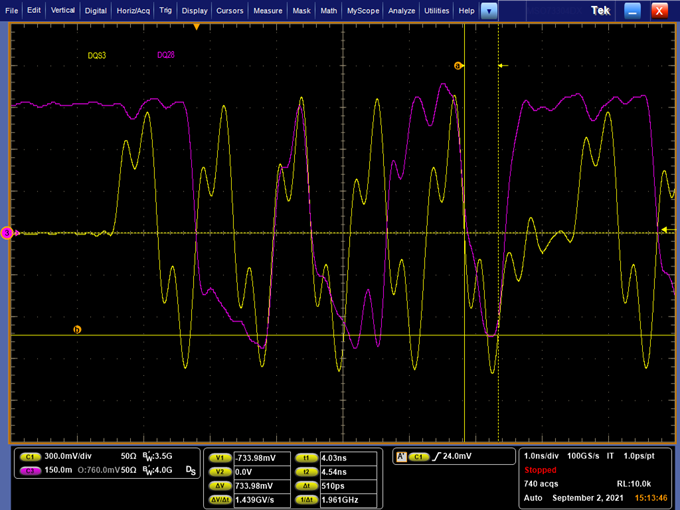

DQS3 Write Postamble tWPST

DQS3 Falling Setup Hold From CK Rising tDSH

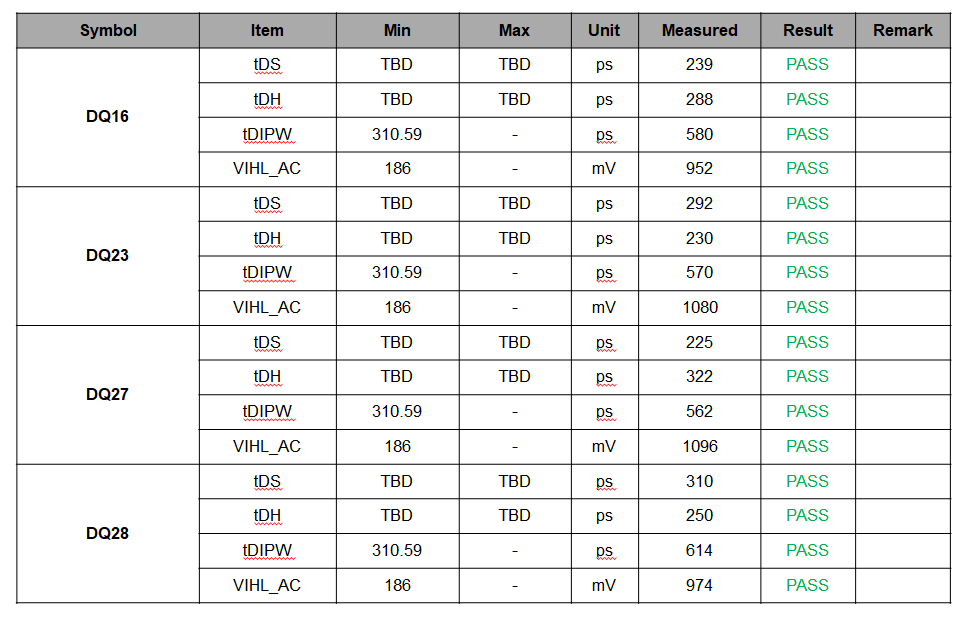

DQ16 Input Set Time tDS

DQ16 Input Hold Time tDH

DQ23 AC Input Pules Width tDIPW

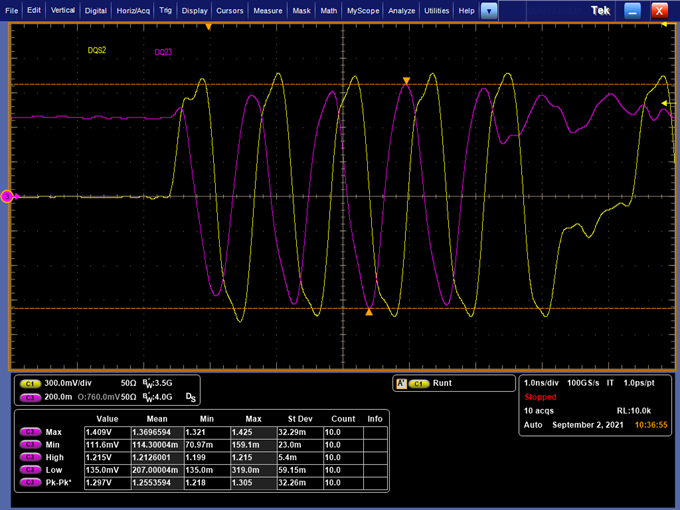

DQ23 AC input swing pk-pk

DQ27AC InputPules Width tDIPW

DQ28 Input Set Time tDS

DQ28 Input Hold Time tDH

Write Data Test Result

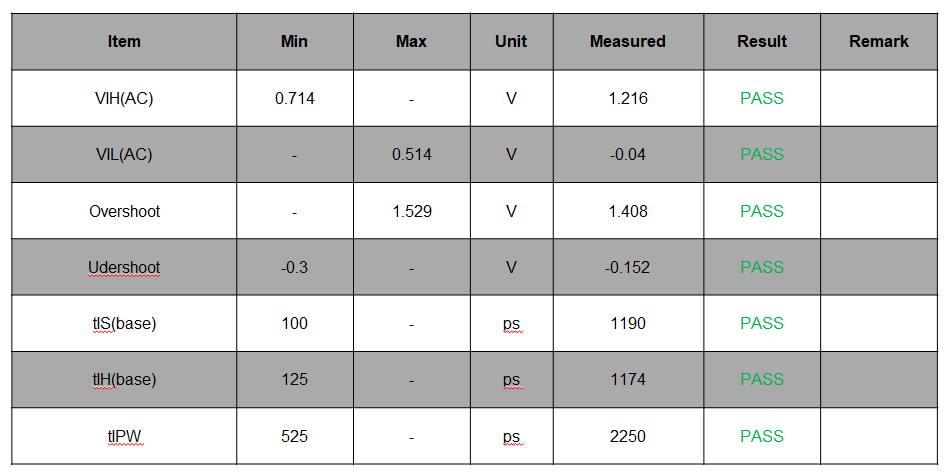

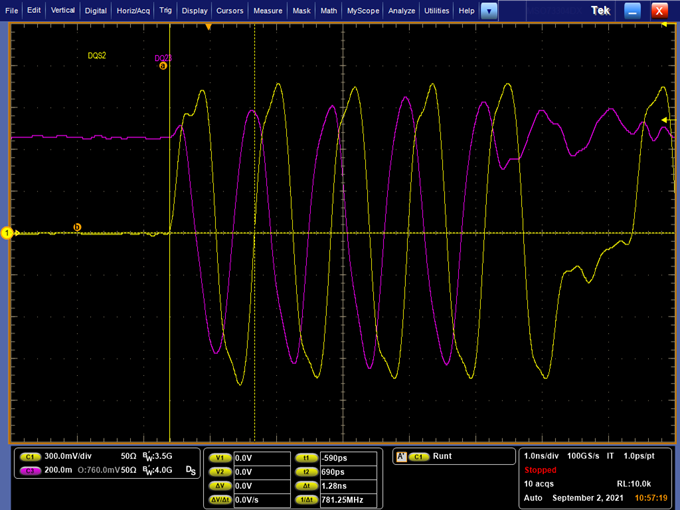

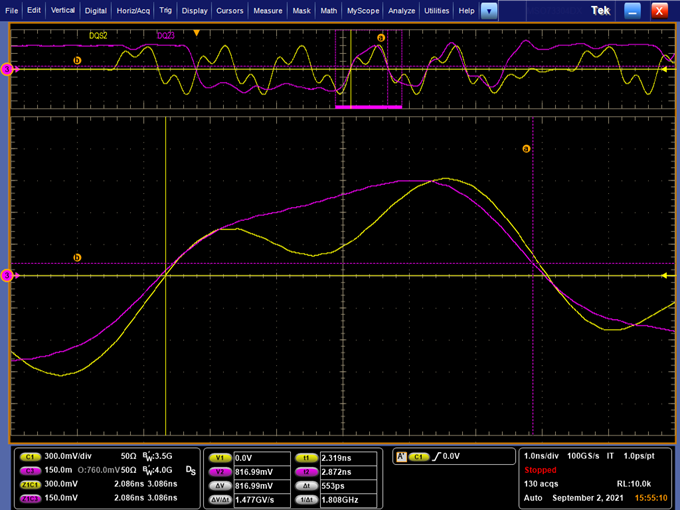

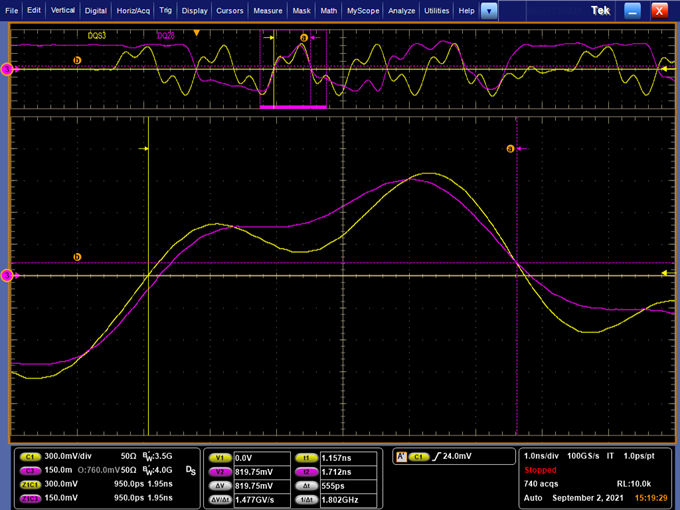

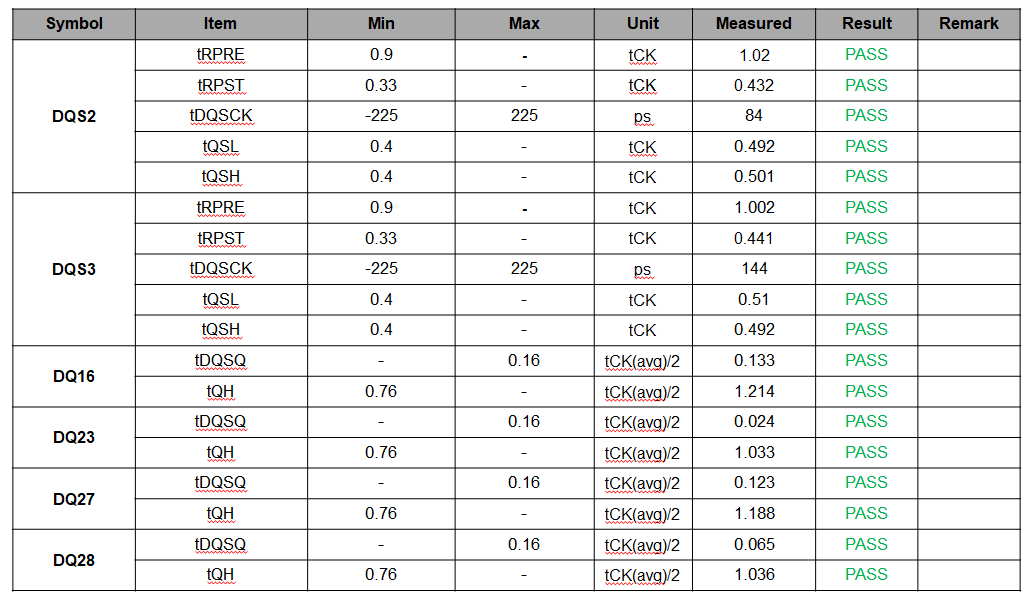

Read Timing Test

DQS2 Read Preamble tRPRE

DQS3 Read Postamble tRPST

DQ16 Output Hold Time From DQS2 tQH

DQ23 Output Hold Time From DQS2 tQH

DQ27OutputHoldTime From DQS3 tQH

DQ28 Output HoldTime From DQS3 tQH

Read Data Test Result

启威测实验室提供DDR2/3/4/5信号完整性测试及一致性验证。

编辑:黄飞

-

DDR4信号完整性测试要求2024-01-08 5207

-

DDR4的工作原理以及寻址方式2021-11-11 2513

-

DDR4,什么是DDR42010-03-24 4254

-

怎样降低DDR4系统功耗2017-10-13 2066

-

ddr3及ddr4的差异对比2017-11-07 56509

-

ddr4和ddr3内存的区别,可以通用吗2017-11-08 32657

-

DDR4技术有什么特点?如何采用ANSYS进行DDR4仿真?2018-10-14 28346

-

DDR4设计规则及DDR4的PCB布线指南2019-07-26 52588

-

DDR4通道中过孔 stub对信号质量的影响分析2021-03-23 8120

-

DDR4原理及硬件设计2021-11-06 3435

-

专门为内存颗粒测试设计的DDR4/DDR5 Interposr测试板2022-10-10 9482

-

DDR4协议2022-11-29 1737

-

DDR4和DDR3内存都有哪些区别?2023-10-30 14900

-

什么是DDR4内存的工作频率2024-09-04 7971

-

DDR5内存的工作原理详解 DDR5和DDR4的主要区别2024-11-22 9433

全部0条评论

快来发表一下你的评论吧 !