基于仿真工具对100VN TrenchMOSFET器件设计研究

功率器件

描述

摘 要 本文基于仿真和实验方法,开展了 100VN 沟槽 MOSFET 的设计研究工作。通过沟槽深度,体区注入剂量和栅氧化层厚度拉偏,获得了对击穿电压,阈值电压和导通电阻的影响规律并对机理进行了分析,仿真工具同时描述了器件内部的电流路径和碰撞电离率分布。随着沟槽深度增加击穿电压先升后降,导通电阻则表现为相反趋势;击穿电压与注入剂量具有弱相关性,阈值电压随注入剂量增加而升高;击穿电压随着栅氧化层厚度增加整体表现上升趋势,但变化幅度不大,阈值电压与厚度变化表现出强相关性。通过逐步优化获得了最终结构和工艺参数为沟槽深度 1.5μm,体区注入剂量1.3E13,栅氧化层厚度 700A,通过流片获得器件最终电性参数为击穿电压为 105.6V,阈值电压 2.67V,导通电阻 3.12mR,相较于仿真参数分别有 98%,94%和 75%的变化率,研究过程中相关参数设计及理论分析对于同行业研究具有一定的参考价值。

1 引言

功率半导体器件( Power Semiconductor Device)作为电力控制的核心电力电子器件,应用于电能的变换和控制[1]。近年来,随着 5G 通讯发展的带动,新能源汽车、高速列车、光伏、风电、手机、电脑、电视机、空调等各个领域对于功率半导体器件的需求量大大增加,促进了该领域的飞速发展。金属氧化物半导体场效应晶体管(MetalOxide Semiconductor Field Effect Transistor,简称MOSFET)作为一种重要的功率半导体器件,其栅极通过电压控制既能完成器件导通,又可以实现关断,具有高输入阻抗和低导通损耗的优点,现阶段广泛的应用于开关电源、电机控制、移动通讯等领域。

沟槽(Trench)MOSFET 是一种新型垂直结构的 MOSFET 器件,是从传统平面 MOSFET 结构基础上优化发展而来,Trench MOSFET 由于将沟槽深入硅体内,在设计上可以并联更多的元胞,从而降低导通电阻(Ron),实现更大电流的导通和更宽的开关速度。

王颖等人[9]基于仿真手段,研究和分析了外延杂质对器件 Ron 和击穿电压(BVDSS)的影响,所设计的新结构 Ron 降低了 18.8%。王南南等人对沟槽深度对器件阻态和通态电性进行了研究,直观展示了沟槽结构对器件 BVDSS 以及 Ron影响。乔杰等人研究了沟槽深度和宽度对于 Ron和 BVDSS 的影响,通过优化结构,最后获得比导通电阻(Rsp,on)为 0.79mR·cm2,BVDSS 为 81V的器件。陈力等人研究了在不同 BVDSS 下器件Ron 优化设计差别,理论和仿真表明,高 BVDSS器件的 Ron 比低耐压器件更接近理想 Ron。

本研究设计开发了一种 100VN 中压 Trench MOSFET 器件,基于仿真和实验对器件设计开发思路进行验证,在此过程中对影响器件击穿电压,阈值电压和导通电阻的结构和工艺参数进行了拉偏研究,针对器件所表现的电性现象进行了分析,并利用仿真软件描述了微观的物理图像,以更加深刻的理解器件性能变化的机制。

2 Trench MOSFET 结构模型

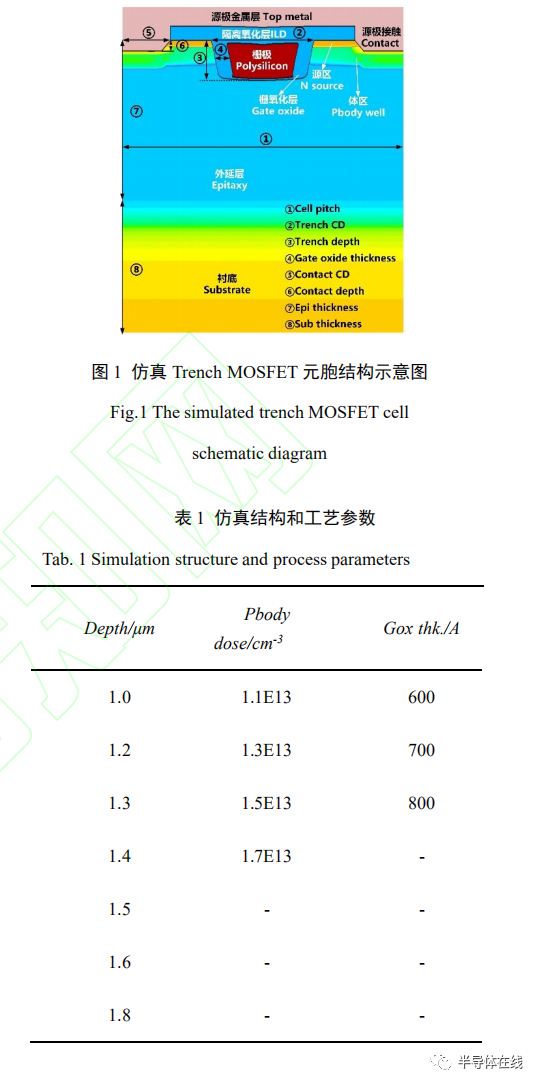

图 1 是本文研究的 Trench MOSFET 元胞结构示意图,其特点是在外延硅内部刻蚀形成沟槽结构,在体区(Pbody well)形成垂直导电沟道,进而并联更多元胞,降低导通电阻。结合图 1 对相关结构和工艺基础参数进行定义:外延层掺杂浓度3.9E15cm-3,厚度 8.3μm,元胞尺寸(cell pitch)1.4μm,沟槽深度(Trench depth)为 1.0μm~1.8μm,沟槽宽度(Trench CD)0.4μm,源极接触宽度(Contact CD)0.45μm,源极接触深度(Contactdepth)0.35μm,栅氧化层(Gate oxide,简称 Gox)厚度为 600A~800A,体区注入剂量(Pbody dose)1.1 E13~1.7E13,源区(N source)注入剂量 4.5E15。

3 结果分析

3.1 沟槽深度

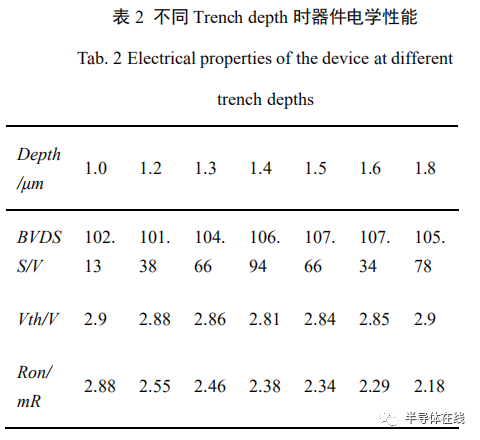

在保持其他结构和工艺参数不变情况下,Trench depth 变化会对沟槽底部电场分布和积累层电阻产生影响,从而影响到器件的 BVDSS 和 Ron。本研究设计的 Trench depth 取值依次为 1.0μm、1.2μm、1.3μm、1.4μm、1.5μm、1.6μm 和 1.8μm。如表 2 和图 2 所示,器件 BVDSS 随着深度的增加表现为先升后降的趋势,Vth 与深度的相关性不明显,变化值仅为 0.09V,Ron 与深度表现为相反数值关系。

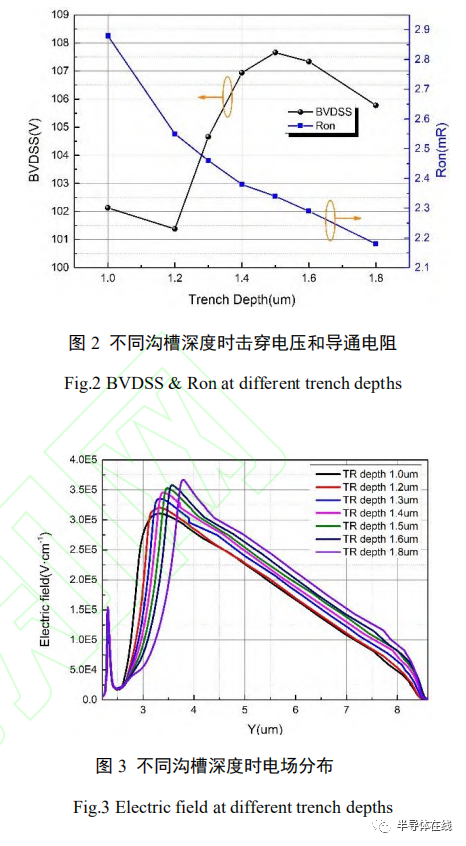

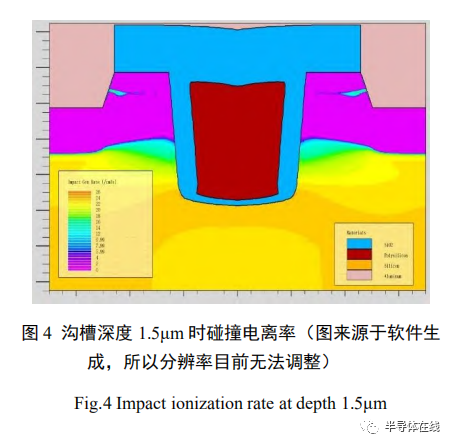

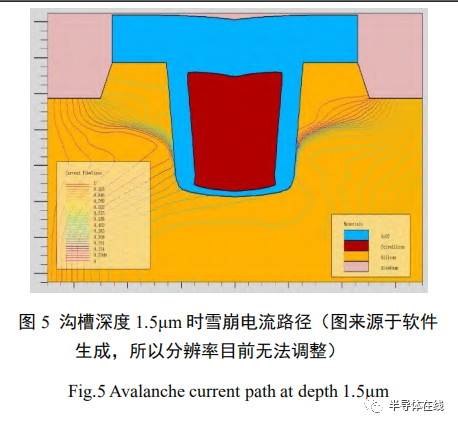

Trench depth 在 1.0μm~1.5μm 范围内,与深度保持正相关,这是因为栅极在沟槽内部具有类似于场板作用,随着深度增加,相应 BVDSS 也随之增加,并在 1.5μm 时 达 到 最 大 值 107.66V , 在1.5μm~1.8μm 范围内,随着深度进一步增加,沟槽底部挤压电力线情况变得严重,进而导致沟槽底部承受电场强度增加,达到临界场强后,引起 PN 结雪崩击穿,导致 BVDSS 降低。图 3 为器件在不同深度时电场分布,可以看出峰值电场强度随着深度增加而升高,图 4 和图 5 分别表示器件反向耐压时碰撞电离率分布和雪崩击穿时电流流通路径,可以看出碰撞电离率出现在沟槽的底部拐角处,雪崩击穿时 PN 漏电流直接沿着沟槽底角从体区流向源极接触。

Trench depth 对于 Vth 影响不明显,在深度变化 0.8μm 条件下,Vth 仅变化了 0.09V,这是因为深度变化未引起体区离子分布变化,同时 Gox 厚度也未变。在栅源电压 Vgs=10V 时 Ron 随着深度增加而降低,其主要原因是深度的增加降低了漂移区电阻,对于低压 MOSFET 而言,沟道电阻和漂移区电阻是影响器件导通电阻主要部分,本研究中体区注入条件和结构未发生变化,因此沟道电阻不变,而深度增加占用了漂移区面积,从而降低了漂移区电阻,整体表现为器件 Ron 降低。

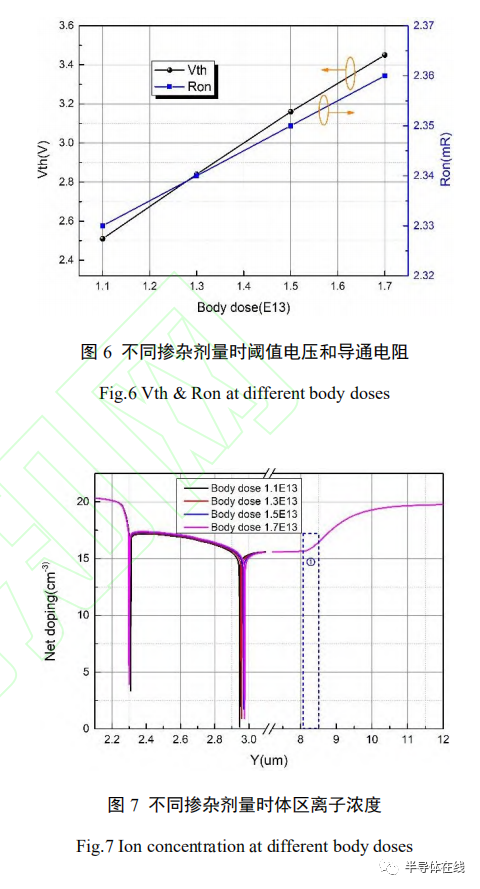

3.2 体区注入剂量

本研究设计体区注入能量固定为 60keV,注入剂量和对应电学性能如表 3 所示,从表 3 和图 6 可以看出,BVDSS 与注入剂量具有弱相关性,Vth 随着注入剂量增加而升高,原因可以根据公式 1 进行解释,Vth 主要由 Gox 厚度和 Pbody 注入剂量共同决定,且与此因素均为正相关关系。

其中,Vth 为阈值电压,tox 为栅氧化层厚度,εox为栅氧化层介电常数,εox 为硅的相对介电常数,k为玻尔兹曼常数,T 为绝对温度,ψB 为体电势,NA为体区掺杂浓度,ni为 300K 时硅本征电子浓度。 对于 Ron 影响一方面随着 Vth 的升高,在相同栅源电压 Vgs=10V 条件下,反型电荷数量降低,对应沟道电阻升高,另一方面如图 7 所示,随着注入剂量增加,对应体区结深和沟道电阻增加,也会引起 Ron的升高,图 7 中还可以看出衬底在整个器件制作过程中有近 0.5μm 的反扩,当外延厚度窗口条件不足的情况下,这种反扩容易造成 BVDSS 降低。

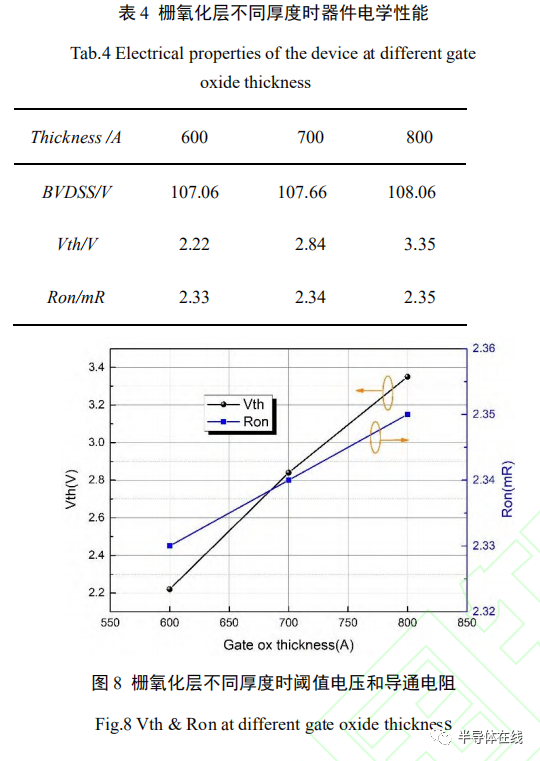

3.3 栅氧化层

通过控制 Gox 氧化时间进行其厚度调控,保持沟槽侧壁氧化层厚度分别为 600A, 700A 和 800A,从表 4 和图 8 可以看出,器件 BVDSS 随着厚度增加整体表现上升趋势,但变化幅度不大,这主要是因为器件中在反向时起到耐压作用的是体二极管,因此 Gox 厚度影响不大。但对于 Vth 而言与厚度的变化表现出强相关性,如公式 1 所示,Gox 厚度增加,需要更大的栅源电压 Vgs 来实现反型传输电荷层的形成,因此表现为 Vth 升高。对于 Ron 也随着Gox 厚度增加而表现升高趋势,但增幅比较小,其增加原因主要与 Vth 升高相关。

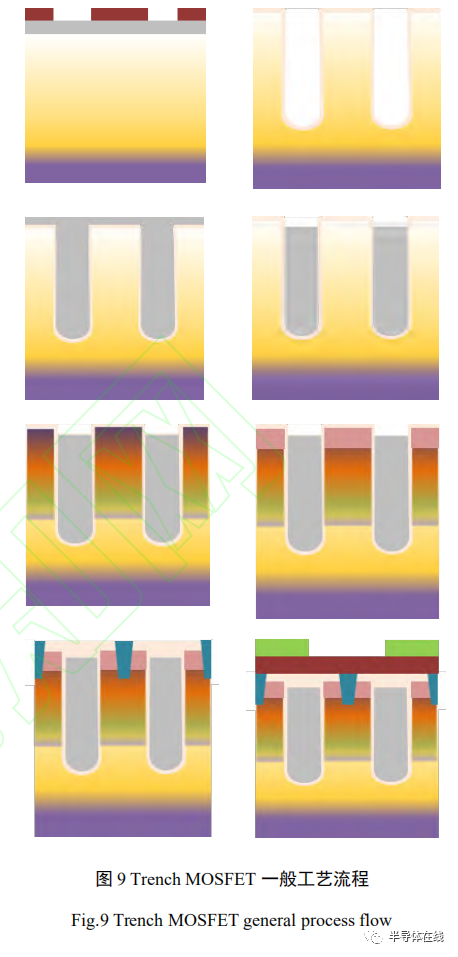

3.4 实验工艺流程

根据上述研究结果确定 Trench MOSFET 结构和工艺条件如下:Trench depth 为 1.5μm,Pbody dose为 1.3E13,Gox 厚度 700A,图 9 为所设计的器件一般工艺流程,具体包括沟槽刻蚀,栅氧化层生长,多晶硅栅极淀积和刻蚀,Pbody 体区和 Source 源区离子注入与退火,源极接触刻蚀和接触金属填充,源极金属和钝化层淀积。其中在完成沟槽刻蚀后,需要进行牺牲场氧生长和去除,以降低沟槽表面损伤和残留异物,在完成多晶硅回蚀刻后,需要进行过刻蚀,以去除平台(mesa)上可能残留的多晶硅,防止由此引起的栅源短接。

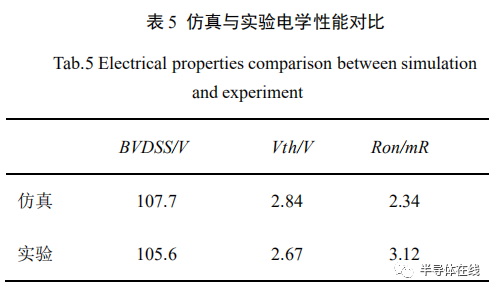

表 5 是基于实际流片获得仿真与实验电性性能对比,从图中可以看出 BVDSS,Vth,Ron 相近度分别在 98%,94%和 75%,由于 BVDSS 主要与外延厚度,浓度和体区注入条件等相关,此部分仿真过程中完全参照实验条件,因此 BVDSS 具有比较小变化。Vth 仿真中虽然在 Gox 和体区注入部分参照实验,但是实际流片中,Gox 的质量,界面缺陷,栅极多晶硅品质等均未进行定义,因此与实验相比具有 94%的相近度。而 Ron 仿真结果具有比较大变化率,是因为仿真结构模型为了提高计算速度,减少了部分层别的设置如 Ti/TiN,背面金属层等,同时在实际实验减薄和背面金属化过程中,最终厚度等条件也可能有偏移,因此表现为 Ron 结果具有较大差异。但整体上通过仿真方法获得了器件结构和工艺参数对电性影响规律,并符合物理规律,同时BVDSS 也达到了预设目标,整体上本研究仿真设计的参数对于实际的实验开发具有参考意义。

4 结束语

本 研 究 基 于 仿 真 工 具 对 100VN TrenchMOSFET 器件进行设计和研究,重点研究了沟槽深度,体区注入剂量和栅氧化层厚度对于击穿电压,阈值电压和导通电阻的影响现象并对机理进行了分析,并使用仿真工具对器件内部的物理场变化进行了描述。通过优化研究获得了器件结构和工艺参数为沟槽深度 1.5μm,体区注入剂量 1.3E13,栅氧化层厚度 700A,最后通过实际流片获得对应器件击穿电压为 105.6V,阈值电压 2.67V,导通电阻3.12mR,相对应仿真电性分别为 107.7V,2.84V 和2.34mR。以上说明基于仿真工具进行 MOSFET 器件开发的准确性,利用其描述的微观物理图像,可以更加深刻理解器件性能变化机制,同时研究过程中相关参数设计及理论分析对于同行业研究具有一定的参考价值。

编辑:黄飞

-

DK5V100R10VN 东科集成100V功率NMOS管同步整流芯片2025-07-05 498

-

领先的光子学仿真工具Ansys Lumerical功能详解2023-05-26 33801

-

RSoft光子器件工具2023.03中的新增功能:扩展超透镜设计和多物理场仿真2023-05-24 5272

-

电子元器件如何在电路仿真中进行建模?2021-04-06 3503

-

美国BANNER邦纳光电传感器PD45VN6C1002021-01-26 853

-

如何使用开放工业标准仿真源码设计射频器件建模工具的资料说明2020-09-15 607

-

EV-VN7010AJ EV-VN7010AJVN7010AJ评估板2020-05-21 750

-

EV-VN7020AJ EV-VN7020AJVN7020AJ评估板2020-05-20 724

-

VN5Exxx不可用于模拟2019-01-28 1693

-

微波射频电路仿真100例2013-09-12 2810

-

电子元器件在电路仿真中如何建模2010-04-12 13097

全部0条评论

快来发表一下你的评论吧 !