FPGA连接MIPI接口的实现方案

可编程逻辑

描述

本文主要介绍MIPI D-PHY在FPGA上的实现。

随着camera和显示技术的发展,MIPI接口在实际运用中越来越广泛,MIPI接口协议层主要包括CSI和DSI两种,其中CSI主要用于图像输入,如图像传感器等;DSI主要用于图像输出,如屏幕显示器等。随着FPGA的广泛使用,实际应用中,经常会用到FPGA来连接各种camera模组进行图像采集输入,以及通过各种显示接口来进行图像的显示,这就要求FPGA端有CSI或者DSI接口,下面就针对FPGA端的MIPI接口实现方式进行简单的介绍。

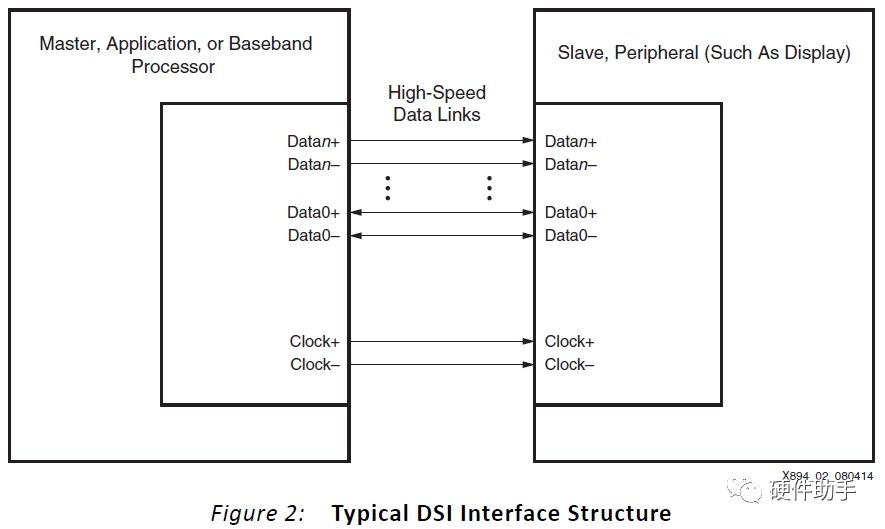

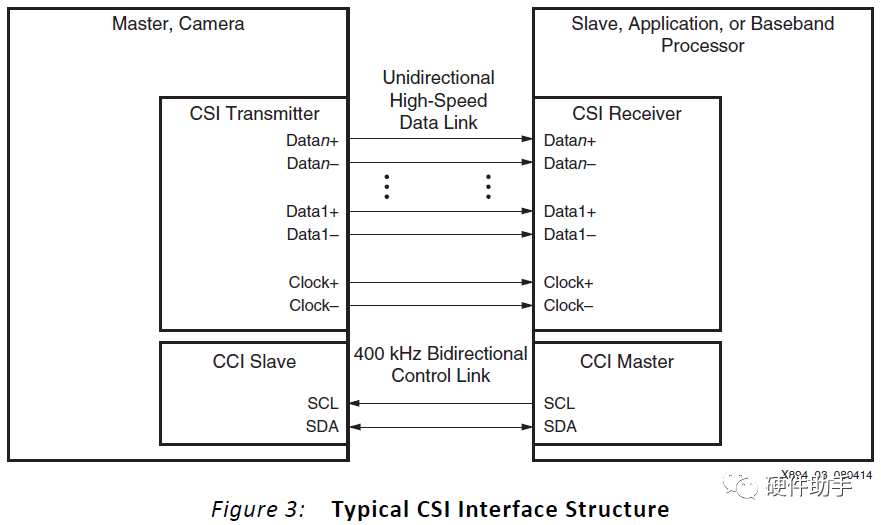

1、CSI/DSI接口

常见的CSI和DSI接口如下图所示:

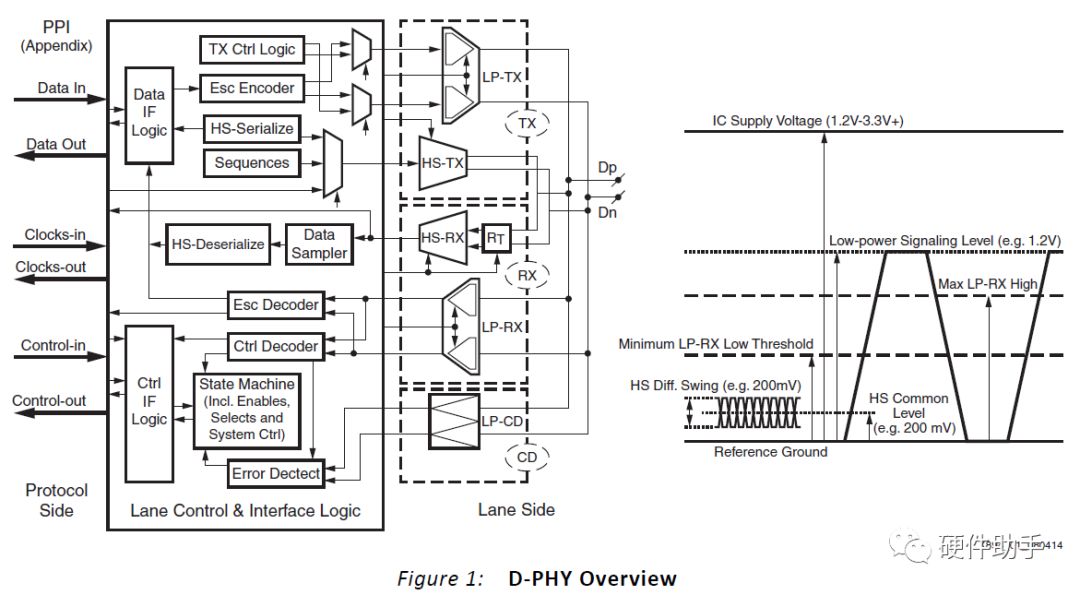

2、D-PHY

CSI和DSI的物理层常见的是D-PHY(也有兼容C-PHY的),下图是D-PHY的结构:

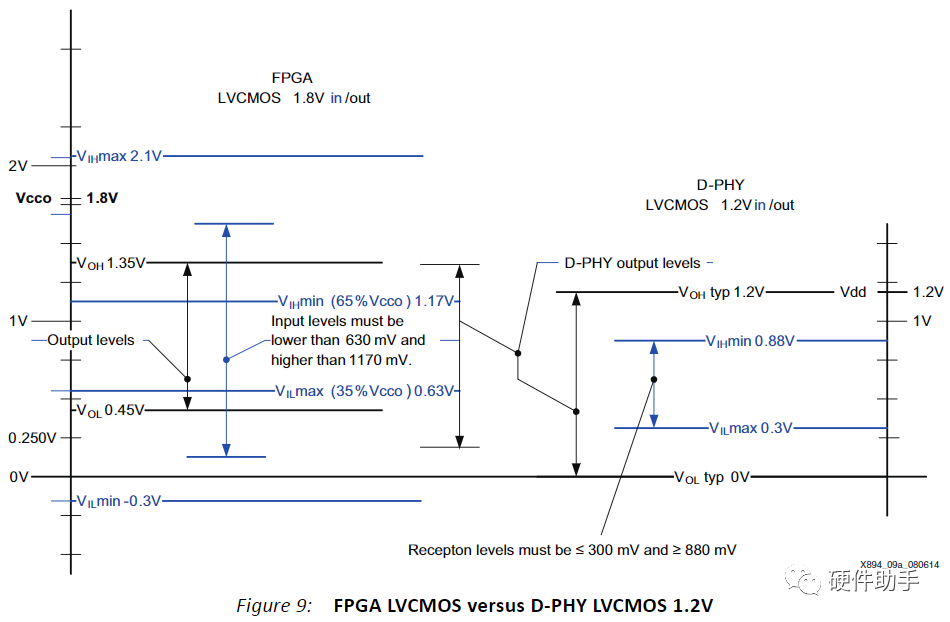

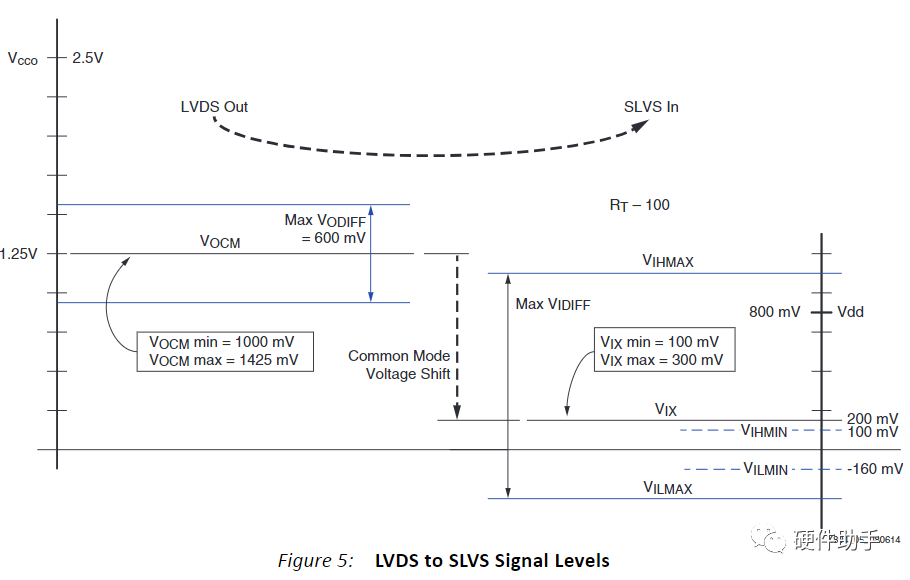

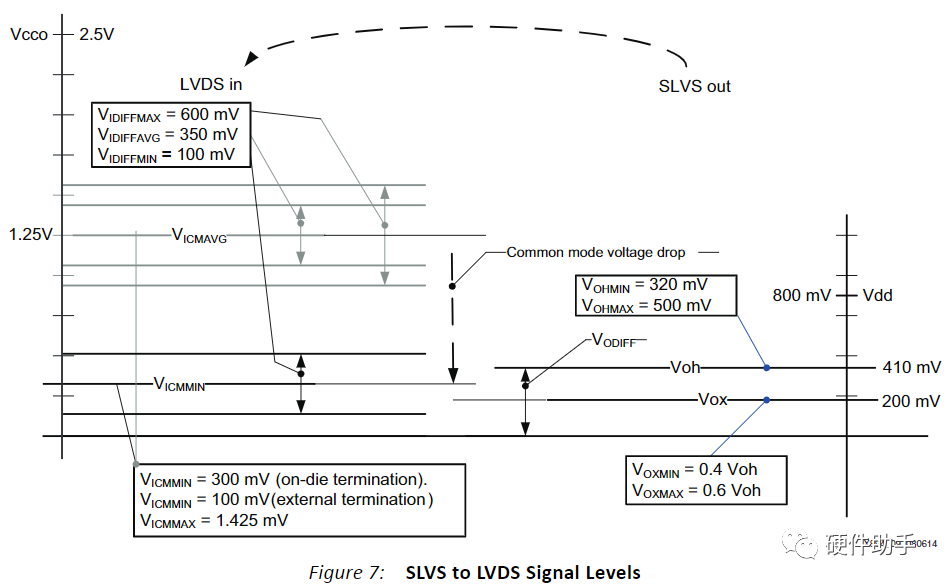

D-PHY支持HS(High Speed)和LP(Low Power)两种工作模式。HS模式下采用低压差分信号(SLVS电平),功耗较大,但是可以传输很高的数据速率(数据速率为80M~2.5Gbps),采用源同步的传输方式,由主机(Master)设备向从机(Slave)设备提供DDR时钟;LP模式下采用单端信号(1.2V LVCMOS信号),数据速率很低(≤10Mbps),但是相应的功耗也很低,用于传输初始化控制信号。两种模式的结合保证了MIPI总线在需要传输大量图像数据时可以高速传输,而在不需要大数据量传输时又能够减少功耗。

在LP模式下,只用lane0实现双向数据传输,时钟是使用数据Dp和Dn的EXOR恢复的。

3、FPGA实现方式

针对D-PHY的FPGA实现,主要有以下几种方式:

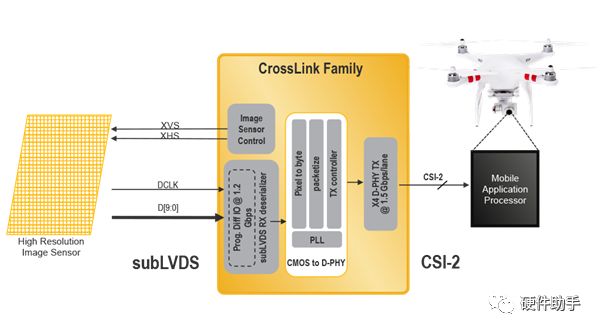

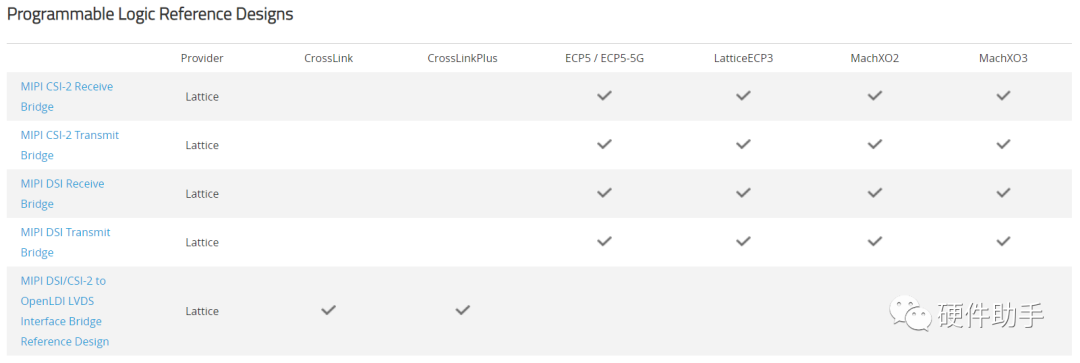

直接采用支持D-PHY的FPGA芯片(Xilinx的ultrascale系列、ultrascale+系列、Lattice的Crosslink系列)

采用电平转换电阻网络转换后使用(收发分别采用不同的电阻网络)

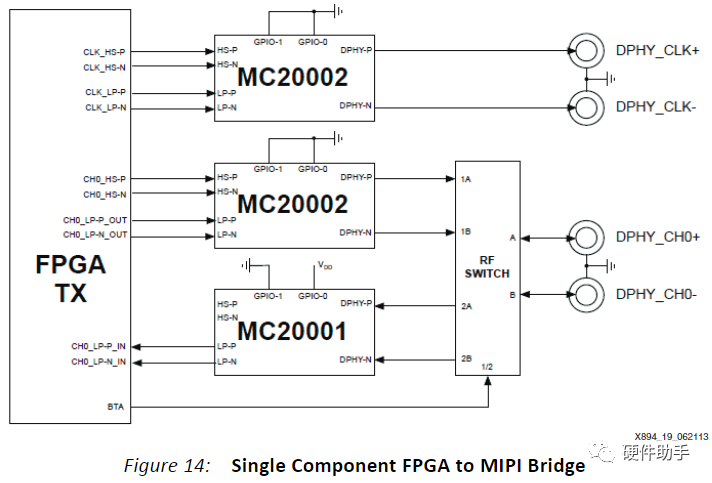

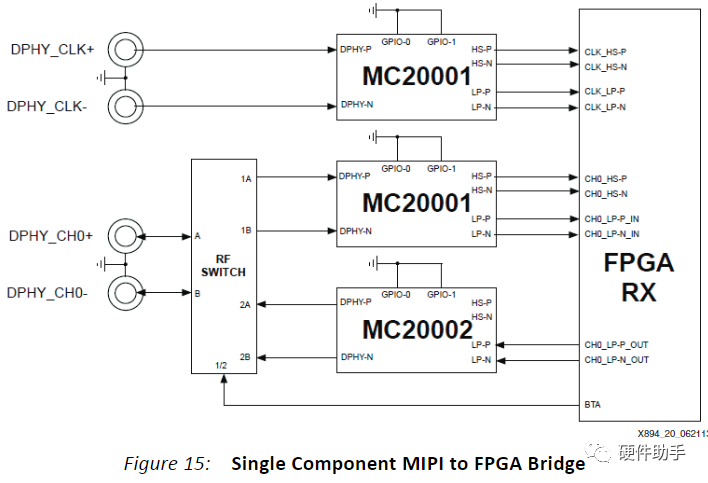

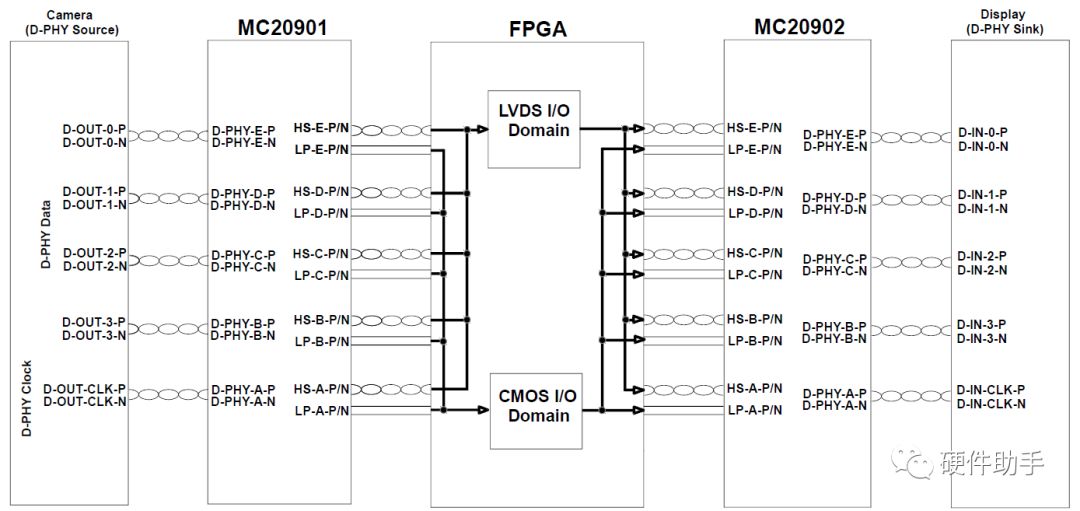

采用专用芯片进行转换(meticom、晶门、龙迅、东芝等公司均有该类转换芯片)

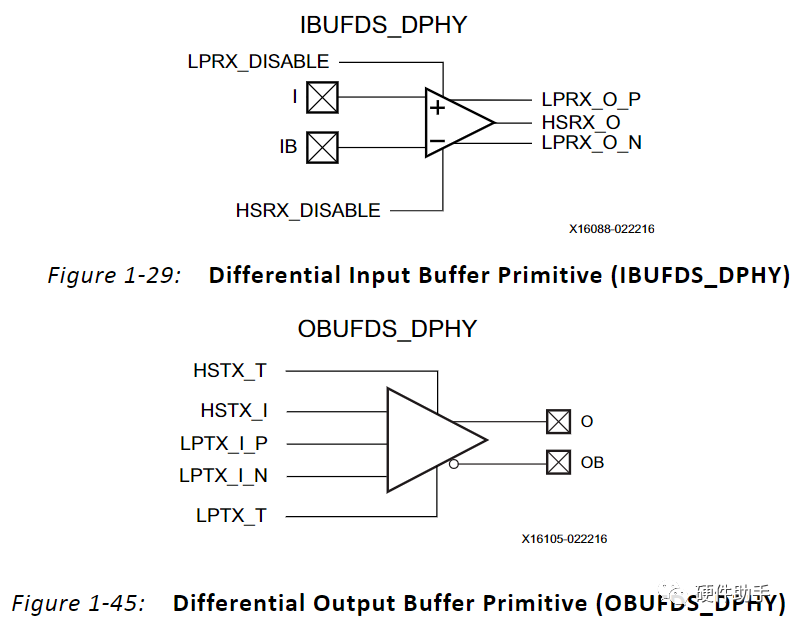

3.1、FPGA自带D-PHY

Xilinx的ultrascale系列、ultrascale+系列的HP I/O banks就自带D-PHY。

Lattice的CrossLink和CrossLinkPlus系列就自带MIPI接口。

3.2、采用电阻匹配网络转换

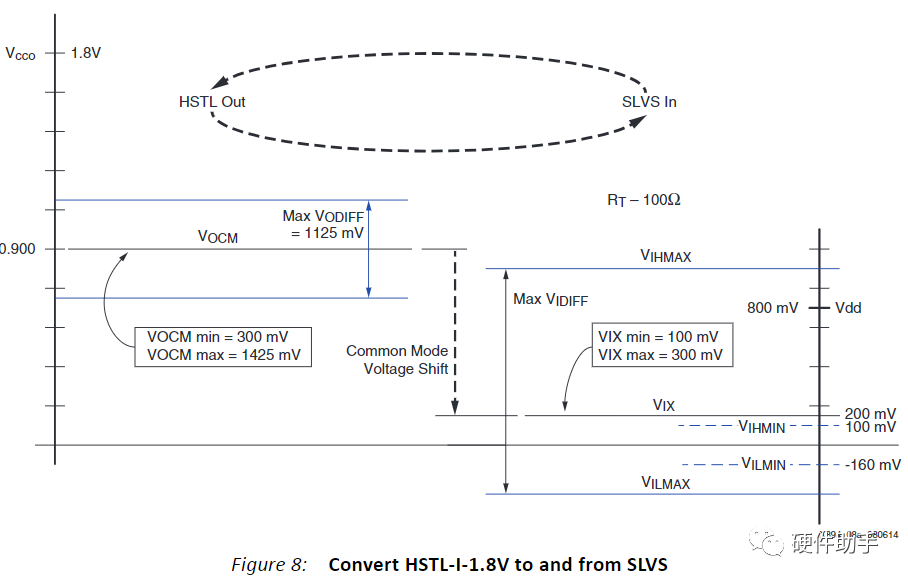

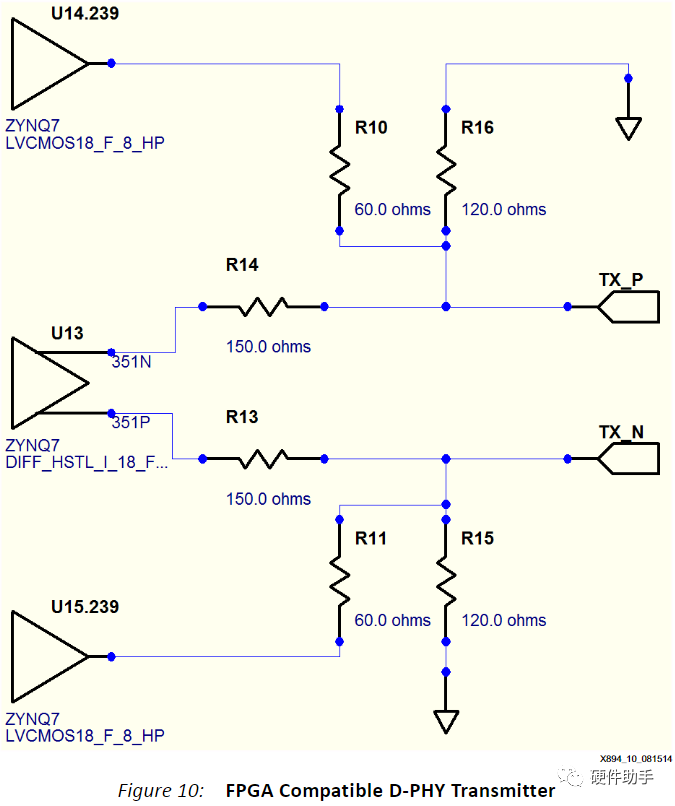

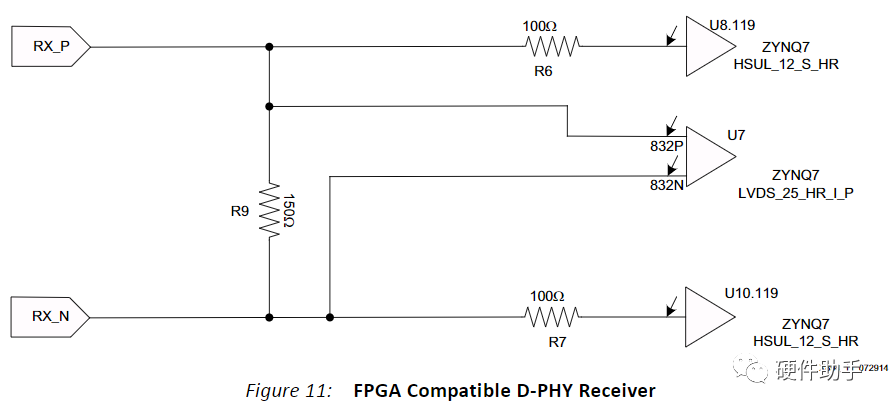

Xilinx的FPGA可以通过简单的电阻匹配网络来实现CSI/DSI接口和FPGA对接,主要是从SLVS电平的特性出发,7系列FPGA的LVDS、HSTL、LVCMOS_18、HSUL_12等电平的输入都可以直接兼容到1.8V IO bank,因此可以通过简单的转换实现SLVS电平直接对接7系列FPGA。

鉴于以上特性,将接收和发送分开进行匹配如下:

3.3、专用芯片转换

专用转换芯片有各种各样的,有的单通道的,有的四通道的,具体厂家和型号可根据实际应用进行选择,国外的有meticom、东芝等,国产的有晶门、龙迅、集创等厂家。

以上就是针对FPGA连接MIPI接口的实现方案简介,实际应用中可以根据性价比、实现难度等多方面考虑。

审核编辑:汤梓红

-

基于Xilinx FPGA实现MIPI DPHY接口案例分析2021-01-28 18996

-

Xilinx FPGA MIPI 接口简单说明2023-04-24 8304

-

请问是否有MIPI CSI-2解决方案可了解FPGA?2019-07-18 3766

-

基于FPGA的MIPI接口匹配方案2022-09-28 1821

-

基于赛灵思FPGA的低成本MIPI接口IP2017-02-10 17675

-

mipi是什么接口_mipi接口定义详解2017-12-26 167022

-

MIPI和Xilinx MIPI解决方案的介绍2018-11-27 12834

-

手机摄像头的MIPI接口如何通过FPGA采集2019-12-19 3351

-

基于FPGA的USB 3.0视频桥接解决方案及MIPI DSI连接方案的介绍2020-01-16 11648

-

基于高云半导体FPGA的MIPI接口匹配方案2022-09-14 901

-

FPGA项目承接案例:基于FPGA的MIPI接口开发服务2022-11-21 1377

-

Xilinx FPGA MIPI接口简单说明2023-04-19 6621

-

mipi接口和edp接口可以转换吗?2024-07-15 6094

-

mipi显示器接口多少引脚2024-07-16 7250

-

如何在智多晶FPGA上使用MIPI接口2025-09-11 1504

全部0条评论

快来发表一下你的评论吧 !