安装FPGA开发环境的步骤

可编程逻辑

描述

第一篇 基础篇

3.1安装FPGA开发环境

3.1.1 安装高云云源软件

用户可直接在高云官方网站的开发者专区下载最新版本的云源软件GOWIN FPGA Designer,云源软件有支持Windows和Linux两种系统的版本。网站可下载教育版和全功能版,教育版不需要License即可使用,全功能版需在官网申请License方可使用。

申请License时需要填写用户电脑的MAC地址,即一个Licence只能用于一台电脑使用。全功能版与教育版的主要区别在于支持的器件型号不同,教育版仅支持较小规模的器件,全功能版支持高云的所有PFGA器件。

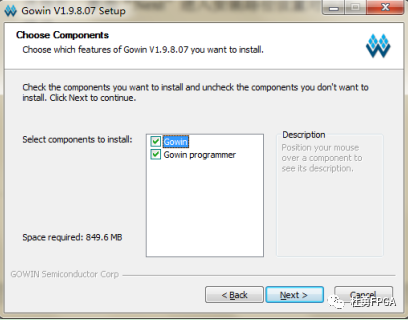

双击高云云源软件安装程序,在打开的界面中依次单击“Next”、“IAgree”按键,进入到软件安装组件选择对话框,如图3-1所示。

图3-1 云源软件安装组件选择界面

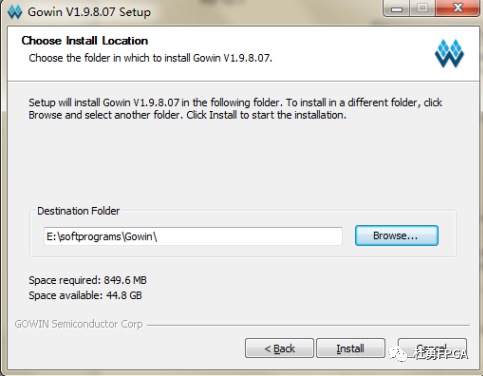

图3-1中的组件主要包括Gowin开发环境和程序下载组件Gowin programmer,默认全选择可,单击“Next”进入安装路径设置对话框,如图3-2所示。用户可以选择软件安装的路径。

图3-2 云源软件安装路径设置界面

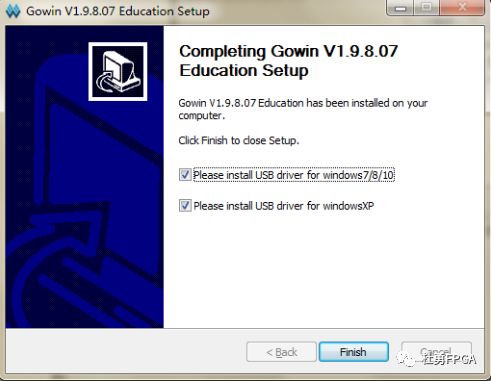

单击“Install”即可开始软件安装。由于云源软件的功能比较简单,软件安装十分迅速。完成Gowin和Gowin programmer组件后,自动弹出USB转JTAG驱动安装界面,如图3-3所示。

图3-3 云源软件USB转JTAG驱动安装界面

云源软件集成了USB转JTAG(边界扫描)驱动,便于通过USB接口完成FPGA程序的下载功能,使用非常方便。

依次单击“Next”,即可顺利完成FTDI公司的USB转串口芯片FT232HQ的驱动安装。本书配套开发板CGD100上集成了由FT232HQ做转接的USB转JTAG下载的电路模块。

3.1.2 安装ModelSim软件

Mentor公司的ModelSim是业界最优秀的HDL语言仿真软件,它能提供友好的仿真环境,是业界唯一的单内核支持VHDL和Verilog HDL混合仿真的仿真器。ModelSim采用直接优化的编译技术、单一内核仿真技术,编译仿真速度快,编译的代码与平台无关,便于保护IP核。个性化的图形界面和用户接口,为用户加快调试进程提供了强有力的手段,是FPGA的首选仿真软件。

ModelSim可以独立完成HDL代码的仿真测试。AMD、Intel这两家公司的FPGA开发环境本身自带了HDL仿真工具,同时也提供了与ModelSim软件的功能接口,可以将ModelSim软件嵌入到公司的FPGA开发环境中。

云源软件本身没有自带的HDL仿真工具,也没有提供ModelSim的功能接口,因此只能独立运行ModelSim软件完成HDL仿真。同时,ModelSim可以编译高云FPGA的IP核,完成IP核的仿真库编译后,即可利用ModelSim完整仿真包含高云FPGA IP核的HDL文件,应用起来也十分方便。

接下来首先介绍ModelSim软件安装步骤。

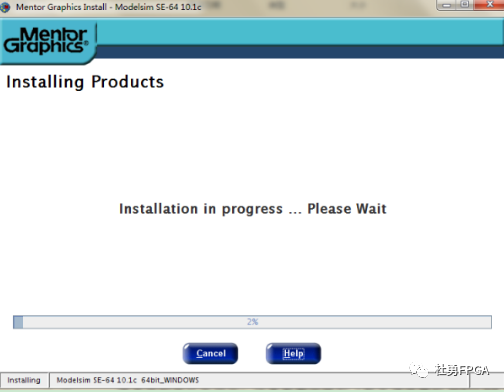

双击ModelSim安装程序文件后打开软件安装界面,单击“Next”进入安装路径设置界面,设置好安装路径后依次单击“Next”、“Agree”进入安装界面,如图3-4所示。

图3-4 ModelSim安装过程界面

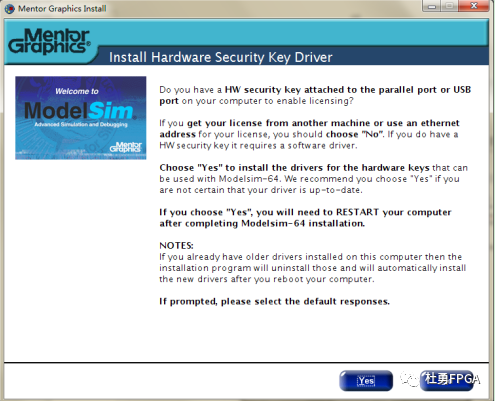

在图3-4所示的界面安装完成后,弹出硬件安全密钥驱动器(Hardware Security Key Driver)安装界面,单击“Yes”完成安装即可,如图3-5所示。硬件安全密钥驱动器实际上是安装ModelSim软件的License文件的工具。

图3-5 硬件安全密钥驱动器安装界面

如果HDL文件中不包括任何IP核,则可直接使用ModelSim进行仿真;如果HDL文件中包含了例化的IP核,由于ModelSim是第三方软件,本身没有集成高云FPGA的IP核信息,因此需要在ModelSim中完成高云FPGA的IP核编译,才能进行仿真。

首先在ModelSim安装目录下新建“gowingw1n”文件夹,用于存放编译后的小蜜蜂系列FPGA器件(本书配套开发板的FPGA芯片为小蜜蜂家族的GW1N-UV4LQ144)。

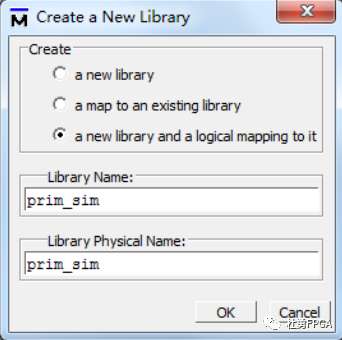

建好文件夹后,打开ModelSim软件,依次单击菜单“File→Change Directory...”打开修改目录对话框,将当前目录修改为新建的“gowingw1n”路径。依次单击“File→New→Library...”打开新建库对话框,将库名称(Library Name)修改为prim_sim,如图3-6所示。

图3-6 新建IP仿真库编译界面

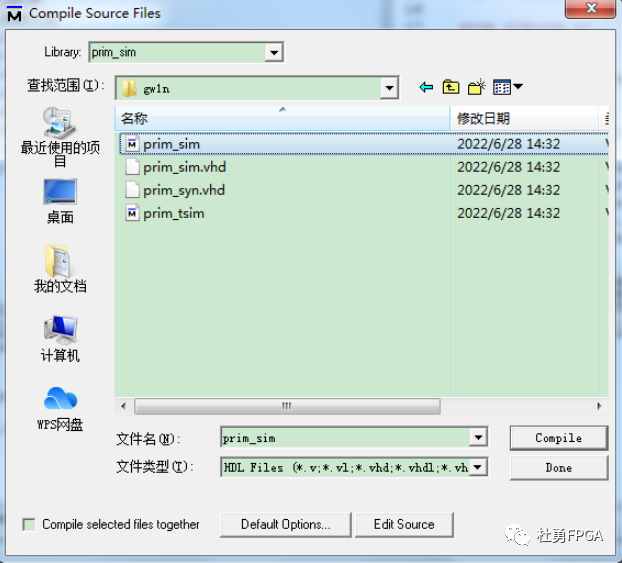

单击“OK”完成仿真库的建立。依次单击“Compile→Compile”打开编译源文件界面,在设置界面中选择“Library”为“prim_sim”,将文件路径设置为云源软件安装目录下的“IDEsimlibgowinprim_sim.v”,单击“Compile”即可完成高云小蜜蜂家族FPGA器件的IP库编译,如图3-7所示。

图3-7 编译源文件设置界面

3.2 开发平台CGD100简介

CGD100是专为本书设计的一块低成本入门级FPGA开发板。本书中的实例主要涉及到按键、LED灯、数码管、蜂鸣器、串口通信接口,CGD100具备这些功能接口。书中绝大多数实例均可在该开发板上验证。由于本书的实例较为简单,对芯片的逻辑资源需求量较少,读者也可以选购其他具备类似接口的FPGA开发板完成本书的实验。

在其他开发板完成本书实验时,只需修改工程中的目标FPGA器件型号,并根据开发板用户手册修改程序顶层端口信号对应的管脚约束即可。如果读者采用其它公司的FPGA器件为开发平台,对于涉及到IP核的程序实例时,需要在对应的开发环境中重新生成所需功能的IP核。

CGD100外观尺寸为90 mm60 mm,精心设计的电路板结构紧凑、布局美观且具备良好的工作稳定性。综合考虑工程实例对逻辑资源的需求,以及产品价格等因素,CGD100开发板采用高云的小蜜蜂家族FPGA系列GW1N-UV4LQ144为主芯片。

芯片包含4608个4输入LUT4、3456个触发器(FF)、180kbit的块状存储器(SSRAM)、256kbit的用户闪存、16个18比特位宽的乘法器(Multiplier)、2个时钟锁相环(PLL)和125个用户IO。

CGD100主要有以下特点及功能接口。

l ) 采用高云小蜜蜂家族FPGA系列的GW1N-UV4LQ144为主芯片,丰富的资源可胜任FPGA入门实例项目设计;

2) 256kbit的闪存资源,有足够的空间存储FPGA配置程序;

3) 集成了下载电路模块,只需一根USB线即可完成FPGA程序下载及调试;

4) 50MHz外部晶振;

5)独立的USB转串口接口,便于完成串口通信等功能电路;

6) 4个共阴极8段数码管,便于完成数字时钟等功能电路;

7) 1个无源蜂鸣器,便于完成电子琴等功能电路;

8) 8个独立按键;

9) 8个单色LED灯;

10) 4个三色LED灯(红、黄、绿);

l1) 4位拔码开关;

l2) 80针扩展接口,扩展输出独立的FPGA用户引脚。

审核编辑:刘清

-

乾芯DSP开发环境之IDE安装使用入门2025-12-29 1867

-

【蓝桥杯单片机】第二章 开发环境与工具的安装2024-10-30 2078

-

php运行环境的配置步骤2023-12-04 1981

-

如何在Arduino IDE中安装ESP32开发环境2023-07-13 24307

-

基于Windows系统的SpinalHDL开发环境搭建步骤2022-10-24 2664

-

IntelliJ Idea开发环境安装教程2022-10-17 2546

-

Jetson Orin开发套件安装开发环境的详细步骤2022-07-06 7130

-

IAR for 8051 开发环境的安装2021-12-03 1131

-

nuvoton 开发环境安装问题2021-11-30 735

-

Arduino的集成开发环境的安装和使用教程2019-12-18 2125

-

BadApple_FPGA的安装步骤2019-08-06 60484

-

e² studio开发环境之安装教程2018-07-23 5241

-

Android 开发环境搭建步骤详细图解2017-10-24 1054

-

Altera FPGA开发软件安装指南2009-07-21 757

全部0条评论

快来发表一下你的评论吧 !