如何读懂时序分析报告

描述

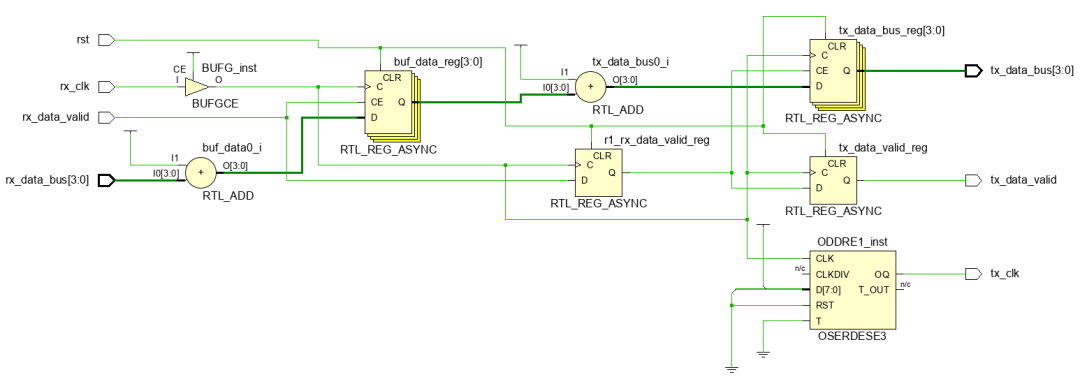

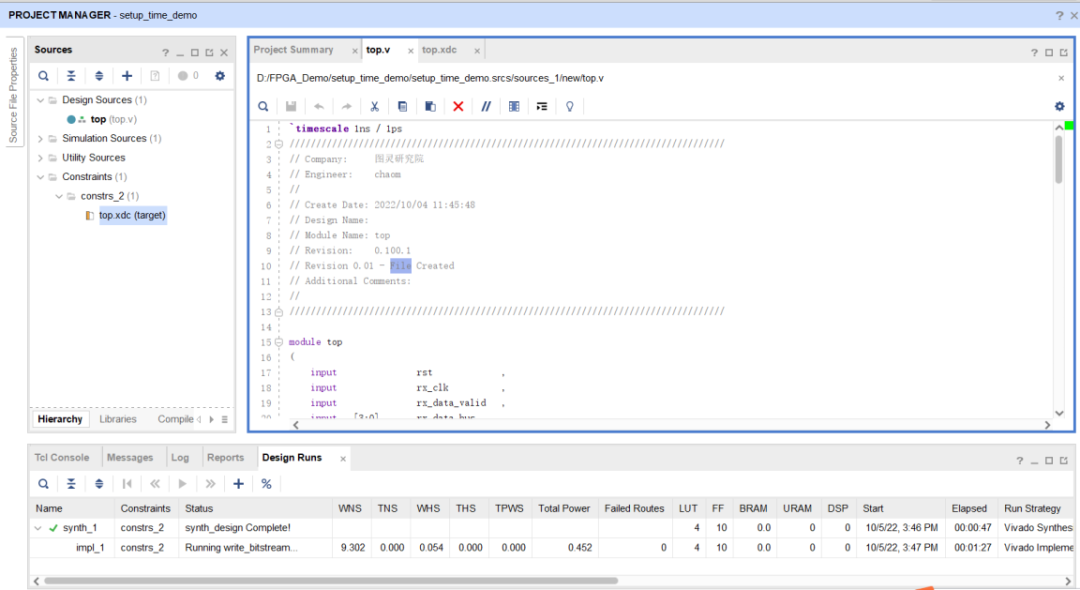

1. 前言 在上篇文章里《时序分析基本概念(一)——建立时间》,我们向大家介绍了建立时间的基本概念和计算方法。本篇文章我们将通过vivado工程实例来向大家介绍如何读懂时序分析报告。 2. vivado实例工程介绍 借用的vivado工程实例很简单,工程的电路原理框图如下图所示:  电路功能为:在rx_data_valid信号拉高的情况下,对输入的数据总线rx_data_bus数据做了两次加法,最后通过tx_data_bus管脚输出。大家可以自行下载vivado工程,具体下载方法见文章末尾。 我们对该工程进行管脚约束和时钟约束,如下图所示:

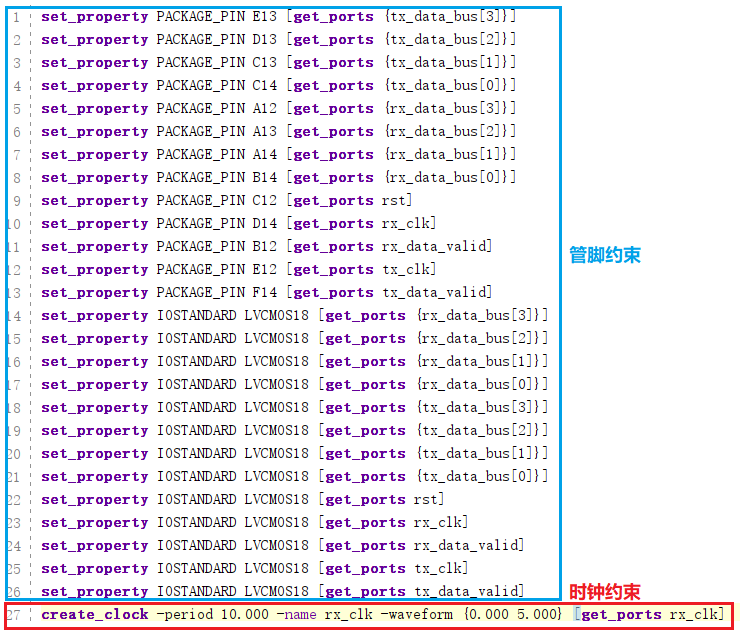

电路功能为:在rx_data_valid信号拉高的情况下,对输入的数据总线rx_data_bus数据做了两次加法,最后通过tx_data_bus管脚输出。大家可以自行下载vivado工程,具体下载方法见文章末尾。 我们对该工程进行管脚约束和时钟约束,如下图所示:  图中时钟约束的含义是告诉vivado工具,rx_clk时钟的时钟频率为100MHz。vivado软件只有在知道工作时钟频率后,才能正确的布局布线以满足该电路工作的时序要求。 3. 工程编译并打开时序报告 vivado工程编译好后,打开时序分析报告。

图中时钟约束的含义是告诉vivado工具,rx_clk时钟的时钟频率为100MHz。vivado软件只有在知道工作时钟频率后,才能正确的布局布线以满足该电路工作的时序要求。 3. 工程编译并打开时序报告 vivado工程编译好后,打开时序分析报告。  时序报告打开方法: -> 先选择“Open Implemented Design”,打开布局布线后的工程;

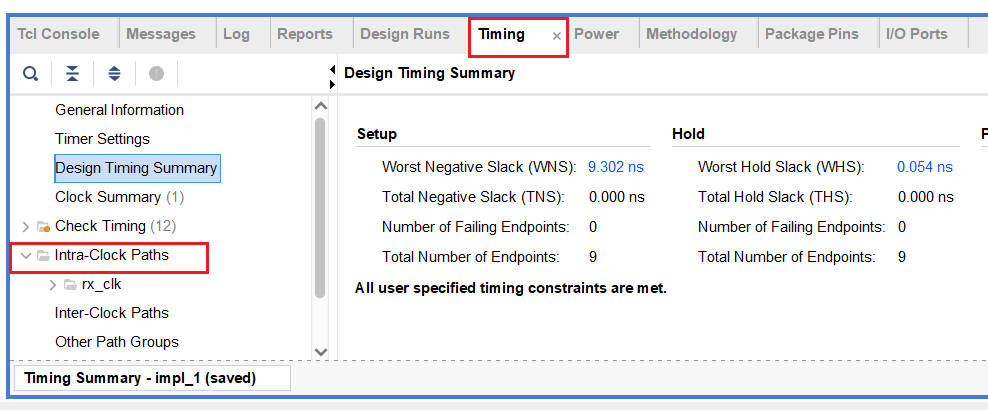

时序报告打开方法: -> 先选择“Open Implemented Design”,打开布局布线后的工程;  -> 选择“Timing”选项卡,并展开“Intra-Clock Paths”;

-> 选择“Timing”选项卡,并展开“Intra-Clock Paths”;  由于我们的工程只有rx_clk时钟域,因此我们只用展开“rx_clk”时序报告,查看“Setup”报告(建立时间报告)。

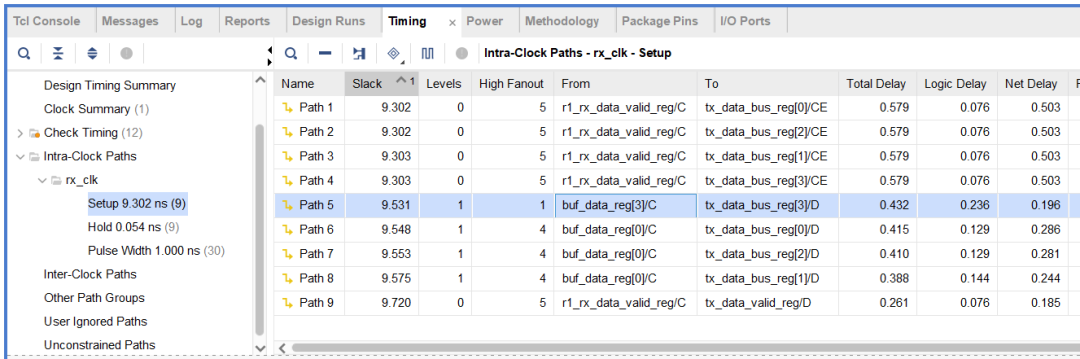

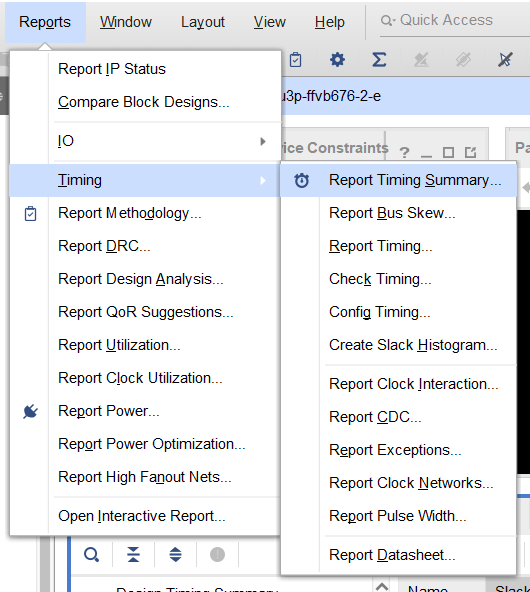

由于我们的工程只有rx_clk时钟域,因此我们只用展开“rx_clk”时序报告,查看“Setup”报告(建立时间报告)。  如果工程复杂,路径过多,该窗口默认显示的路径并不全,如果没有找到我们想查看的路径,我们可以选择菜单上的“Reports -> Timing -> Report Timing Summary”

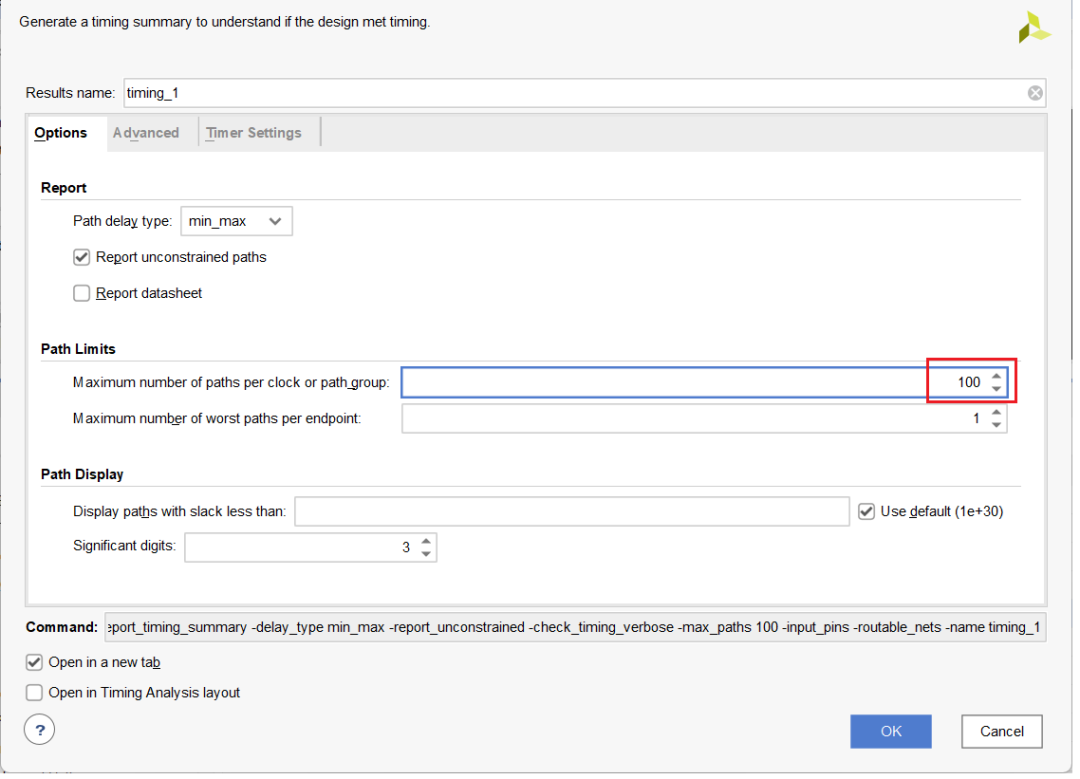

如果工程复杂,路径过多,该窗口默认显示的路径并不全,如果没有找到我们想查看的路径,我们可以选择菜单上的“Reports -> Timing -> Report Timing Summary”  修改Maximum number of paths per clock orpath_group至100(根据自己需要),点击“OK”按钮。

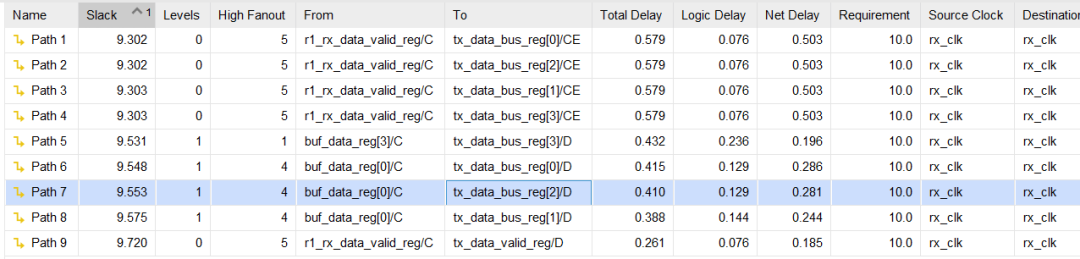

修改Maximum number of paths per clock orpath_group至100(根据自己需要),点击“OK”按钮。  4. 分析时序报告 比如图中的路径“Path7”,第一列的“Slack”指的是建立时间的松紧程度。该值为正值代表该路径的布线满足时序要求。“Levels”为1,代表数据路径上的组合逻辑为1级,“High Fanout”代表该路径的扇出为4。

4. 分析时序报告 比如图中的路径“Path7”,第一列的“Slack”指的是建立时间的松紧程度。该值为正值代表该路径的布线满足时序要求。“Levels”为1,代表数据路径上的组合逻辑为1级,“High Fanout”代表该路径的扇出为4。  双击路径“Path7”可以打开更详尽的时序报告,如下图所示。

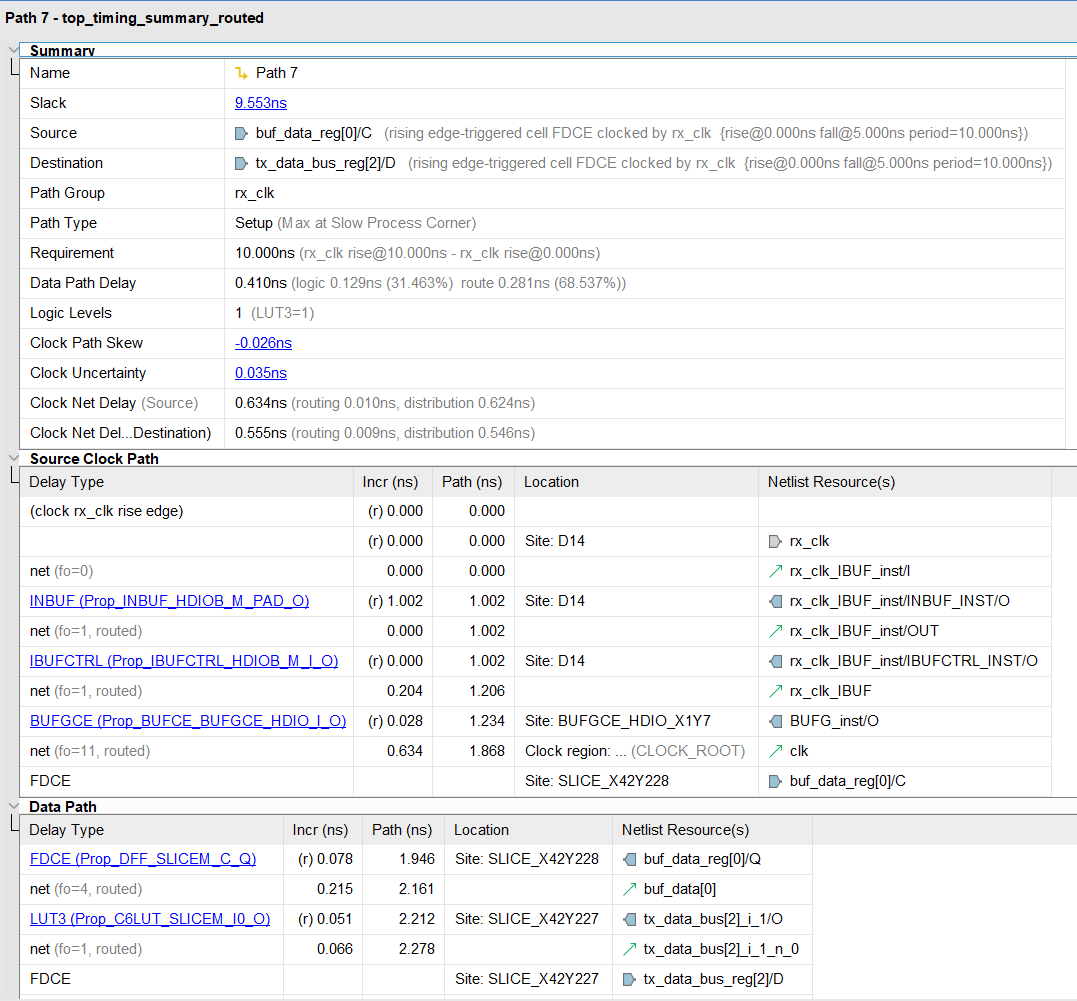

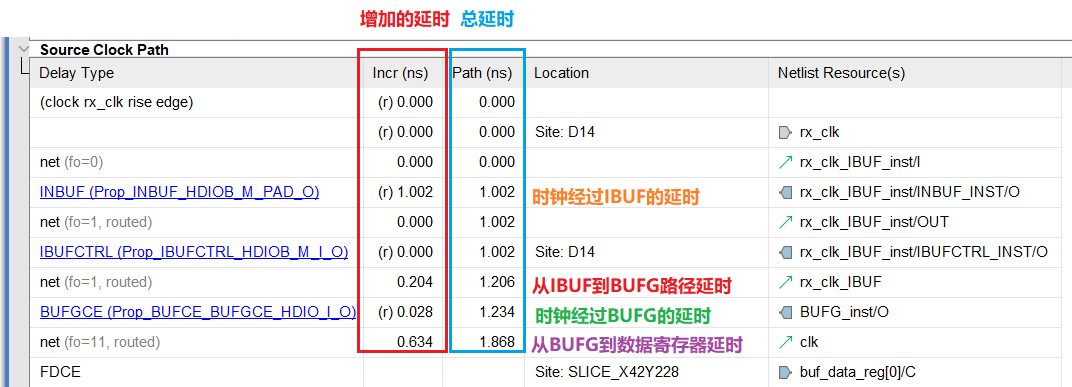

双击路径“Path7”可以打开更详尽的时序报告,如下图所示。  ① Source Clock Path 我们先来查看源时钟路径,图中用各个颜色表示了每行延时的具体含义。

① Source Clock Path 我们先来查看源时钟路径,图中用各个颜色表示了每行延时的具体含义。  根据上篇文章的学习可知,以上的延时总和为源时钟的路径延时,对应建立时间计算公式的Tclk1,即Tclk1 = 1.868ns。 我们也可以通过综合出来的电路图来更直观的查看这些路径延时的由来,打开“SYNTHESIS-> Open Synthesized Design -> Schematic”。

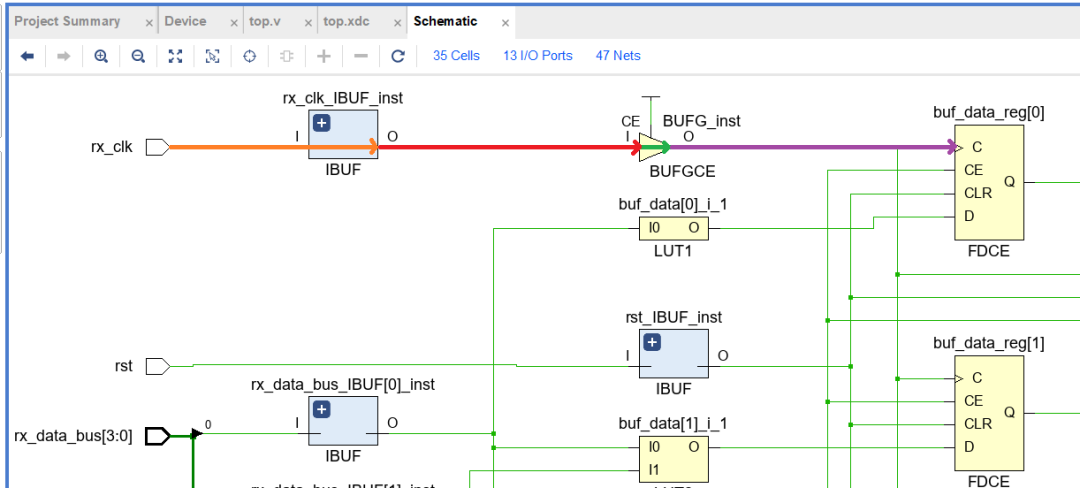

根据上篇文章的学习可知,以上的延时总和为源时钟的路径延时,对应建立时间计算公式的Tclk1,即Tclk1 = 1.868ns。 我们也可以通过综合出来的电路图来更直观的查看这些路径延时的由来,打开“SYNTHESIS-> Open Synthesized Design -> Schematic”。  图中用对应每行时序报告注释的颜色标出了对应延时路径的具体位置。 ② Data Path 我们再来看数据路径时间。数据路径时间相对简单,主要由寄存器“buf_data_reg[0]”的内部延时Tco、走线的路径延时以及组合逻辑引入的延时组成。图中用不同颜色的注释已经标注出来。

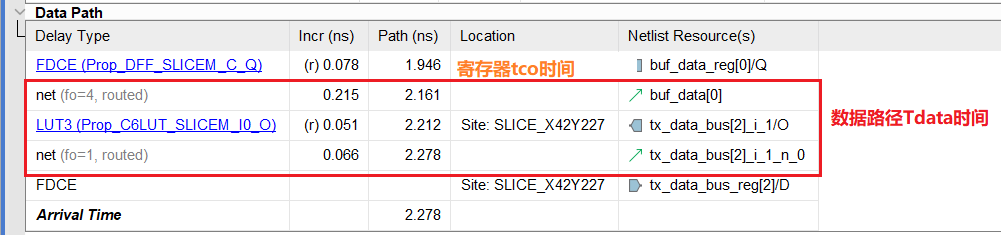

图中用对应每行时序报告注释的颜色标出了对应延时路径的具体位置。 ② Data Path 我们再来看数据路径时间。数据路径时间相对简单,主要由寄存器“buf_data_reg[0]”的内部延时Tco、走线的路径延时以及组合逻辑引入的延时组成。图中用不同颜色的注释已经标注出来。  走线的路径延时 + 组合逻辑引入的延时即为数据延时Tdata。同样的,我们通过在综合出来的电路图上,用每行时序报告注释的颜色标出了对应延时路径的具体位置。

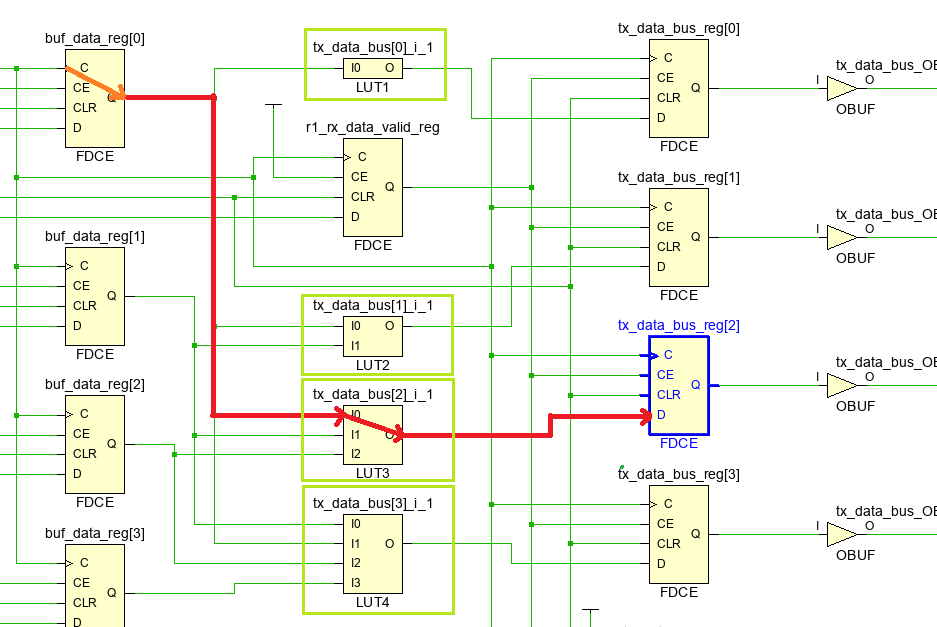

走线的路径延时 + 组合逻辑引入的延时即为数据延时Tdata。同样的,我们通过在综合出来的电路图上,用每行时序报告注释的颜色标出了对应延时路径的具体位置。  图中buf_data_reg[0]的Q端口输出分别连至4个绿色框标出的器件,因此该路径的扇出为4。由于该数据路径上,从第一个寄存器到达第二个寄存器之间只经过了1个LUT器件,因此路径上的组合逻辑为1级。 ③ Destination Clock Path 最后我们来看目的时钟路径。图中用各个颜色表示了每行延时的具体含义。

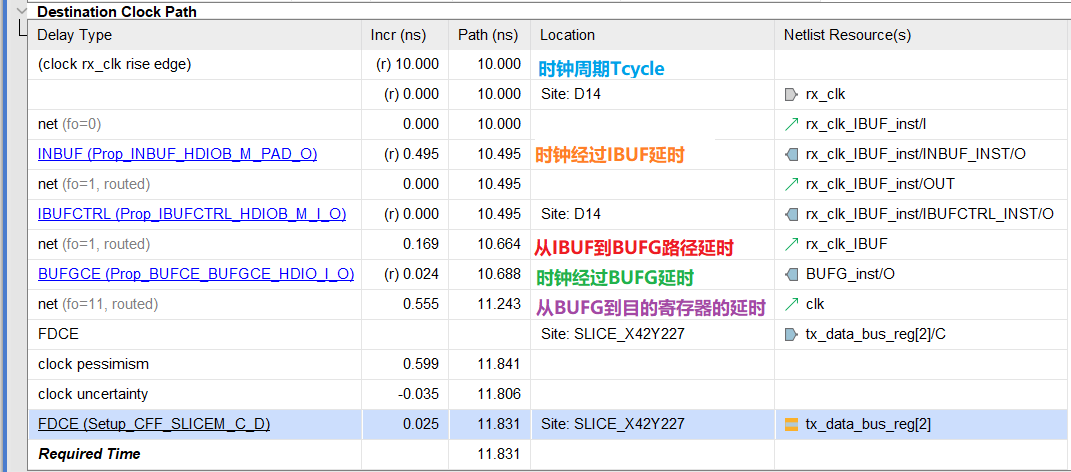

图中buf_data_reg[0]的Q端口输出分别连至4个绿色框标出的器件,因此该路径的扇出为4。由于该数据路径上,从第一个寄存器到达第二个寄存器之间只经过了1个LUT器件,因此路径上的组合逻辑为1级。 ③ Destination Clock Path 最后我们来看目的时钟路径。图中用各个颜色表示了每行延时的具体含义。  表中除掉蓝色的标注,其它所有颜色标注的延时总和为Tclk2。 表中还有“clock pessimism”时钟悲观值和“clock uncertainty”时钟抖动值,这些值的具体由来不在本文中做详述。 表中最后一项FDCE (Setup_CFF_SLICEM_C_D)为寄存器“tx_data_bus_reg”寄存器需要的建立时间值(Tsu)。 同样的,我们通过在综合出来的电路图上,用每行时序报告注释的颜色标出了对应延时路径的具体位置。

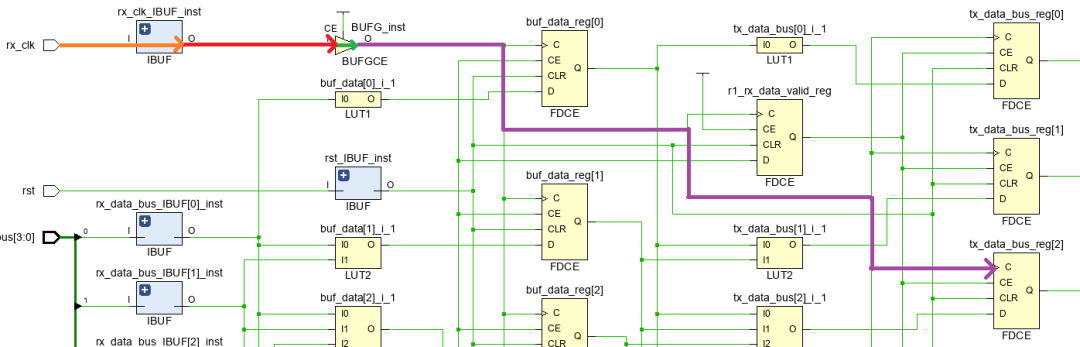

表中除掉蓝色的标注,其它所有颜色标注的延时总和为Tclk2。 表中还有“clock pessimism”时钟悲观值和“clock uncertainty”时钟抖动值,这些值的具体由来不在本文中做详述。 表中最后一项FDCE (Setup_CFF_SLICEM_C_D)为寄存器“tx_data_bus_reg”寄存器需要的建立时间值(Tsu)。 同样的,我们通过在综合出来的电路图上,用每行时序报告注释的颜色标出了对应延时路径的具体位置。  这样我们通过公式最终可计算出建立时间的slack值: slack = Tcycle + Tclk2 + Tsu - (Tclk1 + Tco +Tdata) =10 + 1.806 + 0.025 – (1.868 + 0.078 + 0.332) = 9.553ns 和时序报告计算出来的值吻合。

这样我们通过公式最终可计算出建立时间的slack值: slack = Tcycle + Tclk2 + Tsu - (Tclk1 + Tco +Tdata) =10 + 1.806 + 0.025 – (1.868 + 0.078 + 0.332) = 9.553ns 和时序报告计算出来的值吻合。

-

一图读懂爱芯元智2025年度报告2026-03-28 435

-

vivado时序分析相关经验2025-10-30 465

-

如何读懂FPGA开发过程中的Vivado时序报告?2023-06-26 2745

-

如何读懂Vivado时序报告2023-06-23 3342

-

时序分析工具对比报告2022-09-27 740

-

一文读懂什么是FPGA时序分析2021-09-18 1765

-

一文读懂时序分析与约束2021-06-15 4006

-

正点原子FPGA静态时序分析与时序约束教程2020-11-11 2918

-

如何阅读时序报告?2020-08-31 7407

-

调用timequest工具对工程时序进行分析2019-11-28 2835

-

时序基础分析2019-11-15 3664

-

FPGA实战演练逻辑篇65:CMOS摄像头接口时序设计5时序报告2015-08-19 7246

-

FPGA时序收敛学习报告2011-09-23 4083

-

时序约束与时序分析 ppt教程2010-05-17 955

全部0条评论

快来发表一下你的评论吧 !