浅谈PCB的层叠结构设计

PCB设计

描述

当把网表导入到layout软件后,需要做的事,就是叠层的设计。

以前画数字硬件板的时候,刚开始选的8层板,后来走线发现线实在走不开,最后又换成10层板。

据说有经验的layout工程师,在网表导入后,就可以估算出用几层板。

无奈,我属于没经验的兼职layout工程师,还没练成这个本事,所以只能中途返工。

除了层数的选择外,叠层结构也有讲究。

单板上的东东,笼统的讲,分为三种,即电源,地以及信号。

所以,叠层也就分为电源层,地层以及信号层。

当然还有,放置器件的层,这个一般在TOP面或者Bottom面。

而叠层的设计,就是电源层,地层以及信号层三者之间的位置关系以及距离关系。

通俗的讲,就是谁在上,谁在下,谁谁离的近一点,谁谁离的远一点。

那怎么确定三者之间的位置和距离关系呢?

先记住以下几点:

(1) 电源层和地层不得已不要分开,相邻放置,且越近越好。因为这两层之间形成的平面电容,距离越近,电容越大,对电源的滤波有好处。

(2) 电源和地平面均能作为信号的参考平面,但是呢,优先选择地平面。

(3) 元件面下面最好是地平面,为器件提供屏蔽层,为顶层布线提供参考面。

(4) 所有信号层尽可能与地平面相邻,保证信号的电流回路不会乱。

(5) 避免两信号层直接相邻,若实在没办法,走线尽量保持垂直。

(6) 还有考虑层压结构对称,要不板子容易弯曲。

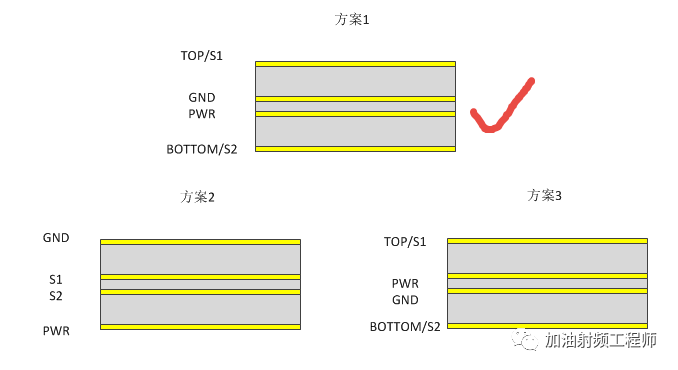

4层板的叠层结构可以有下面三种方案。

这三种方案中,优先选择方案1。

关键信号优先选TOP层,因为在TOP层下面是GND层。

射频和高速信号,走线需要为50ohm,所以叠层厚度需要考虑阻抗控制。

GND和PWR层,一般是使用芯板,使其薄点,保证平面电容的去耦效果。

方案2的目的,是想屏蔽得好一点,所以把GND层和PWR层在最外层。

但是理想丰满,现实骨感。想要在这个叠层条件下,获得好的屏蔽效果,对使用其的设计有苛刻的要求。

像我们常规的,具有很多器件的设计,就不适合使用方案2.

GND和PWR面会由于元件焊盘的影响,变得极不完整,这就导致S1和S2上的信号的回流乱乱的。同时,GND和PWR离的太远,去耦效果也大幅度下降。

方案3,和方案1类似。适用于主要器件在BOTTOM布局的情况,关键信号在BOTTOM层布线。

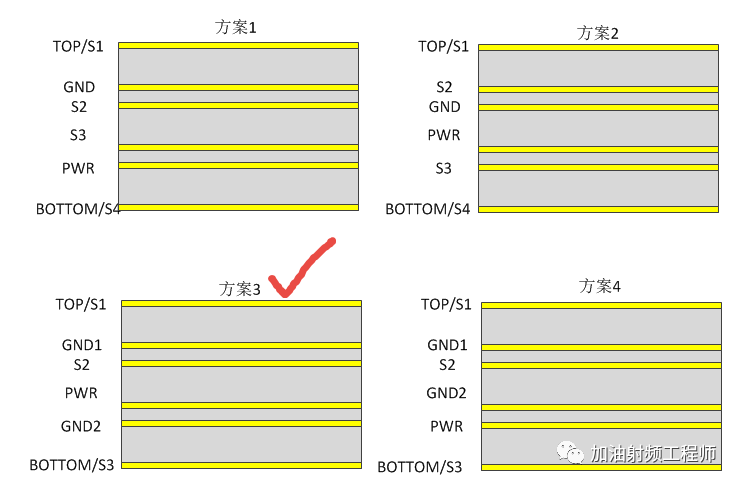

6层板的结构有下面4种方案。

六层板时,优先考虑方案3.

布线层选择依次为S2,BOTTOM,TOP。

主电源在第四层和第五层。

层厚设置上,增大S2和PWR之间的间距(减小电源对S2的影响),缩小PWR和GND2之间的间距(提升板间电容的去耦效果),缩小GND1和S2之间的间距(减小电源对S2的影响).

方案1,优选布线层TOP和S2,其次是S3和BOTTOM。不过,有时候像射频布板,没有专门的电源平面,这时候,布线层就优选TOP和BOTTOM层。

方案2,保证了电源和地平面相邻,保证了板间电容的去耦效果,但TOP,BOTTOM,S2,S3都在外面,只有S2有较好的参考平面。

方案4,适合对于少量信号有高要求的场合,因为S2上下都是GND,EMC性能最好。

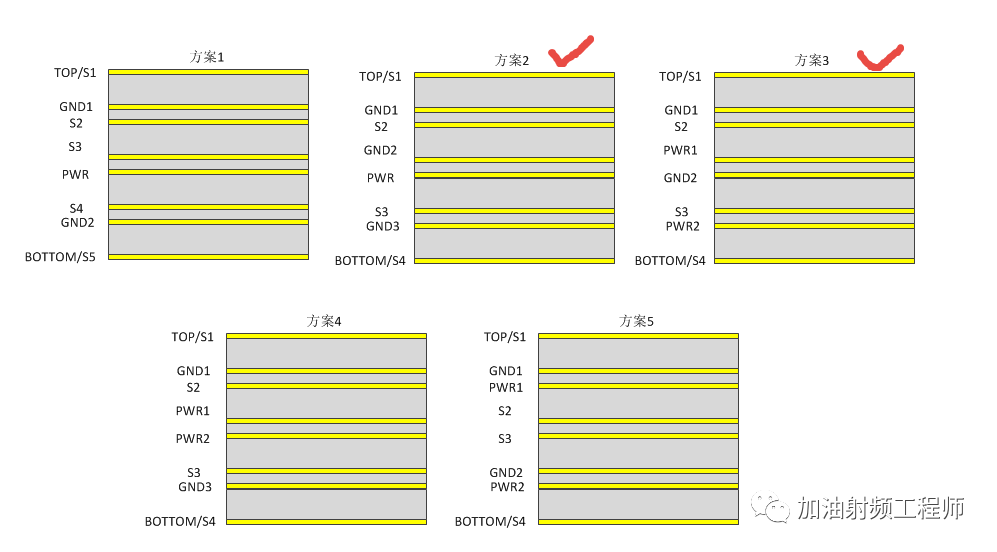

八层板的结构有下面5种方案。

优选方案2和方案3。

方案2中所有的布线层都与地平面相邻,与方案1相比,减少了相邻布线层。

方案3与方案2比,将第七层由GND更改为PWR层,所以需要减少S4上的关键布线。

方案4,无相邻布线层,层压结构对称,但是PWR离GND层远,电源平面阻抗较高。需要适当加大S2和PW1、PWR2和S3之间的距离,缩小GND1和S2、GND3和S3之间的距离。也就是说,让中间层的布线离电源层远点,离GND层近点。

方案5,电源和地平面相邻,有相邻布线层(s2,s3), S4的参考面是PWR层。如果底层关键布线少,且能控制S2和S3的线间串扰,可以考虑该方法。

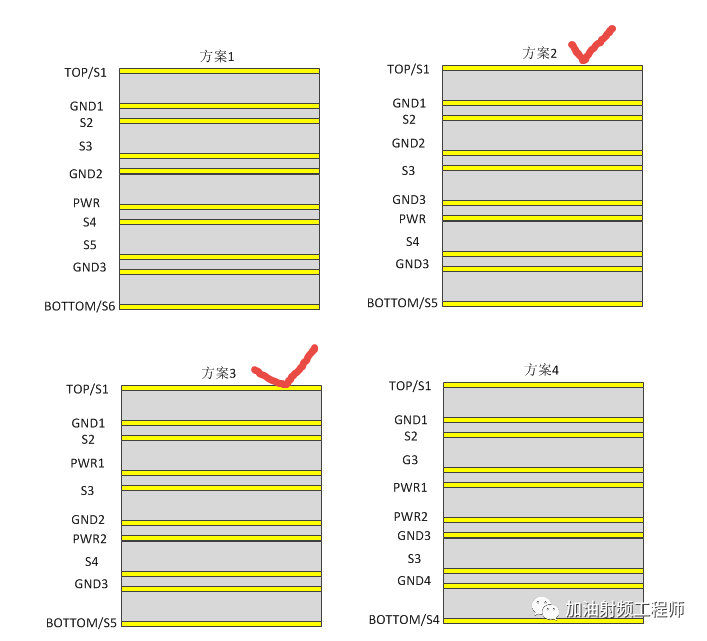

十层板的方案有如下4种。

优选方案2和方案3.

方案3, 扩大电源层与布线层的间距(S2和PWR1,PWR2和S4),缩小布线层和GND层的间距(S3和GND2,S4和GND3)。

主电源为PWR2层,其对应地为GND2层。

布线层优先选择S2,S3,S4,其次是S1和S5。

方案4:与方案3相比,少了一层布线层,但是EMC性能好。如果不考虑成本的话,优先选择这个。

参考文献:

PCB的EMC设计指南

编辑:黄飞

-

LED平板灯是如何进行结构设计的?2016-03-09 7825

-

操作系统结构设计2011-09-13 2576

-

手机结构设计心得2012-11-07 5234

-

浅谈产品结构设计特点2016-02-25 6041

-

软件结构设计2016-09-26 2610

-

PCB层叠结构设计的PCB层数预估和可生产性2019-05-22 1948

-

PCB六层板层叠结构设计方案2020-01-10 4888

-

PCB多层电路板层叠设计2020-07-23 10575

-

结构设计方面资料2010-08-09 1177

-

轴系结构设计实验2009-03-13 59350

-

浅谈面板灯结构设计及注意事项2016-12-30 6311

-

浅谈产品结构设计类别及产品结构设计的重要性2021-05-26 21455

-

PCB叠层结构设计详解2022-09-30 2935

-

FPC的结构设计.zip2023-03-01 972

-

PCB层叠结构设计的先决条件2025-06-06 1526

全部0条评论

快来发表一下你的评论吧 !