TVS Layout与系统对于ESD的防护能力探讨

电子说

描述

随着晶片先进制程的演进,晶片对于抵御外在ESD/EOS干扰的能力越来越弱,进而造成对外接口(例如:USB, HDMI, LAN等)对于ESD/EOS等能量的抗扰能力下降。为了提升系统的ESD/EOS防护效果,在各对外接口加上TVS元件已变成系统产品设计的趋势,因此以下将介绍挑选TVS元件时必须注意的参数。

AMAZINGIC晶焱科技TVS Layout与系统对于ESD的防护能力探讨

挑选适当的TVS 防护元件应注意以下参数: (1)工作电压(VRWM),确保您讯号在正常工作的情形下不被影响,因此TVS的工作电压不小于讯号的工作电压; (2)电容值,TVS元件的寄生电容值过大会造成高速讯号传输异常,因此需选择适当大小的电容值以避免讯号受到影响; (3)钳制电压,对于TVS保护元件而言,此参数格外重要,越低的钳制电压能够提供系统越好的ESD/EOS防护效果。

前面所提及TVS的钳制电压为影响防护ESD/EOS效果的重要参数,但如果在系统电路中没有合适的layout摆放TVS,即便是保护效果再好的TVS元件,当遇到ESD/EOS能量冲击时,也无法有效的发挥TVS的保护效果,最终造成系统的损坏。以下将探讨TVS Layout对于系统防护效果的影响。

针对layout方式主要提供两部份的建议:

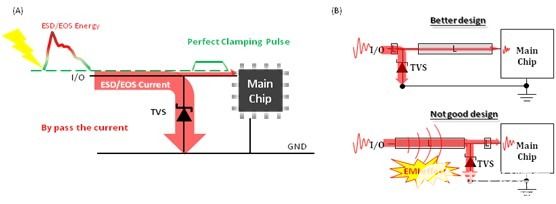

(一)TVS应尽可能靠近外部接口摆放 由图一可见,当TVS摆放位置为靠近外部接口(I/O)时,外部能量可以快速经由TVS将大多数的能量宣泄至地,此为较佳的摆放方式;但当TVS摆放位置距离外部接口较远时,外部能量有可能造成讯号的扰动,因此造成在TVS做到进行保护之前就干扰到整个系统的运作。

图一、

(A)TVS元件于线路中遭遇外部能量时的外部能量导通示意图

(B)当外部能量进入时TVS距离端口远近对于讯号干扰的差异

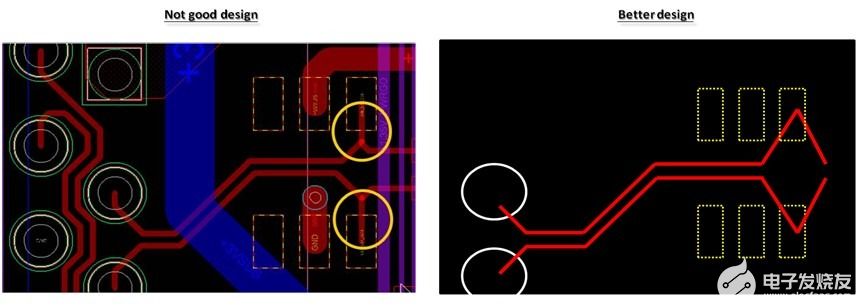

(二)TVS应避免走分支路径 当PCB布线空间狭小时,为了方便摆放TVS,有时会将讯号线另外拉线后接到TVS进行使用,如图二(左)。类似此种另加引线的布线方式将导致TVS无法达到最有效的防护效果。通常于TVS建议走线时,都建议将预保护的讯号线直接通过TVS,并且不建议使用而外拉线的方式进行使用。后续我们也以实测结果来模拟系统线路设计时,TVS的分支路径对于TVS保护效果的影响。

图二、TVS走线方式

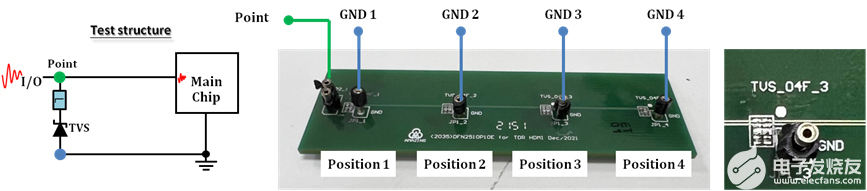

图三为实验测试板,此实验以AZ1143-04F进行测试,板子最左侧为讯号线位置,并且在讯号线上设计不同的TVS放置位置,用于模拟当TVS距离讯号不同距离时,TVS对于系统保护上所产生的变化;而板子位置上,由左至右分别为Position 1至Position 4,并透过TLP系统量测不同位置下的TVS与线路上距离所造成的钳制电压差异,以此作为TVS防护效果变化的依据。为了着重于讯号线与TVS之间的距离对于钳制电压的影响,因此在测试版设计上,将GND部分以最接近TVS元件进行设计,以降低地回路对于整体实验的影响。

图三、实验测试版

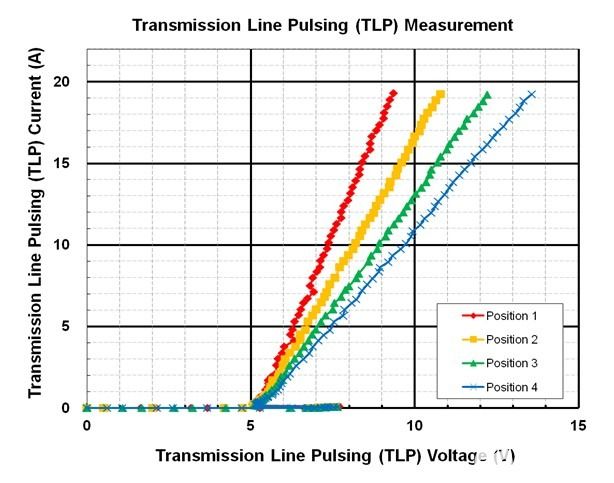

由量测TLP结果(图四)可知,在相同TLP电流16A的情况下,Position 1所量测到的钳制电压最低(8.6V),而Position 4所量测到的钳制电压最高(12.2V);随着TVS距离预保护线路越远,后端晶片所看见的钳位电压就越高,表示保护效果越差。

图四、Position 1-4利用TLP系统量测实验线路上的TVS钳制电压结果

透过以上实验可以证明,在系统电路设计时,TVS防护元件LAYOUT的方式会影响到TVS对于系统的保护效果,在进行电路保护规划时,保护元件应尽量靠近外部接口(Connector)摆放并且TVS应直接摆放于预保护之讯号上,能使TVS元件对于系统ESD/EOS的防护效果较佳化,以达到提升系统抵抗外部ESD/EOS干扰的能力。

审核编辑:汤梓红

-

TVS/ESD 静电防护指南2026-03-03 221

-

ESD与TVS的区别2023-04-14 4245

-

AN051 ESD防护器件之TVS选型和使用2023-02-23 585

-

TVS Layout对于系统防护效果的影响2022-07-20 2299

-

请问Leiditech TVS ARRAY 的ESD防护设计要点是什么?2022-01-14 1263

-

TVS管和压敏电阻ESD防护应用原理2020-09-24 2455

-

探索ESD防护器件的原理及选用2020-09-22 3152

-

【转】电路级静电防护设计技巧与ESD防护方法2019-04-23 2925

-

TVS管的ESD静电防护原理2019-01-14 3019

-

电路级静电防护设计技巧与ESD防护方法2018-10-23 2704

-

基于EMC的ESD防护设计分析2018-09-21 2423

-

浅析ESD 防护与ESD 防护器件2017-07-31 5325

-

TVS在ESD防护中的作用2014-03-31 3124

全部0条评论

快来发表一下你的评论吧 !