FPGA的配置模式

可编程逻辑

描述

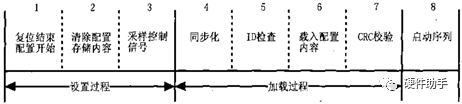

尽管FPGA的配置模式各不相同,但整个配置过程中FPGA的工作流程是一致的,分为三个部分:设置、加载、启动。

复位结束配置开始

有多种方式使FPGA的配置进入这一过程。在上电时,电压达到FPGA要求之前,FPGA的上电复位模块将使FPGA保持在复位状态;外部控制PROG_B引脚出现一个低脉冲也可以使FPGA保持在复位状态。

清除配置存储内容

这一步称为初始化,当FPGA复位结束,配置存储器的内容会被自动清除。在这个步骤中,除配置专用接口外,FPGA I/O均被置于高阻态。在整个初始化过程中,INIT_B引脚被置低并在初始化结束后恢复高电平。如果INIT_B信号在外部被拉低,FPGA将一直停留在初始化状态。注意PROG_B信号的脉宽不能太窄。

采样控制信号

初始化结束后,INIT_B信号回到高电平。FPGA开始采集模式选择引脚M[1:0]和变量选择引脚VS。如果为主动模式,FPGA很快就会给出有效的CCLK。VS信号只在主动BPI及其SPI模式中生效。此时,FPGA开始在配置时钟的上升沿对配置数据进行采样。

同步化

每一个FPGA配置数据流都有一个同步头,它是一段特殊的同步字。同步字主要用于帮助FPGA确定正确的数据位置。同步字之前的配置数据都会被FPGA忽略,也就是FPGA仅仅在同步化之后才正式开始接收配置数据。一般而言,同步字都是由0/1数目相同的二进制数组成的,如Spartan3为AA995566。

ID检查

FPGA同步化后,会自动检测配置流中的器件ID和目标器件ID是否一致。这一步确保了FPGA不会被错误的配置流误配置。

32位的ID中包含了28位的特征值和4位掩码。特征值包括厂商信息,器件族,器件规模等。当器件ID检查遇到问题时,FPGA会将内部寄存器的第一位ID_Err置高,软件也会显示错误信息。

载入配置内容

在ID检查顺利通过后,FPGA开始加载配置数据。

CRC校验

在加载数据过程中,FPGA会对每一帧数据进行CRC校验。如果失败,FPGA会将INIT_B信号拉低并终止配置过程。

启动序列

FPGA配置数据加载完后,FPGA进入启动序列。启动序列事件的默认顺序为先释放DONE引脚,然后激活I/O,最后启动写使能。实际使用中,可以通过BitGen参数对启动顺序进行设置来满足不同的需求。

| 启动序列内容 | 阶段 | BitGen选项 |

| 等待DCM锁定 | 1~6 | LCK_cycle |

| 等待DCI匹配 | 1~6 | Match_cycle |

| 启动全局写使能,允许内部时序元件翻转 | 1~6 | GWE_cycle |

| 释放IO三态,激活IO | 1~6 | GTS_cycle |

| 释放DONE引脚 | 1~6 | DONE_cycle |

审核编辑:汤梓红

-

FPGA的配置模式有哪些?具体配置过程是怎样的?2024-06-19 5380

-

FPGA配置模式和配置设计2022-12-01 2332

-

最常用的FPGA配置模式2022-09-22 5036

-

FPGA的配置模式的分类及应用分析2021-07-02 4773

-

简述烧写FPGA程序配置2021-05-11 5361

-

详解Xilinx FPGA的配置模式(Master/Slave模式,Serial/SelectMAP模式)2021-01-01 30313

-

请问哪些引脚用于通知PROM当前的配置模式吗?2020-05-27 1447

-

FPGA配置模式选择 FPGA上电加载时序介绍2020-04-06 5239

-

关于Xilinx FPGA的配置流程浅析2018-08-01 5406

-

Spartan6系列FPGA的配置模式详解(主模式/具体配置模式)2018-07-14 18709

-

关于XILINX FPGA的配置模式的问题,急急急。。。2013-10-18 3137

-

什么是FPGA?FPGA是什么意思2011-12-07 82845

-

FPGA配置模式2011-09-08 2252

全部0条评论

快来发表一下你的评论吧 !