RTL表达式和运算符

描述

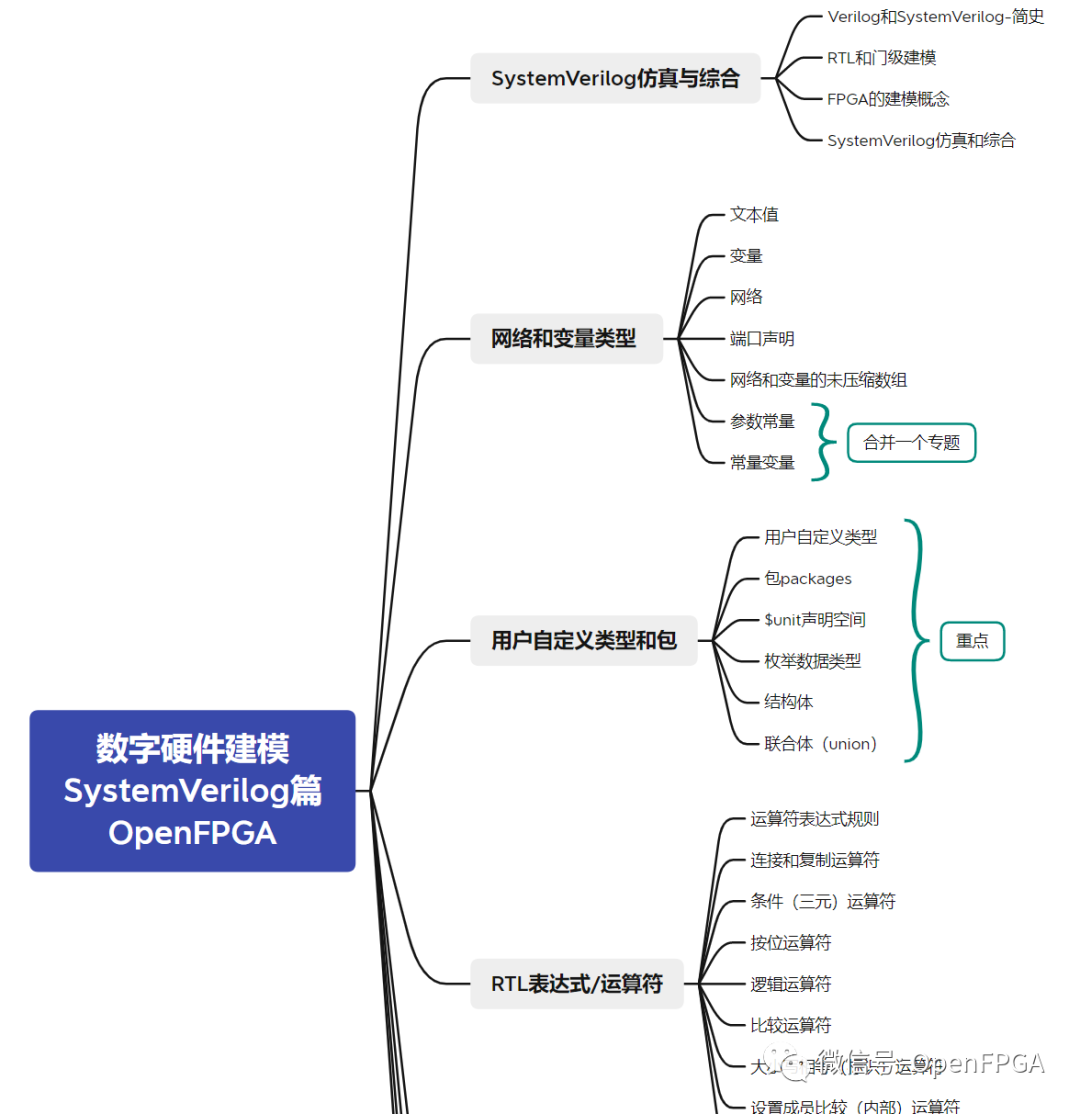

数字硬件建模SystemVerilog-归约运算符(Reduction operators)

经过几周的更新,SV核心部分用户自定义类型和包内容已更新完毕,接下来就是RTL表达式和运算符。

马上HDLBits-SystemVerilog版本也开始准备了,基本这一部分完成后就开始更新~

介绍

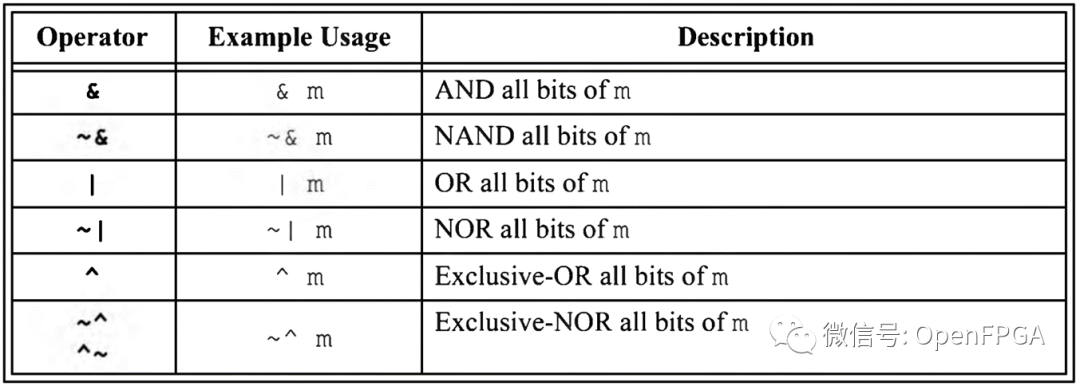

归约运算符对单个操作数的所有位执行运算,并返回标量(1位)结果。表5-9列出了归约运算符。

表5-9:RTL建模的归约运算符

表5-9:RTL建模的归约运算符

归约运算符包括一个NAND和一个NOR运算符,这是按位运算符所没有的。归约AND OR 和 XOR 运算符一次执行一位操作,从最右边的位(最低有效位)向最左边的位(最高有效位)移动。归约NAND、NOR和XNOR运算符首先分别执行归约AND、OR或XOR运算,然后反转1位结果。

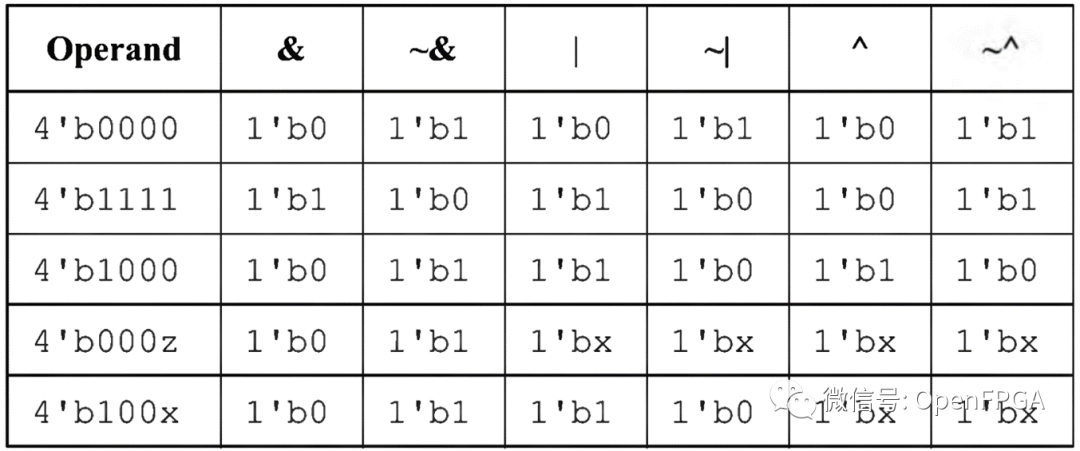

AND、NAND或NOR运算符是X-optimistic。对于归约运算符,如果操作数中的任何位为0,结果将为1’b0。对于归约NAND,如果操作数中的任何位为0,结果将为1’b1。类似地,对于归约运算符,或者如果操作数中的任何位为l,结果将为1’b1。对于归约NOR,如果操作数中的任何位为l,结果将是1’b0.归约XOR和XNOR运算符是X-pessimistic。如果操作数的任何一位是X或Z,结果将是1’bx。表5-10显示了几个示例值的每个归约运算符的结果。

表5-10:归约操作的示例结果

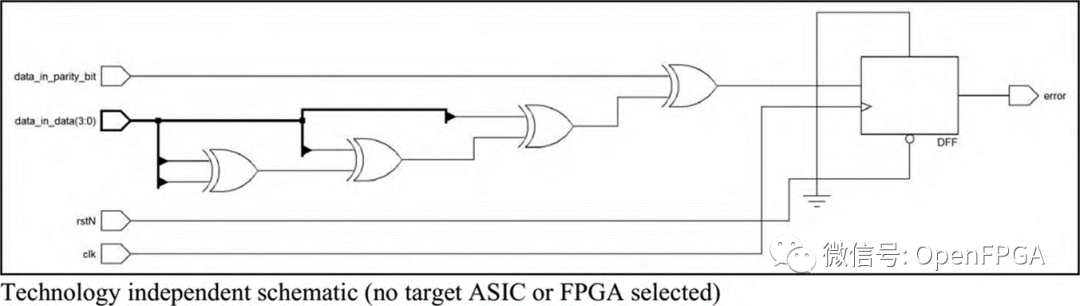

示例5-6说明了一个小型RTL模型,该模型利用归约运算符检查数据值的正确奇偶性,图5-6显示了该RTL模型综合结果。

示例5-6:使用归约运算符:使用异或的奇偶校验

//

// Book, "RTL Modeling with SystemVerilog for ASIC and FPGA Design"

// by Stuart Sutherland

//

// Parity checker using even parity, registered error flag

//

// Copyright 2016, Stuart Sutherland. All rights reserved.

//

// Version 1.0

//

//

// User-defined type definitions

//

`begin_keywords "1800-2012" // use SystemVerilog-2012 keywords

package definitions_pkg;

typedef struct {

logic [7:0] data;

logic parity_bit;

} data_t;

endpackage: definitions_pkg

`end_keywords

//

// Parity checker using even parity, registered error flag.

// The combined data value plus parity bit should always have

// an even number of bits set to 1

//

`begin_keywords "1800-2012" // use SystemVerilog-2012 keywords

module parity_checker

import definitions_pkg::*;

(input data_t data_in, // 9-bit structure input

input clk, // clock input

input rstN, // active-low asynchronous reset

output logic error // set if parity error detected

);

timeunit 1ns/1ns;

always_ff @(posedge clk, negedge rstN)

if (!rstN) error <= 0;

else error <= ^{data_in.parity_bit, data_in.data};

// reduction-XOR returns 1 if an odd number of bits are

// set in the combined data and parity_bit

endmodule: parity_checker

`end_keywords

该文件的仿真文件如下:

//

// Book, "RTL Modeling with SystemVerilog for ASIC and FPGA Design"

// by Stuart Sutherland

//

// Testbench

//

// Copyright 2016, Stuart Sutherland. All rights reserved.

//

// Version 1.0

//

`begin_keywords "1800-2012"

module test

import definitions_pkg::*;

(output logic rstN,

output data_t data_in,

input logic error,

input logic clk

);

timeunit 1ns/1ns;

// generate stimulus

initial begin

$timeformat(-9, 0, "ns", 6); // nanoseconds, no precision, 6 columns

rstN <= 0; // reset DUT (active low)

repeat(2) @(negedge clk) ; // hold reset for 2 clock cycles

rstN = 1; // remove reset

repeat (10) begin

@(negedge clk) ;

data_in.data = $urandom();

data_in.parity_bit = $urandom()%2; // randomly wrong parity value

@(negedge clk) check_results;

end

@(negedge clk) $finish;

end

// verify results

task check_results;

$write("At %t: data=%b parity_bit=%b: ", $time, data_in.data, data_in.parity_bit);

if (^data_in.data === data_in.parity_bit) begin: good_data_in

$write("Good data_in. EXPECT: error = 0, ACTUAL: %b ", error);

if (error === 1'b0) $display(" OK");

else $display(" ERROR!");

end: good_data_in

else begin: bad_data_in

$write("Bad data_in. EXPECT: error = 1, ACTUAL: %b ", error);

if (error === 1'b1) $display(" OK");

else $display(" ERROR!");

end: bad_data_in

endtask

endmodule: test

`end_keywords

`begin_keywords "1800-2012"

module top;

timeunit 1ns/1ns;

import definitions_pkg::*;

parameter WIDTH = 8;

logic clk, rstN;

data_t data_in;

logic error;

test test (.*);

parity_checker dut (.*);

initial begin

clk <= 0;

forever #5 clk = ~clk;

end

endmodule: top

`end_keywords

图5-6:示例5-6的综合结果:归约异或(奇偶校验)

审核编辑:汤梓红

-

C语言基本的算术运算符及表达式2023-03-09 2617

-

逻辑运算符与表达式2023-02-21 3601

-

运算符/表达式规则2023-02-09 2174

-

关于RTL表达式和运算符2022-09-01 2893

-

数字硬件建模SystemVerilog-按位运算符2022-08-12 3841

-

SystemVerilog-运算符/表达式规则2022-08-03 4731

-

RTL表达式和运算符2022-07-21 3109

-

基于运算符信息的数学表达式检索技术2021-04-29 980

-

C语言程序设计--运算符与表达式2010-07-14 572

-

单片机C语言教程-运算符和表达式2010-03-27 2491

全部0条评论

快来发表一下你的评论吧 !